01 發起沿和捕獲沿

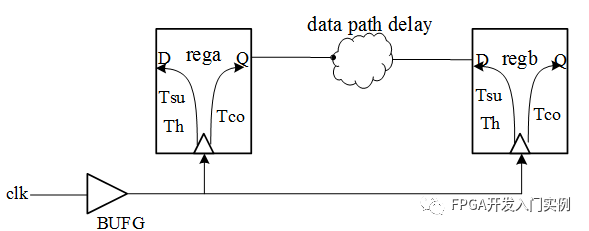

下圖是一個經典時序分析模型,無論寄存器A與寄存器B是否在同一個芯片中,下列概念均適用。

02 時序路徑

2、FPGA內部REGA時鐘端口到REGB的數據端口

3、FPGA末級寄存器的時鐘端口到器件B的輸入數據端口

4、組合邏輯路徑,FPGA輸入端口到輸出端口

1 源端時鐘路徑(紅色)

2 數據路徑(藍色)

3 目的端時鐘路徑(黃色)

03 數據到達時間與數據需求時間

在clk時刻參考時間為0的條件下,進行數據到達時間、時鐘到達時間、數據要求時間(建立時間)、數據要求時間(保持時間)的時序分析。

1.數據到達時間

數據到達時間=0+Tclka+Tco+Tdata

2.時鐘到達時間

時鐘到達時間=捕獲沿+Tclkb

捕獲沿=0+T(一個時鐘周期)

時鐘到達時間=T+Tclkb

3.數據要求時間-建立時間

數據要求到達時間=時鐘到達時間-Tsu-setupuncertainty

=T+Tclkb-Tsu-setup uncertainty

setup uncertainty:時鐘抖動造成的不確定時間。

4.數據要求時間-保持時間

數據要求保持時間=時鐘到達時間+Th+hold uncertainty

=T+Tclkb+Th+hold uncertainty

hold uncertainty: 時鐘抖動造成的不確定時間。

04 建立時間裕量與保持時間裕量

1.建立時間裕量

建立時間裕量=數據要求到達時間-數據到達時間

=T+Tclkb-Tsu-setupuncertainty -(Tclka+Tco+Tdata)

2.保持時間裕量

保持時間裕量=數據到達時間(新的)-數據要求保持時間

=Tclka+Tco+Tdata-Tclkb-Th-hold uncertainty

3.建立與保持時間裕量整合

建立時間裕量與保持時間裕量為正,則滿足時序要求,如果時間裕量為負,則不滿足時序要求。

建立時間裕量與保持時間裕量為正,則滿足時序要求,如果時間裕量為負,則不滿足時序要求。

系統時鐘頻率

Tlogic為代碼導致的延時,Tnet為布線延時。

05 總結

1、發送沿通常為時序分析的參考時間點

2、通常,捕獲沿=發送沿+1個時鐘周期

3、建立時間與保持時間是由芯片工藝本身決定。提高系統時鐘頻率由決Tdata定。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

寄存器

+關注

關注

31文章

5325瀏覽量

120041 -

時序分析

+關注

關注

2文章

127瀏覽量

22551 -

CLK

+關注

關注

0文章

127瀏覽量

17128

發布評論請先 登錄

相關推薦

放大電路中反饋的基本概念及判斷方法

總結一下在時序分析中的基本概念及基本術語

總結一下在時序分析中的基本概念及基本術語

評論