本系列將帶來(lái)FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開(kāi)始,最詳細(xì)操作步驟,最直白的言語(yǔ)描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業(yè)學(xué)生、初入職場(chǎng)小白及打算進(jìn)階提升的職業(yè)開(kāi)發(fā)者都可以有系統(tǒng)性學(xué)習(xí)的機(jī)會(huì)。

系統(tǒng)性的掌握技術(shù)開(kāi)發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。后續(xù)會(huì)陸續(xù)更新 Xilinx 的 Vivado、ISE 及相關(guān)操作軟件的開(kāi)發(fā)的相關(guān)內(nèi)容,學(xué)習(xí)FPGA設(shè)計(jì)方法及設(shè)計(jì)思想的同時(shí),實(shí)操結(jié)合各類操作軟件,會(huì)讓你在技術(shù)學(xué)習(xí)道路上無(wú)比的順暢,告別技術(shù)學(xué)習(xí)小BUG卡破腦殼,告別目前忽悠性的培訓(xùn)誘導(dǎo),真正的去學(xué)習(xí)去實(shí)戰(zhàn)應(yīng)用。話不多說(shuō),上貨。

Signal tap 邏輯分析儀使用教程

在之前的設(shè)計(jì)開(kāi)發(fā)時(shí),利用modelsim得出中間某單元的數(shù)據(jù),并且輸入也是設(shè)計(jì)者在testbench中自己給出的。但是,實(shí)際應(yīng)用時(shí),外部輸入的信號(hào)不一定和我們?cè)趖estbench中所描述輸入的信號(hào)相同,就有可能導(dǎo)致RTL仿真成功,但是下板測(cè)試失敗。

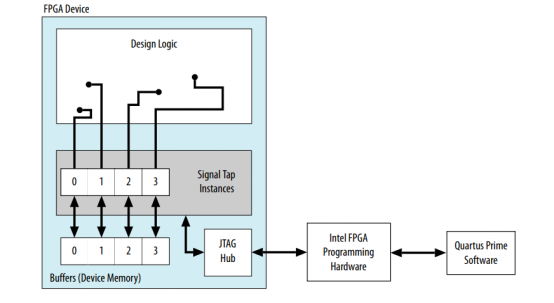

signal tap logic analyzer 采集并顯示FPGA設(shè)計(jì)中的實(shí)時(shí)信號(hào)行為,從而無(wú)需額外的I/O管腳或者外部實(shí)驗(yàn)室設(shè)備即可檢查正常器件操作期間內(nèi)部信號(hào)的行為。

在數(shù)據(jù)獲取期間,器件中的存儲(chǔ)器模塊存儲(chǔ)采集的數(shù)據(jù),然后通過(guò)JTAG通信電纜將數(shù)據(jù)傳輸?shù)竭壿嫹治鰞x。

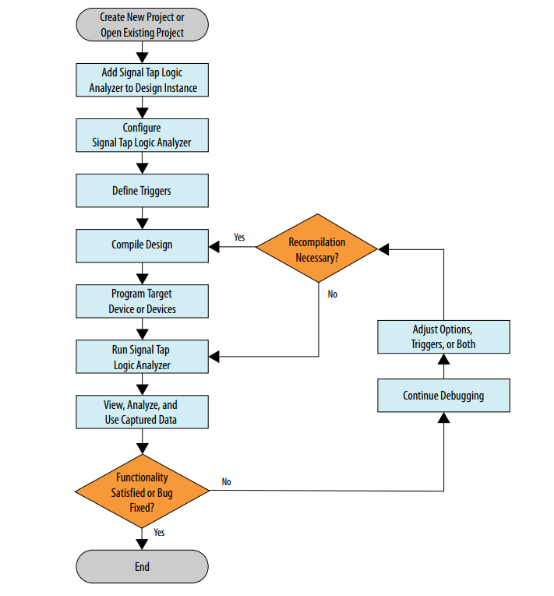

下圖為signal tap logic analyzer的任務(wù)流程。

設(shè)計(jì)要求

利用邏輯分析儀測(cè)量出電腦發(fā)送UART(波特率為115200時(shí))是每bit時(shí)間寬度。

設(shè)計(jì)分析

在UART協(xié)議中規(guī)定了每bit的時(shí)間寬度應(yīng)該是1秒鐘除以波特率,但是在實(shí)際電路中相同標(biāo)號(hào)的兩個(gè)晶振也會(huì)有一定的誤差。我們可以利用邏輯分析儀(也就是利用FPGA的時(shí)鐘)去測(cè)量一下PC發(fā)送UART時(shí)的bit時(shí)間寬度。

由于波特率為115200,在采樣時(shí),一般采用16倍頻采樣。此時(shí)采樣頻率比較高,由基礎(chǔ)的50MHz的時(shí)鐘不能夠做出精確的16倍頻,由此也會(huì)帶來(lái)一定的誤差。

利用邏輯分析儀就可以看到在上述兩個(gè)都有誤差的情況,真實(shí)采樣的偏差,以及偏差對(duì)我們的設(shè)計(jì)是否有影響。

設(shè)計(jì)實(shí)現(xiàn)

將_9_uart_drive 復(fù)制一份,命名為_(kāi)10_uart_drive_signal_tap。然后打開(kāi)此工程,將波特率修改為115200。

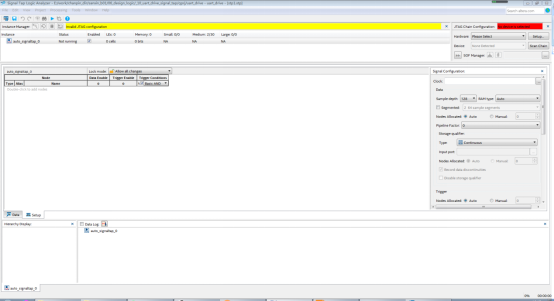

點(diǎn)擊tools -> signal tap logic analyzer。

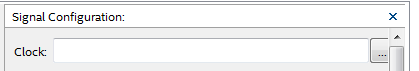

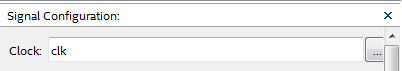

在右側(cè)窗口signal configuration中,首先需要指定一個(gè)采樣時(shí)鐘信號(hào)。

邏輯分析儀在采樣時(shí)鐘的每個(gè)上升沿進(jìn)行數(shù)據(jù)采樣。邏輯分析儀不支持在采樣時(shí)鐘的下降沿進(jìn)行數(shù)據(jù)采樣。設(shè)計(jì)中的任何信號(hào)都可以用作采樣時(shí)鐘。但是,為了獲得最佳的數(shù)據(jù)采樣結(jié)果,請(qǐng)使用與被測(cè)信號(hào)同步的全局時(shí)鐘。

在本設(shè)計(jì)中,所有的信號(hào)都是由外部的clk信號(hào)進(jìn)行驅(qū)動(dòng)的,所以此采樣時(shí)鐘,選擇為clk。點(diǎn)擊clock對(duì)話框后面的三個(gè)點(diǎn)。將filter選擇為pin:all,點(diǎn)擊list,在matching nodes中選擇clk,點(diǎn)擊“大于”,在nodes found中出現(xiàn)clk,然后點(diǎn)擊ok。

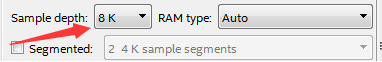

配置完采樣時(shí)鐘信號(hào)后,需要配置采樣深度。

針對(duì)被采樣的數(shù)據(jù)中的每個(gè)信號(hào),采樣深度指定了采樣和存儲(chǔ)的樣本的數(shù)量。在器件存儲(chǔ)器資源有限的情況下,由于所選的深度太大,設(shè)計(jì)可能無(wú)法編譯。此時(shí)需要降低采樣深度以減少資源使用。

采樣深度乘以采樣的間隔就確定了采樣的時(shí)間寬度。現(xiàn)在我們要做的是采樣一個(gè)UART的協(xié)議幀,一個(gè)協(xié)議幀共有12個(gè)bit。按照115200的波特率,采樣的時(shí)間寬度應(yīng)該是104166ns,所以采樣深度應(yīng)該是5208,在此選擇采樣深度為8K。

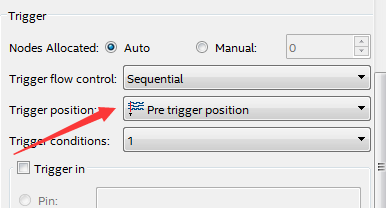

當(dāng)確定好采樣深度后,可以指定邏輯分析儀在觸發(fā)事件之前和之后 采樣的數(shù)據(jù)量。

邏輯分析儀提供三種選擇。Pre表示12%的存儲(chǔ)深度用作觸發(fā)事件之前,88%的存儲(chǔ)深度用作觸發(fā)事件之后;Center表示50%的存儲(chǔ)深度用作觸發(fā)事件之前,50%的存儲(chǔ)深度用作觸發(fā)事件之后;Post表示88%的存儲(chǔ)深度用作觸發(fā)事件之前,12%的存儲(chǔ)深度用作觸發(fā)事件之后。

在此選擇Pre。

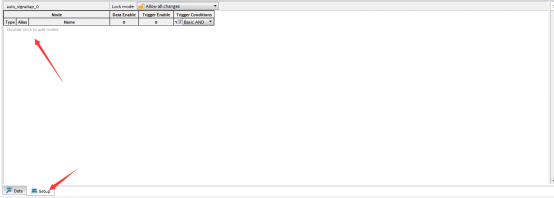

配置好這些信息后,開(kāi)始添加需要觀測(cè)的信號(hào)。

在setup界面,在空白界面雙擊,添加想要觀測(cè)的信號(hào)。

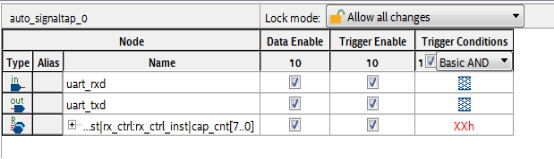

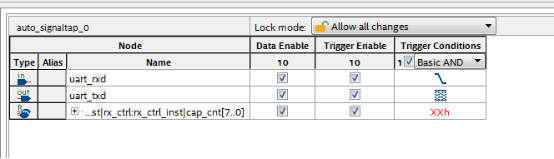

需要觀測(cè)的信號(hào)有uart_txd、uart_rxd、cap_cnt。

uart_txd和uart_rxd為端口信號(hào),選擇filter時(shí),選擇PIN:all即可,cap_cnt為內(nèi)部信號(hào),選擇filter時(shí),選擇signal tap :pre-synthesis。

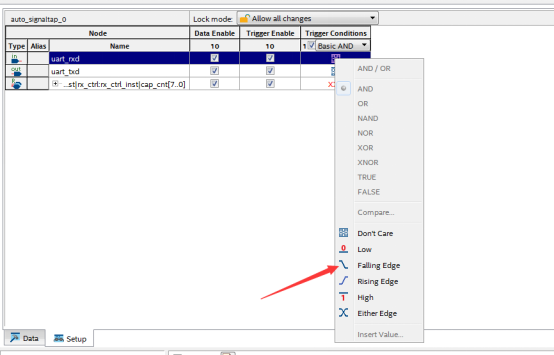

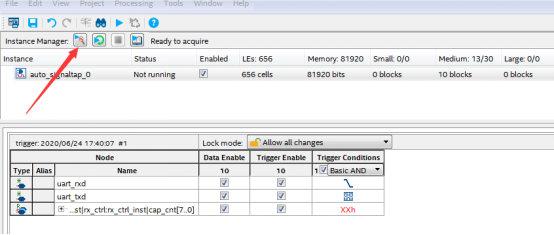

將uart_rxd的下降沿設(shè)置為觸發(fā)條件。

在uart_rxd的trigger conditions的位置,右擊,選擇falling edge。

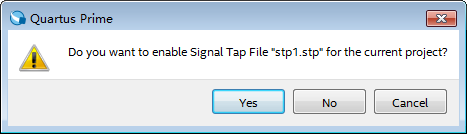

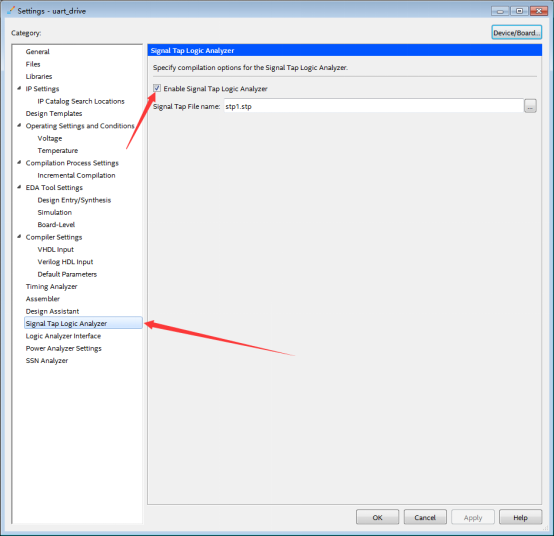

點(diǎn)擊保存,保存到qprj,命名為stp1.stp。

使能邏輯分析儀。點(diǎn)擊Yes。

回到quartus界面,進(jìn)行綜合分析并形成配置文件。

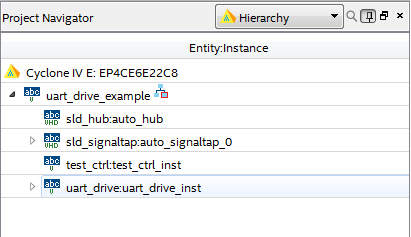

在工程向?qū)У慕Y(jié)構(gòu)界面,可以看到在結(jié)構(gòu)中出現(xiàn)了兩個(gè)未知的組件。這兩個(gè)就是邏輯分析儀。

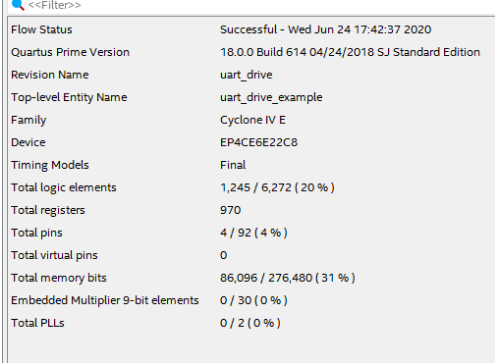

在報(bào)告中,可以看到使用的邏輯資源和存儲(chǔ)器資源增多。

回到signal tap界面,并且連接PC和開(kāi)發(fā)板。

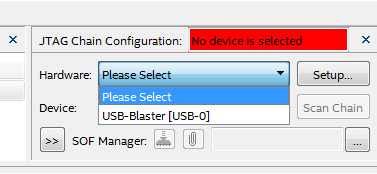

在hardware中,選擇USB – blaster。

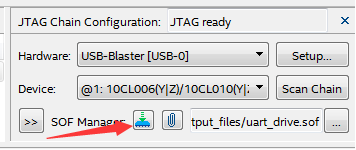

點(diǎn)擊sof manager后面的三個(gè)小點(diǎn),選擇生成的sof文件,然后點(diǎn)擊下載。

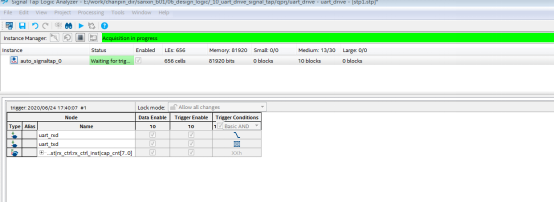

點(diǎn)擊運(yùn)行分析。

此時(shí)邏輯分析儀就在等待被觸發(fā)。

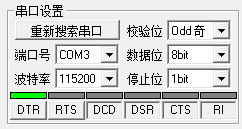

觸發(fā)條件為uart_rxd的下降沿,打開(kāi)串口助手,配置好后,發(fā)送一個(gè)數(shù)據(jù)11。

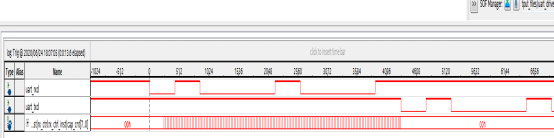

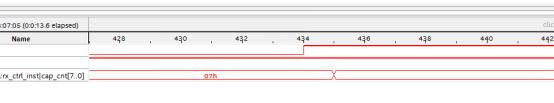

發(fā)送之后,邏輯分析儀中出現(xiàn)了波形。因?yàn)榘l(fā)送為11,發(fā)送數(shù)據(jù)從低位開(kāi)始,故而第一個(gè)數(shù)據(jù)應(yīng)該為1。所以第一端低電平為起始位,可以通過(guò)采樣的數(shù)字標(biāo)號(hào),確定它的時(shí)間寬度。

左鍵是放大,右鍵是縮小。

左側(cè)為0,因?yàn)槔孟陆笛刈鳛橛|發(fā)條件。放大左側(cè)數(shù)字為434。

所以起始位的時(shí)間寬度為434x20ns,即8680ns。按照波特率為115200計(jì)算,每一個(gè)bit的時(shí)間寬度應(yīng)該是8680.5556ns。這就證明PC發(fā)過(guò)來(lái)的bit的時(shí)間寬度和我們所預(yù)想的是一致的。

可以用此方法測(cè)量其他的bit的寬度,有的bit的寬度要比8680ns要少,有的bit的寬度要比8680ns要多,但是偏差不多。

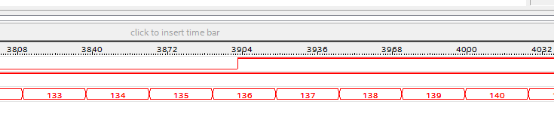

由于真正的寬度和我們認(rèn)為的寬度有一定的區(qū)別。但是設(shè)計(jì)是按照每個(gè)bit的寬度都是20ns的整數(shù)倍,所以在采樣時(shí),就會(huì)有偏差。通過(guò)cap_cnt可以看出來(lái),并且隨著采樣的越長(zhǎng),誤差累計(jì)就會(huì)越大。

在數(shù)據(jù)的第一個(gè)bit時(shí),cap_cnt等于7,馬上要變?yōu)?。按照cap_cnt的計(jì)數(shù)規(guī)律是波特率的16倍頻設(shè)計(jì),所以后面所有的bit起始時(shí),都應(yīng)該是16 *N + 7,并且馬上要變?yōu)?6 * N + 8。但是真實(shí)的時(shí)間寬度和預(yù)想的時(shí)間寬度有一定的偏差。

在最后的校驗(yàn)位的起始時(shí),cap_cnt的數(shù)據(jù)按照16倍頻采樣來(lái)說(shuō),應(yīng)該是135,然后快變?yōu)?36才對(duì)。但是此時(shí)已經(jīng)等于136,并且馬上變137。

我們是按照cap_cnt去進(jìn)行采樣的(在cap_cnt變化的位置采樣)。

因?yàn)橛姓`差,所以規(guī)定UART的協(xié)議幀的長(zhǎng)度不能夠過(guò)長(zhǎng)。即中間的數(shù)據(jù)位的個(gè)數(shù)不能隨意增加。

上述分析步驟的數(shù)字只是筆者的測(cè)驗(yàn)結(jié)果,不同的PC和開(kāi)發(fā)板測(cè)試時(shí),可能會(huì)得到不同的結(jié)果。

邏輯分析儀總結(jié)

利用邏輯分析儀可以直接查看到開(kāi)發(fā)板內(nèi)部運(yùn)行的波形。所以在很多時(shí)候,都是利用邏輯分析儀進(jìn)行板級(jí)測(cè)試作為最終結(jié)果。

如果不需要工程中的邏輯分析儀,可以打開(kāi)assignments -> settings –> signal tap logic analyzer,將使能的對(duì)勾去掉,然后重新編譯就可以了。

更多熱點(diǎn)文章閱讀

-

電子技術(shù)

+關(guān)注

關(guān)注

18文章

884瀏覽量

55866 -

電子發(fā)燒友論壇

+關(guān)注

關(guān)注

4文章

197瀏覽量

1056

原文標(biāo)題:【教程分享】FPGA零基礎(chǔ)學(xué)習(xí):Signal tap 邏輯分析儀使用教程

文章出處:【微信號(hào):gh_9b9470648b3c,微信公眾號(hào):電子發(fā)燒友論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談邏輯分析儀的技術(shù)原理和應(yīng)用領(lǐng)域

Keysight 頻譜分析儀(信號(hào)分析儀)

multisim中邏輯分析儀怎么連接

邏輯分析儀multisim的應(yīng)用

邏輯分析儀可以當(dāng)示波器用嗎

邏輯分析儀主要工作方式是什么

24M的邏輯分析儀怎么用的

邏輯分析儀的主要用途是什么

邏輯分析儀的使用說(shuō)明

矢量信號(hào)分析儀與矢量網(wǎng)絡(luò)分析儀的區(qū)別

邏輯分析儀的常見(jiàn)故障及原因

邏輯分析儀的基本原理、結(jié)構(gòu)組成及關(guān)鍵技術(shù)

如何用內(nèi)部邏輯分析儀調(diào)試FPGA?

邏輯分析儀產(chǎn)生的脈沖頻率不對(duì)

使用Raspberry Pi Pico實(shí)現(xiàn)簡(jiǎn)單的邏輯分析儀

【教程分享】FPGA零基礎(chǔ)學(xué)習(xí):Signal tap 邏輯分析儀使用教程

【教程分享】FPGA零基礎(chǔ)學(xué)習(xí):Signal tap 邏輯分析儀使用教程

評(píng)論