軟硬件工程之間的界限比我們看到的更模糊。稱之為現場可編程門陣列 (FPGA) 的器件,其物理屬性可通過使用硬件描述語言 (HDL) 來操控,該器件可在軟硬件編程之間架起一座橋梁。

但人們通常認為,FPGA 是只能由硬件工程師編程的器件。幸運的是,今時不同往日,現代統一軟件平臺插入通用開發工具,可簡化 FPGA 的編程過程。

事實上,軟件開發人員也可了解如何編程 FPGA。本文將首先介紹 FPGA 的基礎知識,比如 FPGA 的工作原理以及為什么要使用 FPGA 等。然后討論設計和執行首款 FPGA 應用所需的工具。

何為 FPGA 以及為什么使用 FPGA?

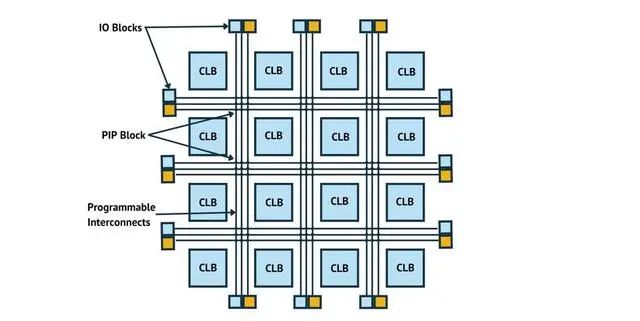

FPGA 是一種集成電路 (IC),具有可配置邏輯塊 (CLB) 以及其它用戶可編程并可重新編程的特性。術語“現場可編程”表示 FPGA 的功能是可調節的,與其它由制造商硬連接的 IC 不一樣。

FPGA 是屬于可編程邏輯器件 (PLD) 范疇的集成電路 (IC)。FPGA 技術的基本功能建立在自適應硬件之上,具有制造后可修改的獨特功能。硬件塊陣列(每塊都可配置)可根據需要進行連接,允許為所有應用構建特定域的高效架構。

這種硬件靈活應變性是 CPU 和 GPU 所不具備的獨特差異化特性。

雖然 CPU 靈活性很高,但其底層硬件是固定的。CPU 一旦出廠,硬件就無法修改。它依靠軟件來告訴它要針對內存中的哪個數據執行哪項具體運算(算術函數)。硬件必須能夠執行所有可能的運算,稱之為使用軟件指令,通常一次只能執行一條指令。相比之下,FPGA 可并行處理海量數據。與 CPU 相比,自適應硬件的優勢因應用而異,很大程度上取決于計算的性質及其并行化的能力,但與功能可高度并行化的 CPU 實現方案相比,性能提高 20 倍的情況并不少見。

GPU 不僅可彌補 CPU 的一個主要不足之處 — 并行處理大量數據的能力,而且運行的數據集還很寬。從根本上講,GPU 和 CPU 類似,因為它們有固定的硬件,而且使用軟件指令運行。一條指令可處理 1000 個以上的數據,因此它們適用于圖形加速、高性能計算、視頻處理以及某些形式的機器學習等特定域。但從根本上講,GPU 的基本架構和數據流在制造之前是固定的。

FPGA 可幫助編程人員和設計人員更靈活地適應和更新計算架構,從而帶來更能滿足其需求的特定域架構。FPGA 并不是什么新事物,但因人工智能等領域的創新速度,其重要性日益凸顯。第一款商用 FPGA 是 AMD 于 1985 年發明的,在目前的 FPGA 市場上占據 60% 至 70% 的份額。

下載電子書

FPGA 的用途與應用

FPGA 應用廣泛。今天,數據中心、航空航天工程、國防、人工智能 (AI)、工業物聯網 (IoT)、有線及無線網絡以及汽車等眾多行業無處不見其身影。這類器件通常處于用戶需要實時信息的環境中。例如,一款家庭安防攝像頭需要將即時圖像以高分辨率和最小的時延傳給房主的智能設備。隨著消費者對通過手機收發即時信息的依賴程度越來越高,這些期望值只會增加。

此外,FPGA 也有助于完成本來可以在軟件中完成的功能加速。這使得 FPGA 成了一種非常有幫助的工具,可卸載需要高性能的任務,比如人工智能的深度神經網絡 (DNN) 推斷。

FPGA 和硬件加速

FPGA 的架構使其成了硬件加速的高效解決方案。ASIC 和 GPU 等器件使用一種過時的方法在編程和內存之間切換。而且它們也不能適應需要實時信息的應用,因為存儲和檢索任務所需的高功率會導致性能滯后。

與 ASIC 和 GPU 不同, FPGA 不需要在內存和編程之間切換,這使得存儲和檢索數據的過程更高效。FPGA 架構靈活性更高,因此您可以自定義您希望 FPGA 用于特定任務的電源。

這種靈活性有助于將能耗極高的任務從傳統 CPU 或其它器件轉移到一個或幾個 FPGA 上。許多 FPGA 都可以重新編程,因此您可以對硬件加速系統輕松進行升級和調整。

FPGA 編程是怎樣進行的?

FPGA 編程可根據您希望器件具備的功能,使用 HDL 來操控電路。該過程不同于對 GPU 或 CPU 的編程,因為您編寫的程序將不會按順序運行。相反,您可使用 HDL 來創建電路,并根據您想要的功能對硬件進行物理修改。

這個過程類似于軟件編程,其中您編寫的代碼將轉換成二進制文件并加載在 FPGA 上。但結果是 HDL 對硬件進行了物理修改,而不是通過嚴格優化器件來運行軟件。

FPGA 上的一個程序將邏輯門和內存塊等較低層次的元件組裝在一起,其可協同工作,共同完成一項任務。因為您是從頭開始操控硬件的,因此 FPGA 將帶來很高的靈活性。您可以根據任務調整內存或功耗等基本功能。

用于編程 FPGA 的語言

FPGA 似乎主要服務于芯片設計人員,而不是專門從事軟件開發的工程師。畢竟,大多數用于編寫 FPGA 代碼的 HDL 都是較低級的語言,硬件工程師可能比軟件工程師更熟悉這些語言。但有些 HDL 與通用軟件語言的類似程度遠比您想象的高。

當我們將“編程”一詞用于 FPGA 時,因為程序的設置方式和執行方式的緣故,它與創建軟件并不完全相同。但使用該術語確實包含了編寫并執行 FPGA 代碼與創建軟件算法的過程相似的理念。最初的思維方式是,FPGA 只能由電路設計硬件工程師來編程。今時不同往日。

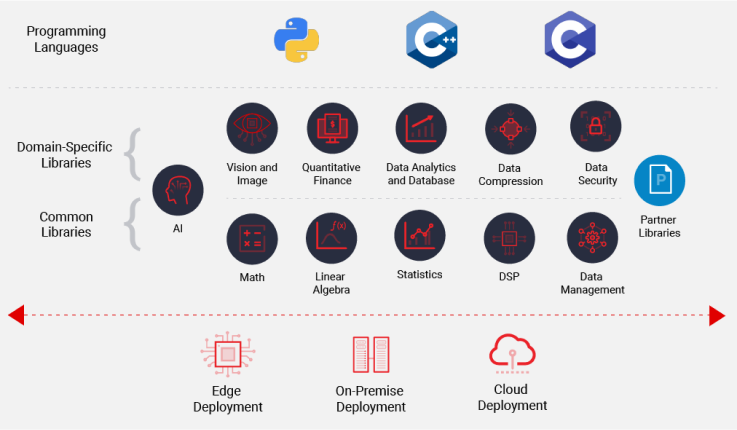

在統一軟件平臺的幫助下,軟件開發人員無需掌握 HDL 技術,便可使用他們喜歡的語言來對 FPGA 進行編程。這不僅可消除必須轉而采用全新編程語言的壓力,而且還可幫助軟件開發人員將工作重心從硬件轉向概念。這些平臺的工作原理本質上是將較高級的語言翻譯成較低級的語言,以便 FPGA 執行所需的功能。能夠與統一軟件平臺一起用于 FPGA 編程的語言包括:

-

TensorFlow 和 Pytorch 等 AI 框架 :有了 Vitis AI, AI 科學家現在可直接從 TensorFlow 或 Pytorch 獲取其訓練有素的深度學習模型,并針對 FPGA 加速進行編譯。這不僅無需對低層次硬件進行編程,而且還可在幾分鐘內實現瞬間編譯,從而能夠與使用 CPU 和 GPU 的典型軟件編譯體驗相媲美。

-

C 和 C++ :在高層次綜合 (HLS) 的幫助下,基于 C 語言的語言現在可用于 FPGA 設計。具體來說,AMD Vivado HLS 編譯器提供的編程環境能夠與標準處理器及專用處理器共享關鍵技術,用于優化 C 語言程序和 C++ 程序。這允許軟件工程師優化代碼,無需掃清有限內存空間或計算資源的路障。

-

Python :設計人員可使用 Python 語言和庫來創建高性能應用并通過 PYNQ 編程 FPGA。PYNQ 是 AMD 的一個開源項目,可簡化 AMD 平臺的使用。

此外,現在主要用于 FPGA 編程的,也有大量主流 HDL。下面簡單介紹一下其名稱和主要屬性:

-

Lucid :這種語言是專門針對 FPGA 設計的,可彌補 Verilog 等一些更早語言的不足。

-

VHDL :超高速集成電路 (VHSIC) 硬件描述語言的首字母縮寫,該語言最早出現在 20 世紀 80 年代,主要基于 Ada 和 Pascal。

-

Verilog :Verilog 是有史以來創建的第一款 HDL,今天主要用于測試分析與驗證。該語言的內核基于 C 語言。

如何編程 FPGA

雖然 FPGA 只存在于硬件工程師領域,但 AI 科學家和軟件編程人員現在可以訪問新平臺,讓該過程感覺就像編寫軟件程序一樣。有了正確的工具,您將找到一個為 FPGA 編程的解決方案,在當前的軟硬件知識層面滿足您的需求。

如果您習慣了針對 GPU 進行編程,即使結果有點不同,編寫 FPGA 代碼的過程也會感覺非常相似。FPGA 編程包括編寫代碼、根據需要將該程序翻譯成較低級的語言,以及將該程序轉換為二進制文件。然后,您將向 FPGA 提供程序,操作就像讓 GPU 讀取一款用 C++ 編寫的軟件一樣。就是這么簡單。

但為了優化該編程過程,您需要訪問正確的平臺。幸運的是,AMD 擁有完美的解決方案,這是一套開創性的工具,可在 FPGA 編程過程的每個環節為軟件開發人員提供幫助。

使用 Vitis 統一軟件平臺簡化 FPGA 編程

Vitis 統一軟件平臺是一款領先應用,可為軟件工程師、數據科學家以及 AI 開發人員優化 FPGA 編程過程。它包括一個針對 AMD FPGA 和 ACAP 硬件平臺優化的擴展性開源庫,以及一個內核開發套件,有了該套件,沒有豐富的硬件經驗,也可無縫構建加速應用。

此外,Vitis 還包括 Vitis Model Composer,其在 MATLAB 和 Simulink 中提供了一個工具套件。它可優化設計并測試新應用的過程。

如何使用 Vitis 軟件針對應用加速啟動設計

Vitis 分四個步驟幫助您針對邊緣、本地或云端的數據及計算密集型應用設計加速器:

-

確定應用中需要加速的性能關鍵部分。

-

使用 Vitis 加速庫設計加速器,也可使用 C、C++、OpenCL 或 RTL 開發自己的加速器。

-

構建、分析和調試,以驗證功能正確性并確保符合性能目標。

-

在邊緣、本地或云端的 AMD 平臺上部署加速應用。

AMD 是業內排名第一的 FPGA 供應商

盡管沒有硬件專業技術,FPGA 編程可能會讓人望而卻步,但 Vitis 等平臺可幫助軟件開發人員簡化該過程。AMD 是業界收入最高的 FPGA 廠商,也是為軟件工程師創建 FPGA 應用提供資源的行業領導者。

使用 C、C++ 和 OpenCL 編寫的函數可以使用 AMD Vitis HLS 工具集成到硬件中。HLS 工具不僅可為代碼修改實現自動化,簡化更新,而且還可針對每款應用的低時延和高吞吐量優化 C/C++ 代碼。

更多熱點文章閱讀

-

基于32位RISC-V設計的互聯型微控制器,沁恒微CH32V307開發樣例

-

RK3568!四核64位ARMv8.2A架構,匯聚編譯源碼及實戰樣例

-

尺寸僅有21mm*51mm,板邊采用郵票孔設計,合宙 Air105 核心板開發總結

原文標題:【干貨分享】FPGA 編程:原理概述

文章出處:【微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

-

電子技術

+關注

關注

18文章

884瀏覽量

55841 -

電子發燒友論壇

+關注

關注

4文章

197瀏覽量

1053

原文標題:【干貨分享】FPGA 編程:原理概述

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【干貨分享】FPGA 編程:原理概述

【干貨分享】FPGA 編程:原理概述

評論