在后仿真過程中經(jīng)常會(huì)遇到關(guān)于setup和hold violation的問題,但是關(guān)于setup和hold time的產(chǎn)生原因和由來很多人還比較朦朧,為此本文通過解剖一個(gè)邊沿觸發(fā)器簡要說明setup和hold產(chǎn)生原因。

解剖示例

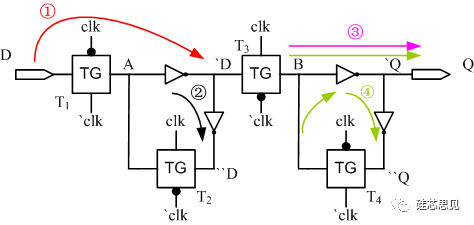

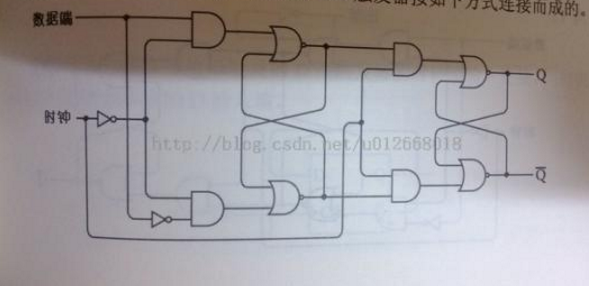

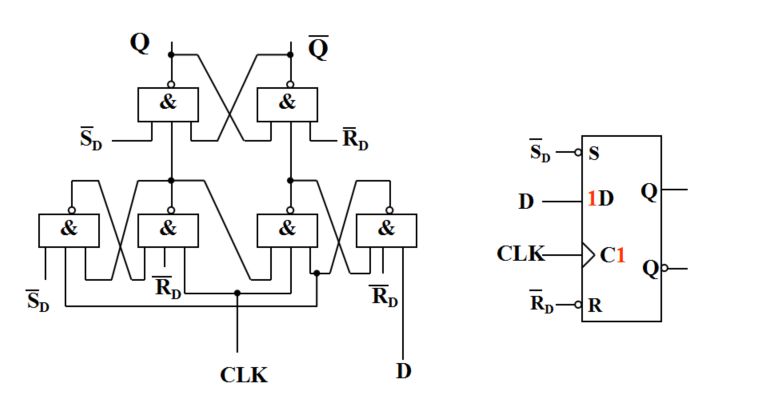

上圖為觸發(fā)器的簡要示意圖(clk和’clk為反向時(shí)鐘)。T1和T4同時(shí)導(dǎo)通,T2和T3同時(shí)導(dǎo)通,且T1、T4和T2、T3導(dǎo)通狀況互反。其中T1、T2、T3、T4均為傳輸門,均為電平敏感,所以所謂的時(shí)鐘跳變可以理解為高低電平的相互跳變所致。而電路中實(shí)際的延時(shí)信息主要由于電信號(hào)導(dǎo)通時(shí)通過電子器件時(shí)耗費(fèi)的時(shí)間。

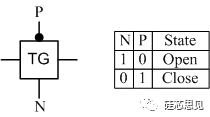

【注】傳輸門的開關(guān)狀態(tài)如下圖所示。

工作過程

clk和’clk互為相反的信號(hào),clk為低電平(’clk為高電平)時(shí),T1和T4導(dǎo)通,此時(shí)數(shù)據(jù)進(jìn)入到`D和``D,因?yàn)榇藭r(shí)T4導(dǎo)通,圖中綠色箭頭線中的數(shù)據(jù)保持上一拍的數(shù)據(jù)結(jié)果。 當(dāng)clk高電平(’clk為低電平)到來時(shí),T1和T4關(guān)斷,T2和T3導(dǎo)通,②中的數(shù)據(jù)維持穩(wěn)定,通過T3輸出至Q端,同時(shí)B點(diǎn)、’Q和’’Q點(diǎn)的數(shù)據(jù)保持一致穩(wěn)定;當(dāng)?shù)碗娖降絹頃r(shí),T2和T3關(guān)斷,T1和T4導(dǎo)通,此時(shí)B點(diǎn)、’Q(Q)和’’Q點(diǎn)數(shù)據(jù)一直穩(wěn)定,因此可以保證綠色箭頭線部分有穩(wěn)定一致的數(shù)據(jù)通過Q端發(fā)送出去。

所以,可以看到在上跳沿采樣的數(shù)據(jù)可以保持一個(gè)時(shí)鐘周期。通過上述分析,我們可以看到一個(gè)邊沿觸發(fā)器實(shí)際上可以解剖為兩個(gè)鎖存器,后續(xù)分析時(shí)也會(huì)用到這種結(jié)構(gòu)特點(diǎn)。 一般觸發(fā)器setup和hold的產(chǎn)生,就跟上述觸發(fā)器的工作過程密切相關(guān),下面一塊來看看兩者之間的聯(lián)系。

setup和hold蹤跡

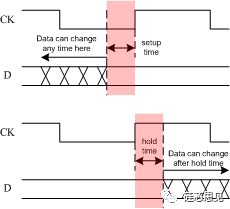

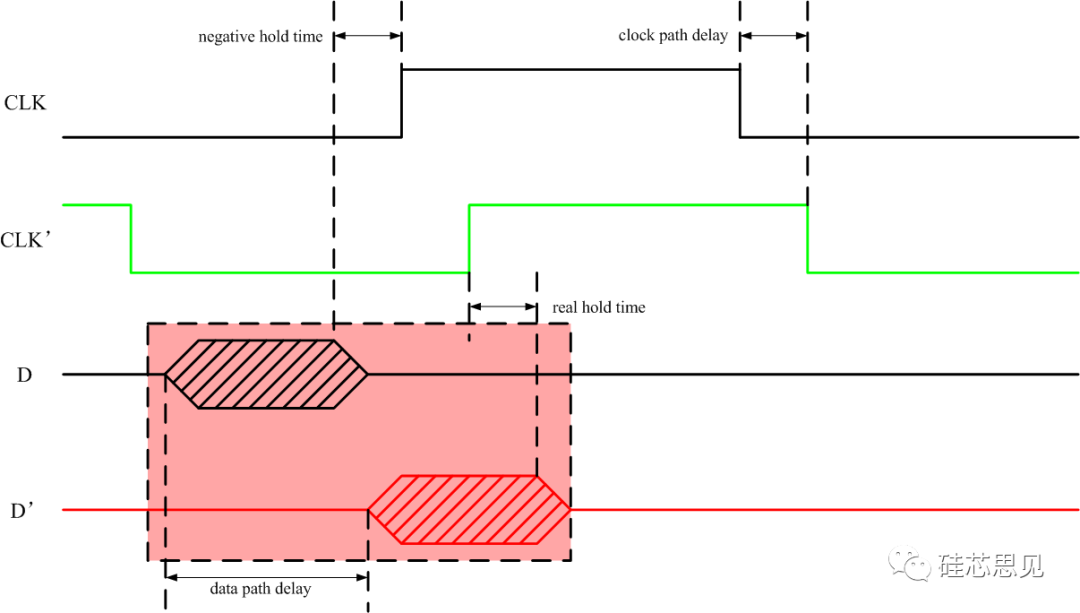

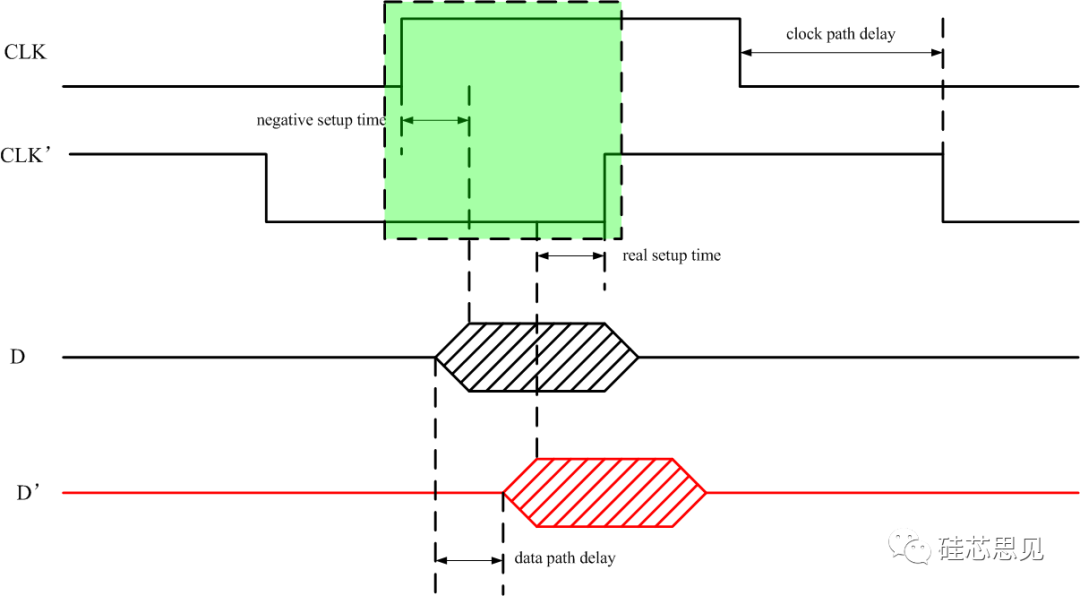

下圖為陰影區(qū)域?yàn)閠iming violation區(qū)。

clk上跳沿之前

setup時(shí)間(tsu):輸入數(shù)據(jù)D在時(shí)鐘上升沿之前必須保持不變的時(shí)間。為了得到有效的數(shù)據(jù),必須保證A點(diǎn)、`D和``D點(diǎn)的數(shù)據(jù)保持一致穩(wěn)定,否則在T2導(dǎo)通時(shí)將會(huì)形成振蕩電路。當(dāng)T1打開時(shí),輸入信號(hào)經(jīng)過T1后分別到達(dá)A點(diǎn)、`D和``D點(diǎn),并且保持一致,耗費(fèi)的時(shí)間為Ts,時(shí)鐘從低電平跳變到高電平需要耗費(fèi)時(shí)間為Tc,因此,為了保持?jǐn)?shù)據(jù)的有效和電路的穩(wěn)定,輸入數(shù)據(jù)需要保持的時(shí)間至少應(yīng)該為Ts,如果不滿足將會(huì)在T2導(dǎo)通時(shí),A點(diǎn)、`D和``D點(diǎn)的值不同,從而可能會(huì)產(chǎn)生亞穩(wěn)態(tài)。因此,可以這樣理解,所謂的建立時(shí)間是指輸入數(shù)據(jù)D經(jīng)過多長時(shí)間才能使`D的數(shù)據(jù)穩(wěn)定可靠。所以setup指的是數(shù)據(jù)從D到達(dá)``D的時(shí)間。

clk上跳沿之后

hold時(shí)間(thold):在時(shí)鐘上升沿到達(dá)后,輸入數(shù)據(jù)需要保持穩(wěn)定的時(shí)間。在clk上跳沿發(fā)生之后,T1和T4關(guān)閉,T2和T3打開,數(shù)據(jù)從Q端輸出。但是需要注意,因?yàn)門1關(guān)閉需要時(shí)間,所以在T1和T4關(guān)閉到T2和T3打開輸入數(shù)據(jù)必須保持穩(wěn)定,如果A點(diǎn)的數(shù)據(jù)受到D點(diǎn)的影響,從而導(dǎo)致A點(diǎn)和D點(diǎn)數(shù)據(jù)不一致,也就是在上跳沿發(fā)生后,即T2、T3導(dǎo)通時(shí),②中循環(huán)的數(shù)據(jù)不能保持穩(wěn)定一致,從而導(dǎo)致Q端數(shù)據(jù)不穩(wěn)定。因此,thold可以理解為D端數(shù)據(jù)通過T1,再經(jīng)過②到達(dá)A點(diǎn),保證A和`D點(diǎn)數(shù)據(jù)一致穩(wěn)定的時(shí)間。 上面是對setup和hold產(chǎn)生原因的一些簡單介紹,有些朋友可能會(huì)問,上文中setup和hold感覺都是正值,為什么我在仿真的時(shí)候遇到過setup或者h(yuǎn)old為負(fù)值的情況呢?為了探討方便,此處以常用到的一種觸發(fā)器(由兩個(gè)鎖存器組成)為例進(jìn)行簡單的說明。

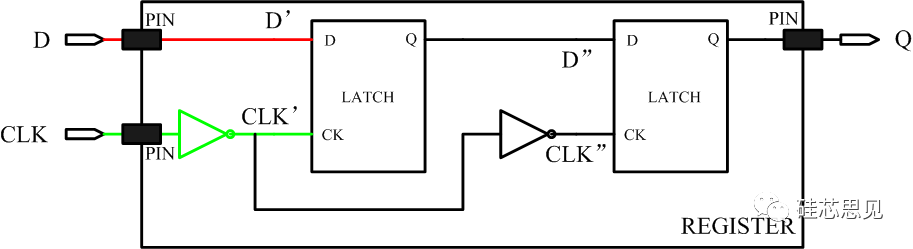

hold time為負(fù)值

當(dāng)data從pin到鎖存數(shù)據(jù)的鎖存器的delay時(shí)間大于clock從pin到達(dá)鎖存器CK端的delay時(shí),那么當(dāng)D結(jié)束于CLK上升沿之前,此時(shí)從REGISTER層面觀測到的hold為負(fù)值,而實(shí)際上在鎖存數(shù)據(jù)的鎖存器端,由于之前data延遲大于clock延遲,CLK'對D'進(jìn)行控制時(shí),D'相對于CLK'一直保持到CLK'為高電平之后,也就是此時(shí)hold為正值,出現(xiàn)在上升沿右側(cè)。

setup time為負(fù)值

當(dāng)data從pin到鎖存數(shù)據(jù)的鎖存器的delay時(shí)間小于clock從pin到達(dá)鎖存器CK端的delay時(shí),那么當(dāng)D開始于CLK上升沿之后,此時(shí)從REGISTER層面觀測到的setup為負(fù)值,而實(shí)際上在鎖存數(shù)據(jù)的鎖存器端,由于之前data延遲小于clock延遲,CLK'對D'進(jìn)行控制時(shí),D'出現(xiàn)在了CLK'之前,也就是此時(shí)setup為正值,出現(xiàn)在上升沿左側(cè)。

審核編輯:劉清

-

鎖存器

+關(guān)注

關(guān)注

8文章

904瀏覽量

41444 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

1995瀏覽量

61051 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17125 -

邊沿觸發(fā)器

+關(guān)注

關(guān)注

0文章

34瀏覽量

3976

原文標(biāo)題:說說setup和hold violation

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

什么是Setup和Hold時(shí)間

CMOS觸發(fā)器在CP邊沿的工作特性研究

邊沿觸發(fā)SR觸發(fā)器

jk邊沿觸發(fā)器工作原理

什么是邊沿觸發(fā)器_邊沿D觸發(fā)器介紹

邊沿觸發(fā)器怎么看

一文詳解邊沿觸發(fā)器

通過解剖一個(gè)邊沿觸發(fā)器簡要說明setup和hold產(chǎn)生原因

通過解剖一個(gè)邊沿觸發(fā)器簡要說明setup和hold產(chǎn)生原因

評論