基本原理

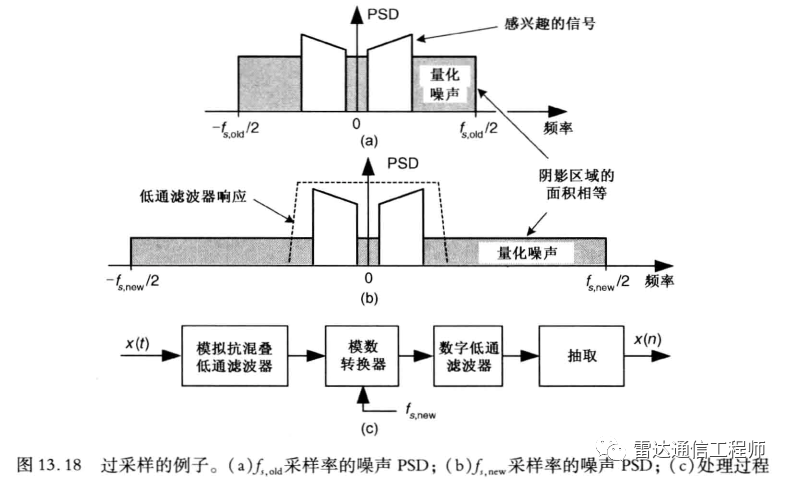

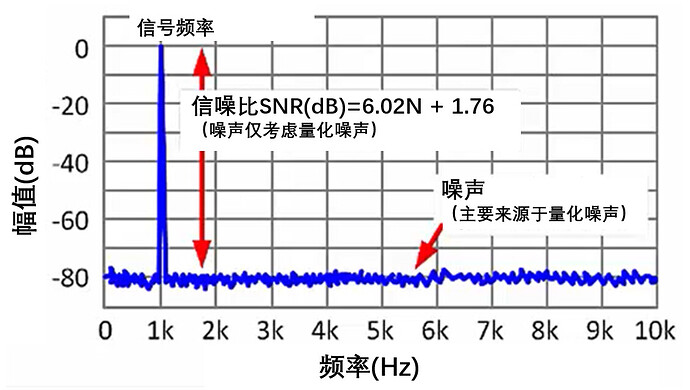

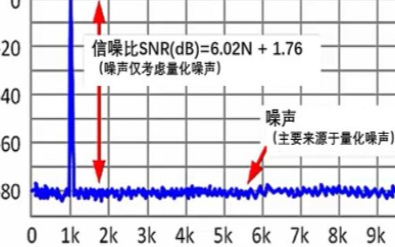

如上圖所示,過采樣提升信噪比的基本原理:對于確定的ADC芯片,其采樣的量化噪聲為固定常數,其均勻的分布在Fs/2帶寬的奈奎斯特區間內,當采樣率Fs增加時,等量的量化噪聲將分布在更換的內奎斯特區間內,噪聲譜密度降低(上圖中陰影區域被壓扁,但面積不變),即同樣信號帶寬內包含的噪聲降低,理論上采樣率每提高一倍,噪聲功率譜密度就降低3dB。

利用該原理而得到的信噪比提升值稱為“處理增益”,因此提高采樣率可以在特定信號帶寬內提高ADC的有效位ENOB,Fs每增加4倍,有效位增加1bit。有專門利用這個原理制造的ADC芯片,即sigma-delta型ADC,其通過很低的實際ADC分辨率(比如2bit)進行超高過采樣(比如1024倍)后再濾波抽取,就能在得到10bit的分辨率,因此很多測量精密直流信號的ADC就適合用這種類型,要求的數據刷新速率較低,如用于測量溫度、壓力這種緩變的24bit、32bit ADC幾乎(應該說全部)都是這種。

sigma-delta型ADC除了利用過采樣外,還利用特殊的噪聲整形技術,將關注的帶內噪聲大部分轉移到帶外,然后再用數字濾波器濾除,如此即可在前面常規過采樣的基礎上進一步降低目標帶寬的噪聲量;噪聲整形的形狀大概有兩種,一種是針對中頻數字接收(如ADI的某些中頻數字接收芯片),有的稱作“浴盆狀”,一種是針對以直流為起點的低通應用,如上面提到的用于近直流測量的24、32bit ADC,重點、重點、重點來了,ADI的射頻收發器如AD9361、71,ADRV9009等的接收通道ADC都屬于sigma-delta型ADC;

注:以上3圖來源自ADI文獻

案列描述

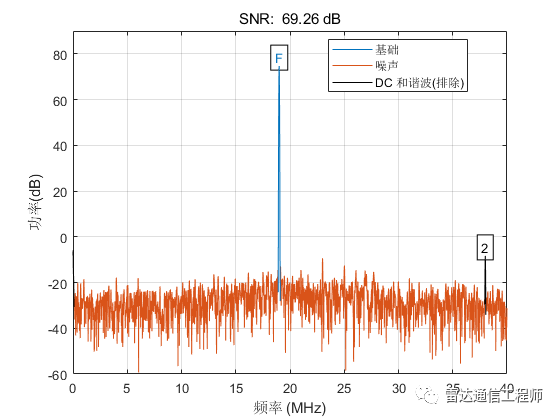

案列描述:使用信號源給ADC輸入一個-1dBFS的61MHz正弦信號,其中ADC采樣率80MHz,信號經過DDC數字下變頻、CIC濾波4抽取、兩級FIR濾波2抽取最終得到5Mbps速率的基帶IQ信號(帶寬4MHz),通過Vivado的ILA核從FPGA同時抓取ADC原始數據、DDC結果、CIC結果、HB濾波結果、FIR濾波結果;然后將數據導入matlab繪制頻譜和計算SNR;文中所有頻譜不是matlab仿真而來,而是在FPGA中采集的實際信號頻譜。

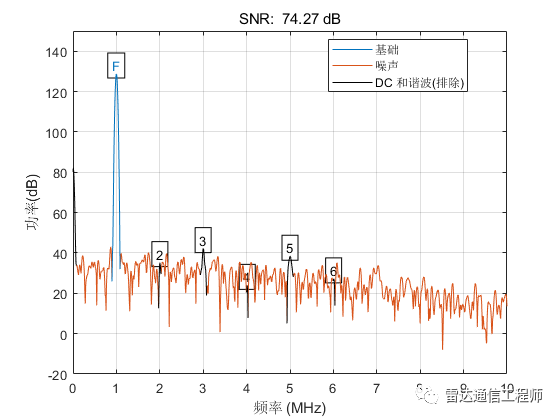

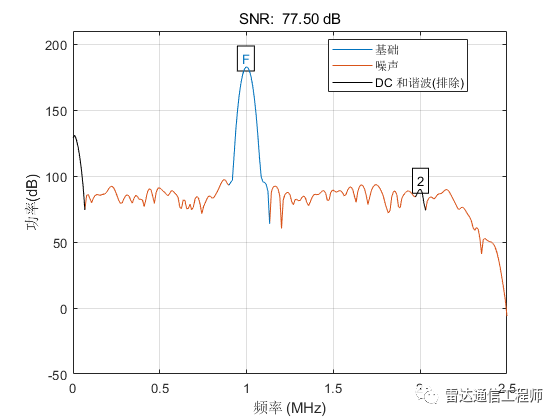

處理增益PG=Fs/(2BW)=80/(25)=8,即理想情況下SNR能夠提升9dB(過采樣處理增益),從圖看出經過系列處理后SNR提高了8.3dB,后文中除了第一個圖是原始實信號外,其余均為基帶I路信號,最后輸出信號的信噪比與理想條件下相差0.7dB,這0.7dB的差異主要就是濾波器不理想(過渡帶)等因素所導致。

基本流程

圖1-ADC采樣的原始數據頻譜

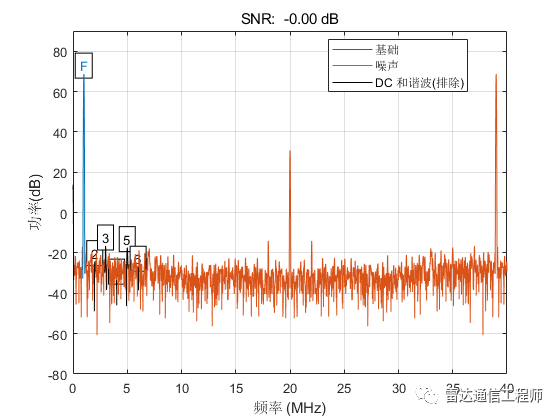

圖2-DDC后的I路數據頻譜

信號中有直流成分,導致DDC過程中NCO本振頻率(20MHz)泄露

圖3-CIC后的I路數據頻譜

實際此處采用4倍CIC抽取其實有些問題,

圖4-HB后的I路數據頻譜

圖5-末級FIR后的I路數據頻譜

濾波器帶寬設置為2MHz,故上圖中可清晰見到2~2.5MHz處的濾波器過渡帶滾降特性。

-

數字濾波器

+關注

關注

4文章

269瀏覽量

46986 -

射頻收發器

+關注

關注

4文章

256瀏覽量

25385 -

數字接收機

+關注

關注

1文章

23瀏覽量

11621 -

FPGA開發板

+關注

關注

10文章

122瀏覽量

31485 -

ADC芯片

+關注

關注

3文章

76瀏覽量

20237

發布評論請先 登錄

相關推薦

基于DSP和FPGA技術的低信噪比雷達信號檢測

利用DSP和FPGA技術的低信噪比雷達信號檢測設計介紹

如何利用DSP和FPGA技術檢測低信噪比雷達信號?

提升JavaEE技術的方法

多帶通信號采樣的信噪比分析

低信噪比下RFID調制識別方法的研究

什么是聲卡采樣/信噪比

過采樣法提高A_D分辨率和信噪比

基于周期平穩的盲信噪比估計方法

信噪比估計方法研究

一種新的非均勻采樣信號的離散傅里葉變換方法

基于fpga的過采樣技術設計

過采樣:提高ADC信噪比巧妙方法

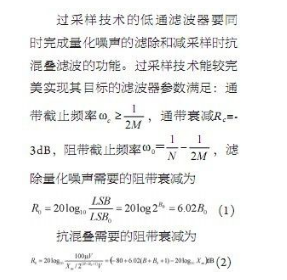

采樣技術對信噪比的提升方法

采樣技術對信噪比的提升方法

評論