引言

??本文主要介紹了時鐘偏差和時鐘抖動。

一、時鐘偏差的相關概念

??時鐘偏差 Clock Skew 是指同一個時鐘域內的時鐘信號,到達各個模塊(如寄存器)所用的時間偏差(由于布線長度不一致以及存在的線延時)。

??時鐘偏差主要分為正偏差和 負偏差 。當信號傳輸的目標寄存器在接收寄存器之前捕獲正確的時鐘信號,電路發生正偏差(時鐘布線方向與數據流水方向一致);當信號傳輸的目標寄存器在接收寄存器之后捕獲正確的時鐘信號,電路發生負偏差(時鐘布線方向與數據流水方向相反)。

正偏差和負偏差

二、時鐘抖動的相關概念

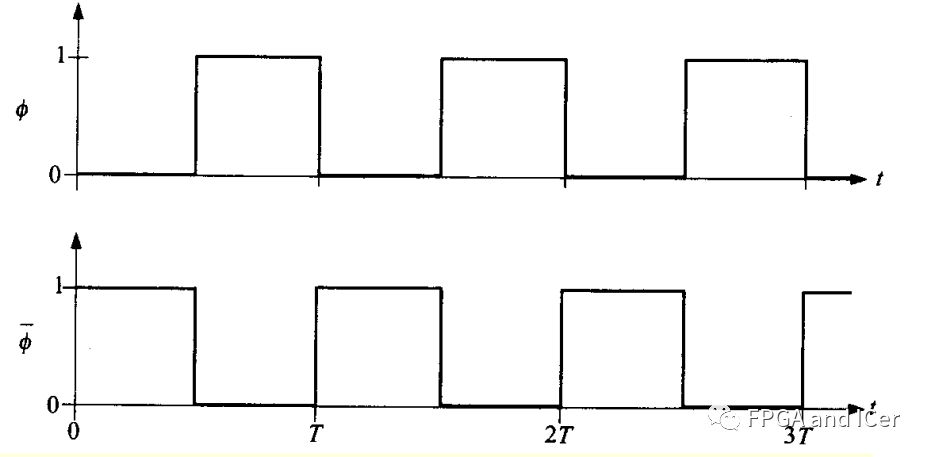

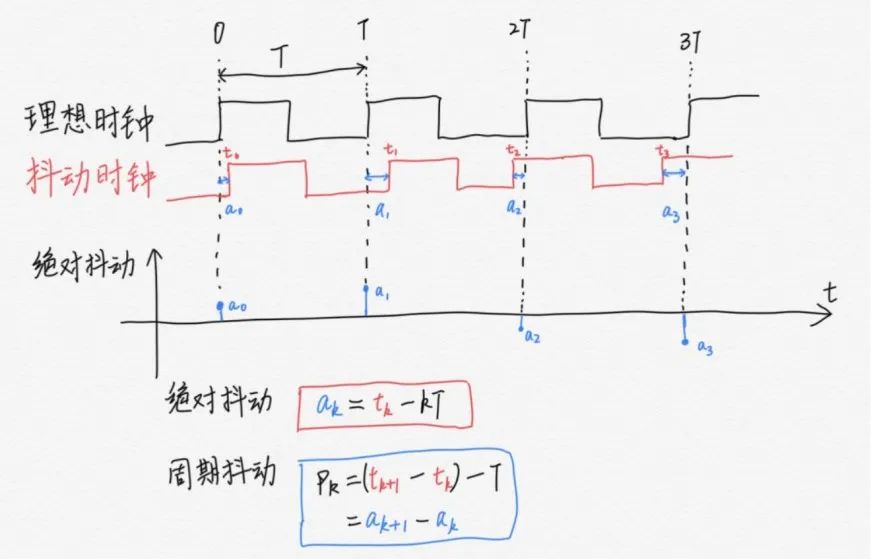

??時鐘抖動 Clock Jitter 是指相對于理想時鐘沿而言,實際時鐘所存在的不隨時間積累的、時而超前、時而滯后的偏移(時鐘脈沖寬度發生了暫時的變化,也就是 Tcycle 或大或小,這是永遠存在的);

總結

??時鐘偏差 Skew 通常是指時鐘相位上的不確定,時鐘抖動 Jitter 通常是指時鐘頻率上的不確定;相位為整體移動,頻率為單個時鐘變動;

??時鐘偏差和時鐘抖動都要求系統時鐘寬度增加,以滿足建立時間和保持時間的要求,從而降低了系統時鐘頻率,導致了系統的性能變差。所有的時鐘網絡布線都應該使用由 FPGA 提供的專用時鐘資源(如全局時鐘資源、局部時鐘資源和 I/O 時鐘資源),否則時鐘偏差會非常嚴重。

- 源時鐘,指發送數據的時鐘;目的時鐘,指接收數據的時鐘;

- 發送沿,指發送數據的源時鐘活動邊沿;接收沿,指接收數據的目的時鐘活動邊沿;

??在超大規模集成電路中,存在大量需要時鐘信號進行同步的寄存器,這就需要構建一個時鐘信號的分布傳輸網絡,來提供時鐘偏移盡可能小的同步時序。在集成電路的物理設計階段,需要設計一個良好的時鐘樹結構 CTS,通過在時鐘信號傳輸電路上插入具有不同時延參數的緩沖器,可以盡可能地使時鐘偏移接近零,即時鐘信號近乎同步到達各個寄存器。

-

寄存器

+關注

關注

31文章

5317瀏覽量

120003 -

緩沖器

+關注

關注

6文章

1917瀏覽量

45450 -

時鐘

+關注

關注

10文章

1720瀏覽量

131362 -

時鐘抖動

+關注

關注

1文章

62瀏覽量

15917 -

布線

+關注

關注

9文章

766瀏覽量

84292

發布評論請先 登錄

相關推薦

正確理解時鐘器件的抖動性能

談談非理想時鐘的時鐘偏差

FPGA如何消除時鐘抖動

時鐘抖動與相位噪聲的關系

時鐘抖動和時鐘偏移的區別

抖動的概念和類型 量化時域抖動、隨機抖動和頻域抖動的方法

時鐘偏差和時鐘抖動的相關概念

時鐘偏差和時鐘抖動的相關概念

評論