概述

本文主要介紹一種基于FPGA的FT232H接口通信開發方案。傳統的USB通信開發對工程人員的要求比較高,除了上層應用軟件以外,還需要掌握一定的USB傳輸協議、固件編程以及底層驅動等等。對于FPGA固件開發人員來說,我只關心數據如何可以正確的收發,說白了就是給我說清楚接口交互時相關信號之間的時序關系即可,其他的內容并不是這么關心。FTDI公司的FT232H應運而生,他把USB的相關協議封裝在芯片內部,只把數據端口部分開發給工程開發人員。與市面上另外一款USB芯片(cypress的CY7C68013)相比,FT232H在模式配置上,有官方提供的工具軟件直接進行模式配置,而不需要像前者那樣,還要編寫模式配置的相關代碼,從而大大提高開發效率。

接口芯片FT232H

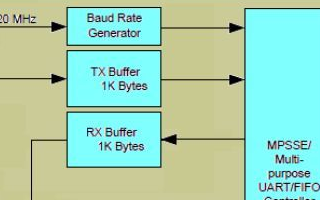

FT232H是一款單通道的高速USB轉UART/FIFO芯片,支持USB2.0協議。通過配套的軟件可以配置成不同的應用模式,如下圖所示:

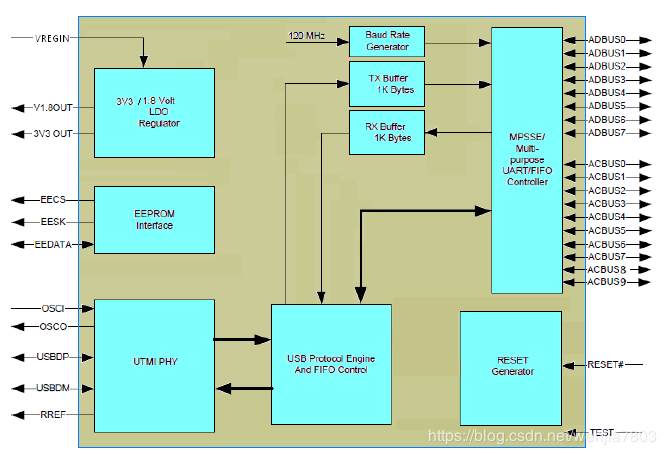

FT232H的內部結構

從圖1中我們可以了解到,FT232H芯片內部可以劃分為UTMI_PHY、USB_protocol and FIFO ctrol、Tx/Rx Buffer、MPSSE/Multi_purpose UART/FIFO controler以及EEPROM_interface這幾部分。其中MPSSE/Multi_purpose UART/FIFO controler是面向用戶設計的IO,通過配置成不同的模式,管腳對應的定義不一樣。

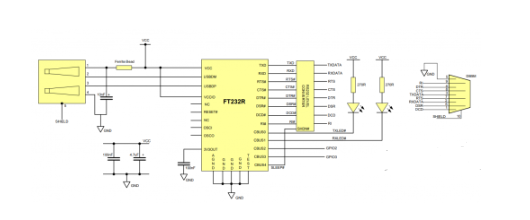

我們通過把FT232H配置成同步FIFO模式,已達到最快的傳輸速率。

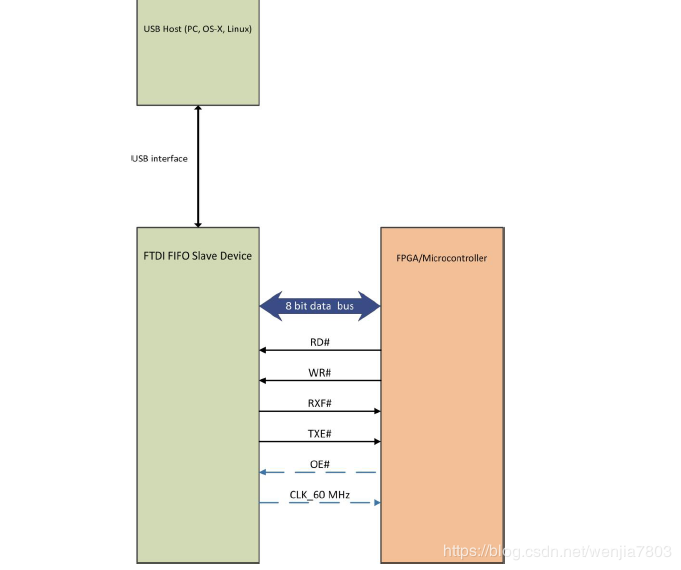

FIFO模式下的拓撲結構

軟件設計

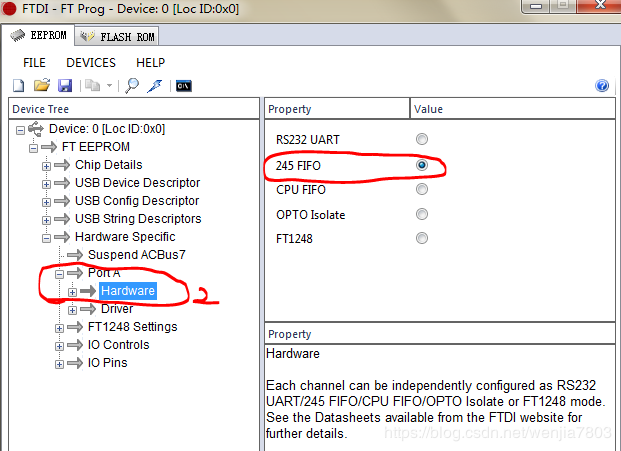

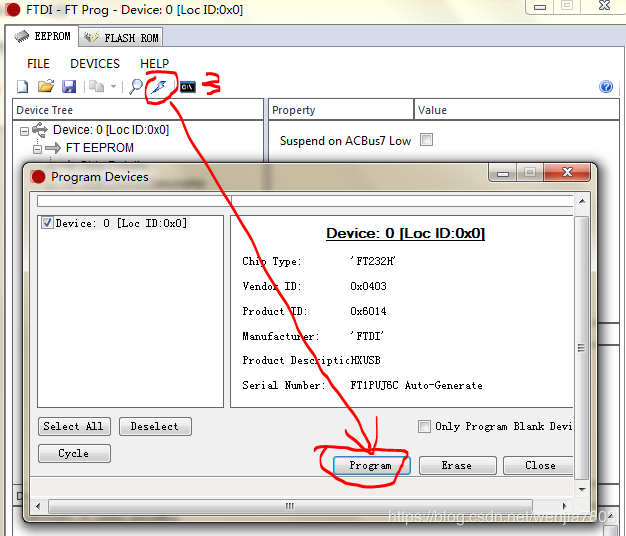

芯片工作模式配置

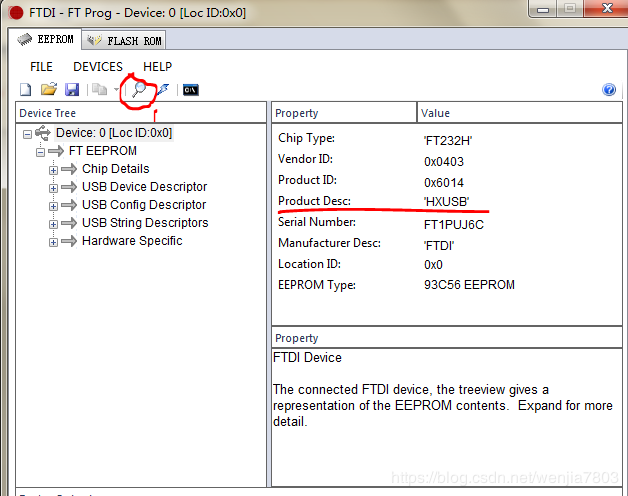

FT232H在出廠的時候,默認是UART模式,配置長同步FIFO模式,需要通過官方提供的配置軟件FT_PROG進行配置,配置過程十分簡單,如下:

如上圖所示,配置過程大體上可以分為上述3個步驟。需要注意的是在進行第一步之前,PC上需要安裝好相應的驅動,才能夠識別出芯片;還有一個需要注意的地方是,Property中product_desc里面的值可以自己修改,但是上位機一定要與之對應,否則編寫的上位機軟件有可能打不開設備。

代碼設計

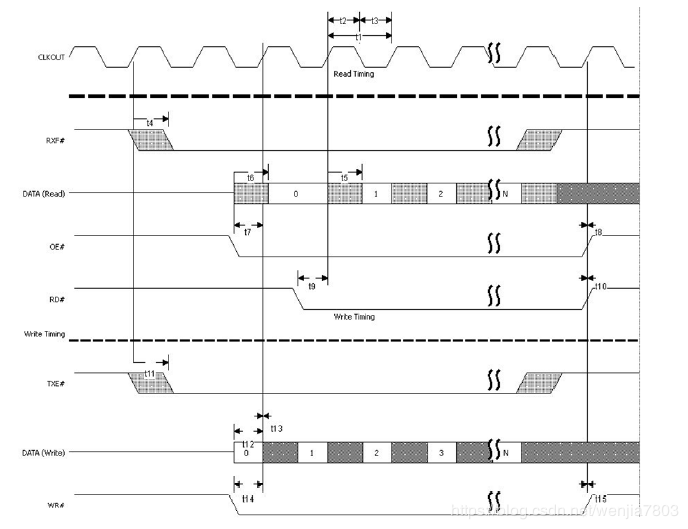

同步FIFO模式下的讀寫時序關系

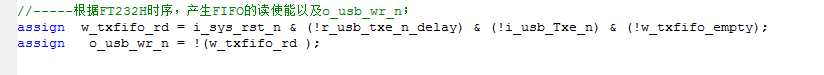

發送端(FPGA--->USB--->PC)

通常來說,為了處理好異時鐘域數據傳輸問題,都會在FPGA端例化一個FIFO來作為與USB接口交互的緩存。在數據發送有個需要注意的地方,當發送速率比USB傳輸速率快,FT232H內部緩存被填滿的時候(TXE#被拉高),會出現丟數據情況。在處理的時候需要特別注意一下。

我們畫一下相關時序就知道怎么回事了。

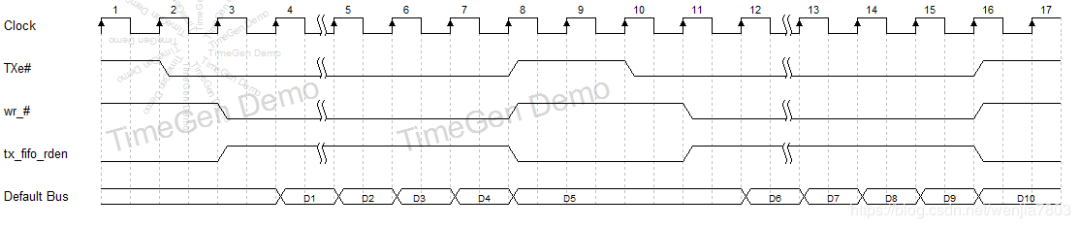

FIFO常規模式下時序圖

從圖中可以看出,FIFO的讀使能持續了5個clk,由于FIFO的輸出最少都有1個clk的延遲,所以這次數據傳輸只傳輸了4個有效數據,剩下一個數據只能由下一次傳輸,當然這種情況,在傳輸流式的數據是沒有問題的,碰上我之前的項目,讀寫由上位機發起,并且讀寫的數據長度也由上位機決定的時候,就會出現上位機會少接收一個數據的現象。

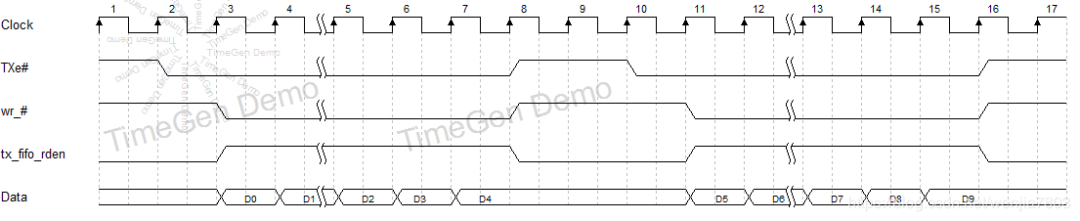

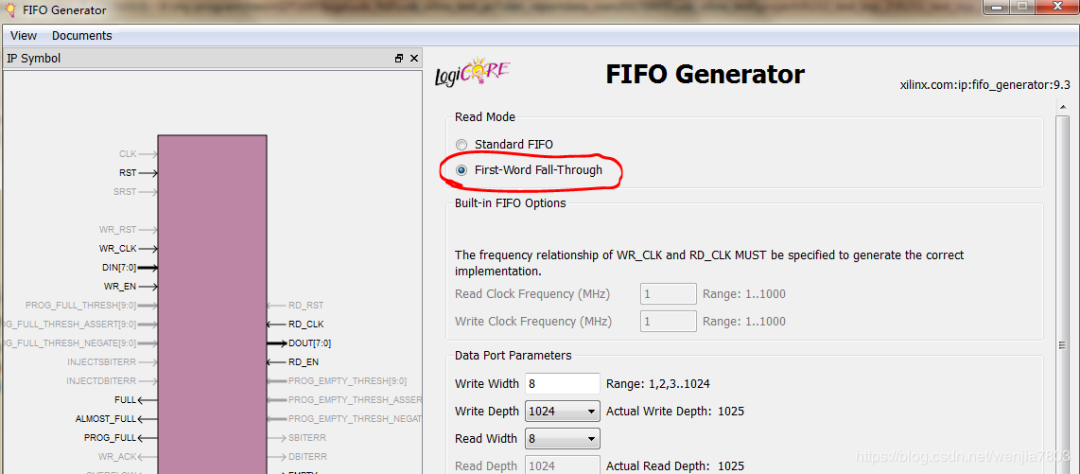

那么有沒有辦法解決這種現象呢?答案是肯定的,我比較推薦的一種方法如下:

將例化FIFO的時候,設置成First_word Fall through模式就可以了,至于這種模式是什么,請自行度娘腦補一下。

方法還有很多,只要時序對的上即可。

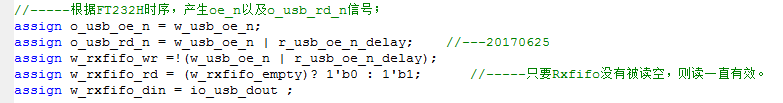

接收端(PC—>USB--->FPGA)

接收端的設計比較簡單,這里就不展開論述了。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828 -

芯片

+關注

關注

453文章

50397瀏覽量

421793 -

接口通信

+關注

關注

0文章

9瀏覽量

13392

發布評論請先 登錄

相關推薦

【紫光同創國產FPGA教程】【第二十八章】USB雙向測速例程

UM232H-B是FT232H高速到串行/并行接口轉換器的開發模塊

FT232H單通道USB至串行/并行接口分線板開發模塊UM232H-B-WE

用于FT232H單通道USB至串行/并行接口分線板的開發模塊UM232H-B-NC

采用FT245BM和FPGA實現USB接口設計

接口轉換芯片-FT232RL

PIC32MX與FTDI FT232H接口如何同步并行

用于FT232RL USB-to-UART接口的串行UART開發模塊

USB2.0高速至MPSSE SPI模塊VA800A-SPI是一個小型電子電路板

基于FT8U232BM的USB-HART通信接口的開發

基于FT232BL的USB接口快速設計

一種基于FPGA的FT232H接口通信開發方案

基于FPGA的FT232H接口通信開發方案

基于FPGA的FT232H接口通信開發方案

評論