今天我們要介紹的時序分析概念是 時序路徑 (Timing Path)。STA軟件是基于timing path來分析timing的。那什么是timing path呢?

Timing Path根據(jù)起點和終點可以分為以下四種:

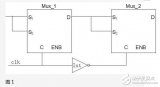

- 由Flip-Flop時鐘輸入端到Flip-Flop數(shù)據(jù)輸入端,即**reg2reg **path,如下圖1

- 由主要輸入到Flip-Flop數(shù)據(jù)輸入,即**in2reg **path,如下圖2

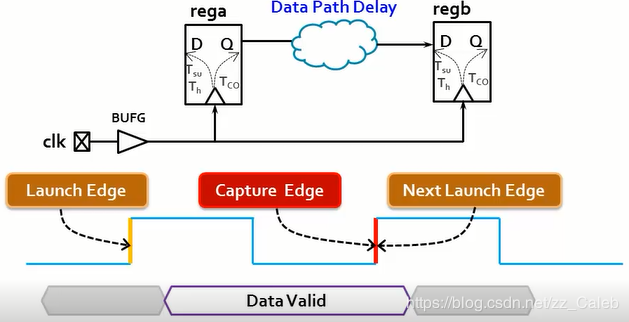

- 由Flip-Flop時鐘輸入端到主要輸出,即**reg2out **path,如下圖3

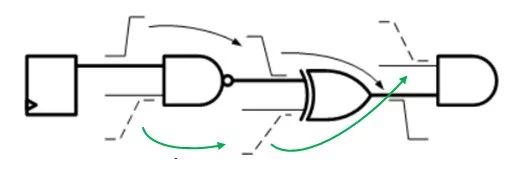

- 由主要輸入到主要輸出,即**in2out **path,如下圖4

圖1

圖2

圖3

圖4

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22551 -

STA

+關(guān)注

關(guān)注

0文章

51瀏覽量

18945 -

時序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5271 -

時序路徑

+關(guān)注

關(guān)注

0文章

12瀏覽量

1394

發(fā)布評論請先 登錄

相關(guān)推薦

【時序約束】關(guān)于設(shè)置FALSE PATH

總得來說,F(xiàn)ALSE PATH就是我們在進(jìn)行時序分析時,不希望工具進(jìn)行分析的那些路徑。一般不需要工具時序分析的路徑指的是異步的

發(fā)表于 06-27 06:34

Vivado下顯示指定路徑時序報告的流程

Vivado運(yùn)行Report Timing Summary時,只顯示各個子項目最差的十條路徑,很可能并不包含你最關(guān)心的路近,這個時候顯示指定路徑的時序報告就顯得很重要了,下面就簡單

發(fā)表于 01-15 16:57

Timing Groups and OFFSET Const

Timing Groups and OFFSET Constraints:

•Use the Constraints Editor to create groups of path

發(fā)表于 01-11 08:55

?4次下載

Path-Specific Timing Constrain

Path-Specific Timing Constraints:Constraining Between Risingand Falling Clock Edges•

發(fā)表于 01-11 08:56

?10次下載

基于FALSE PATH的設(shè)置

總得來說,F(xiàn)ALSE PATH就是我們在進(jìn)行時序分析時,不希望工具進(jìn)行分析的那些路徑。一般不需要工具時序分析的路徑指的是異步的

發(fā)表于 09-19 10:46

?0次下載

靜態(tài)時序分析基礎(chǔ)與應(yīng)用

STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設(shè)計者給定的時序限制(Timing Constraint)。以分析的方式區(qū)分,可分為

發(fā)表于 04-03 15:56

?10次下載

如何判斷路徑的timing exception約束

隨著設(shè)計復(fù)雜度和調(diào)用IP豐富度的增加,在調(diào)試時序約束的過程中,用戶常常會對除了自己設(shè)定的約束外所涉及的繁雜的時序約束感到困惑而無從下手。舉個例子,我的XDC里面并沒有指定set_false_path

AOCV時序分析概念介紹

今天我們要介紹的時序分析概念是 **AOCV** 。全稱Stage Based Advanced OCV。我們知道,在OCV分析過程中,我們會給data path,clock path上設(shè)定單一的

什么是時序路徑timing path呢?

什么是時序路徑timing path呢?

評論