引言

靜態時序分析(STA)是用來分析數字電路是否滿足時序目標的技術手段之一。比如,檢查CPU電路是否達到1GHz的目標頻率。

本文沒有目錄分類,而是想先快速的講完一個案例,然后再回個頭來慢慢引出一些STA概念和知識,以便后面進行分類講解。(ps.這個時候出現的STA專業術語只需有個印象即可。)

案例分析

某芯片回片測試發現功能異常,不符合預期。經過設計人員層層排查,鎖定到某條嫌疑路徑。我們畫出幾組精簡的邏輯電路圖和時序波形圖來示意解釋問題出在哪。

該電路不是真實案例對應的具體電路,而是為了說明問題,虛擬抽象出來的相似電路,它不影響我們對問題的探究剖析。

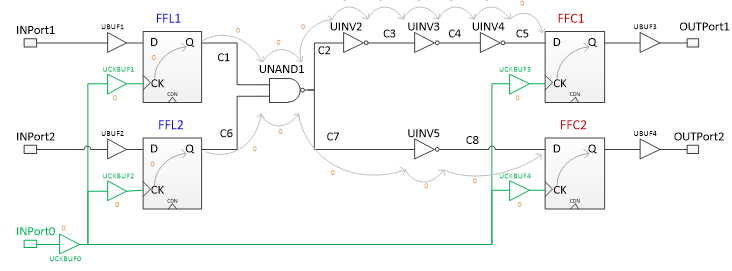

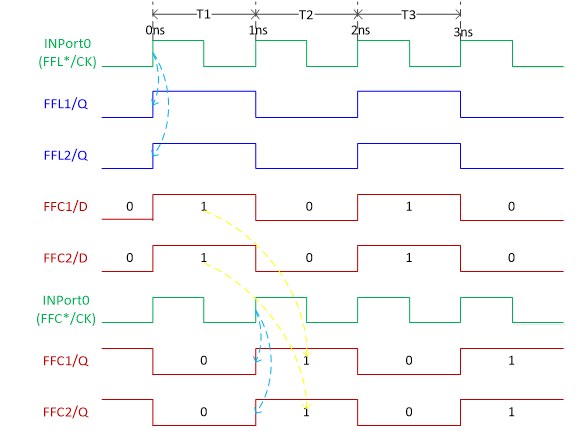

圖一、圖二是數字電路前端設計人員熟悉的邏輯電路圖和時序波形圖,其中時序波形圖代表了該邏輯電路的預期功能。

圖一 邏輯電路圖(理想延遲)

圖二 時序波形圖(理想延遲)

可以看出:

在0ns時刻之前

FFL1、FFL2兩個寄存器儲存的邏輯值分別是0、0。

在0ns時刻時

FFL1、FFL2打出來新的邏輯值1、1,經過邏輯運算和路徑傳播后,到達FFC1、FFC2的D端。

在1ns時刻時

FFC1、FFC2的D端出現的1、1分別被捕獲鎖存進寄存器FFC1、FFC2,即T2周期FFC1、FFC2寄存器儲存的邏輯值是上個周期(T1)的D端輸入值。

實際芯片中,信號經過任何cell和wire都是有延遲的。而且芯片處在不同的工作環境下,這些cell和wire會有不同的延遲值。

因此在不影響問題說明的前提下,為了近一步降低理解難度,我們先假設從clock源頭到任何寄存器的時鐘輸入端的延遲是0ns,而且假設不同工作條件下信號經過同一條wire網絡具有相同的延遲值。

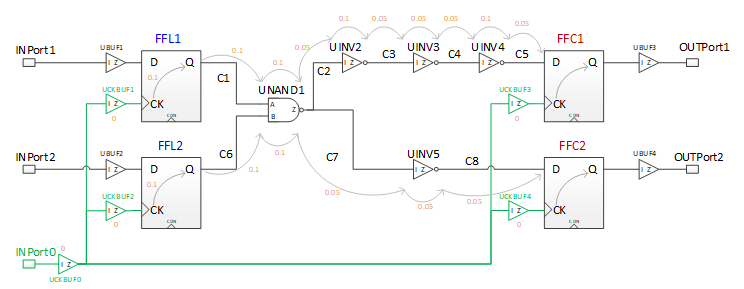

圖三、圖四是在BC工作條件下的邏輯電路圖(含延遲信息)和時序波形圖:

圖三 邏輯電路圖(含BC工作條件下的延遲信息)

圖四 時序波形圖( BC****工作條件)

在0ns時刻之前

FFL1、FFL2兩個寄存器儲存的邏輯值分別是0、0。

在0ns時刻時

FFL1、FFL2打出來邏輯1、1,這兩個輸出的邏輯值經過路徑UNAND1、UINV2、UINV3、UINV4的邏輯運算后到達FFC1的D端。

其路徑延遲 = 經過的cell延遲 + 經過的wire延遲,即:

路徑延遲D(FFL1->FFC1) = D(FFL2->FFC1)

= D(FFL1CP2Q) + D(C1) ~ ~ + D(UNAND1) + D(C2) + D(UINV2) + D(C3) + D(UINV3) + D(C4) + D(UINV4) + D(C5)

= 0.1 + 0.1 + 0.1 + 0.05 + 0.1 + 0.05 + 0.05 + 0.05 + 0.1 + 0.05

= 0.75ns;

同樣,兩個輸出經過UNAND1、UINV5的邏輯運算后到達FFC2的D端,其路徑延遲為:

路徑延遲D(FFL1->FFC2) = D(FFL2->FFC2)

= D(FFL2CP2Q) + D(C6) ~ ~ + D(UNAND1) + D(C7) + D(UINV5) + D(C8)

= 0.1 + 0.1 + 0.1 + 0.05 + 0.05 + 0.05

= 0.45ns;

在1ns時刻時

由于

D(FFL1->FFC1) = D(FFL2->FFC1) = 0.75ns < Tperiod – Tsetup = 1 – 0.1 = 0.9ns,

D(FFL1->FFC1) = D(FFL2->FFC1) = 0.75ns > Thold = 0.1ns,

D(FFL1->FFC2) = D(FFL2->FFC2) = 0.45ns < Tperiod – Tsetup = 1 – 0.1 = 0.9ns,

D(FFL1->FFC2) = D(FFL2->FFC2) = 0.45ns > Thold = 0.1ns,

所以FFC1、FFC2的D端出現的1、1能可靠的分別被捕獲鎖存進寄存器FFC1、FFC2,即T2周期FFC1、FFC2寄存器鎖存了上個周期(T1)的D端輸入值。

**可見,在BC工作條件下,計算了cell和wire延遲后,電路功能依然符合預期。 **

圖五、六是在WC工作條件下的邏輯電路圖(含延遲信息)和時序波形圖。

圖五 邏輯電路圖(含WC工作條件下的延遲信息)

圖六 時序波形圖( WC****工作條件)

在0ns時刻時

FFL1、FFL2打出來邏輯1、1,這兩個輸出的邏輯值經過路徑UNAND1、UINV2、UINV3、UINV4的邏輯運算后到達FFC1的D端,其路徑延遲為:

路徑延遲D(FFL1->FFC1) = D(FFL2->FFC1)

= D(FFL1CP2Q) + D(C1) ~ ~ + D(UNAND1) + D(C2) + D(UINV2) + D(C3) + D(UINV3) + D(C4) + D(UINV4) + D(C5)

= 0.2 + 0.1 + 0.2 + 0.05 + 0.2 + 0.05 + 0.1 + 0.05 + 0.2 + 0.05

= 1.2ns;

同樣,兩個輸出經過UNAND1、UINV5的邏輯運算后到達FFC2的D端,其路徑延遲為:

路徑延遲D(FFL1->FFC2) = D(FFL2->FFC2)

= D(FFL2CP2Q) + D(C6) ~ ~ + D(UNAND1) + D(C7) + D(UINV5) + D(C8)

= 0.2 + 0.1 + 0.2 + 0.05 + 0.1 + 0.05

= 0.7ns;

在1ns時刻時

與前面兩種情況不同,在這種場景下,在1ns時刻時出現在FFC1、FFC2的D端的是0、1(上面場景出現的是1、1)。

因此,此時鎖存進FFC1、FFC2寄存器的值分別是0、1。與我們所預期的T2周期FFC1、FFC2寄存器值是1、1不同。

至此,芯片功能測試異常的原因我們已經找到。簡單的說即芯片中去往FFC1的D端的這2條路徑(沒看錯,是2條),在實際運行場景中的某個時刻,恰好處于接近WC的工作條件,導致FFC1在某時刻采樣錯誤,表現出來芯片功能異常。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42580 -

寄存器

+關注

關注

31文章

5317瀏覽量

120013 -

STA

+關注

關注

0文章

51瀏覽量

18945 -

靜態時序分析

+關注

關注

0文章

28瀏覽量

9572 -

ffc連接器

+關注

關注

1文章

12瀏覽量

8404

發布評論請先 登錄

相關推薦

[MATLAB智能算法30個案例分析].史峰等.掃描版

從一個賬號開始玩轉機智云(應用構建)

HLS系列 – High Level Synthesis(HLS) 從一個最簡單的fir濾波器開始4

STA分析-從一個案例開始

STA分析-從一個案例開始

評論