LDO之所以不好做,很大一部分原因是穩定性的鍋。不同的架構能影響穩定性,負載的性質和大小能影響穩定性,功耗也能影響穩定性,還有其他各種因素都能限制系統穩定性的設計...這家伙可真的是對內唯唯諾諾,對外重拳出擊,一不小心就設計成OSC了。

1. 兩級miller補償

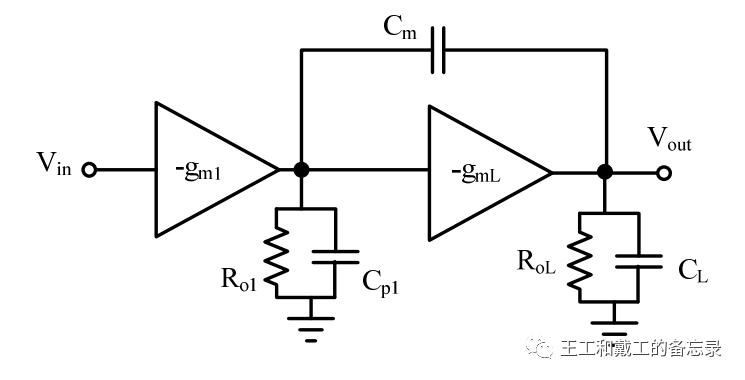

要分析穩定性,各種補償方式和對應的零極點分析是逃不過的一個難題。從上學開始接觸最多的就是兩級的miller補償,主極點在第一級運放的輸出,次級點在系統的輸出,但這也僅限于Cm和CL在同一個數量級時,如果CL>>Cm那么主極點將在系統輸出,次級點在第一級運放的輸出。這時候用miller補償,Cm需要非常大。

所以兩級miller補償好用,但是如果負載電容很大時這種補償方式很不實用。現在很多單片LDO包括有些大芯片內部的PMU應用時輸出外面都會掛一個uF級的大電容,這樣可以在輸出負載跳變時穩定輸出電壓,也可以濾除噪聲。所以在設計LDO時都需要把外面的大電容考慮進去。

LDO的穩定性補償還需要考慮不同負載電流下的穩定性。LDO多用于系統的供電源,所以需要在重載,輕載和空載下都要保持穩定。但是LDO讓人頭疼的就是負載變化時,系統輸出處的極點也會隨之變化。比如還是兩級LDO,假設主極點p1在第一級輸出,次級點p2在系統輸出。p1=1/Ro1CmgmL*RoL,p2=gmL/CL。gmL是跟負載電流iload有關的量,如果iload減小gmL也會減小。對應的p1和帶寬會增大,p2會減小,最壞會在帶內形成雙級點影響穩定性,所以一般都會做一個動態零點補償架構來消除負載變化帶來的影響。

2. 三級級聯補償

下面的架構是一種三級補償方式,這種可以不用miller補償的方式來實現穩定性。假設Co是uF級的負載電容。主極點Po在系統輸出,p1和p2分別為系統另外兩個次級點。增加一個零點來補償帶寬處的穩定性。這種架構優缺點都很明顯,如果把p1和p2做到帶外那么系統為單極點的穩定系統,且也不用考慮負載變化帶來的影響。但是系統帶寬不能太高,如果帶寬太高,p1和p2會很難設計到帶外去。太低的話瞬態效應會不好。

3. Ahuja miller compensation

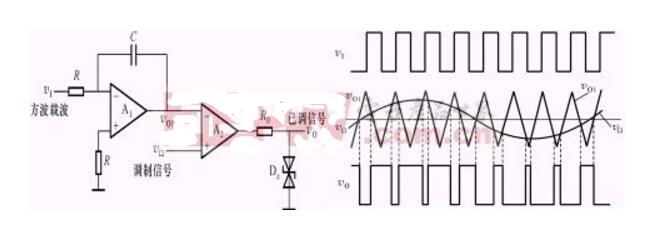

下面也是一種很經典的補償架構:ahuja miller compensation。這種補償方式將主極點往原點死推,Cc會經過兩個增益級,將Cc的等效容值倍增兩個增益級,主極點p1=1/Ro5Ccgmp*RL,次級點p2=gmp/CL,就算輸出外掛一個uF級的大電容,理論上也很容易實現單極點穩定系統。但是在實際做時很容易在帶寬處出現共軛極點,導致穩定性問題。不知道有經驗的大佬對此有沒有具體的分析方法和解決思路可以在評論區分享一下,在此托馬斯回旋跪謝!

4.reverse nested miller compensation

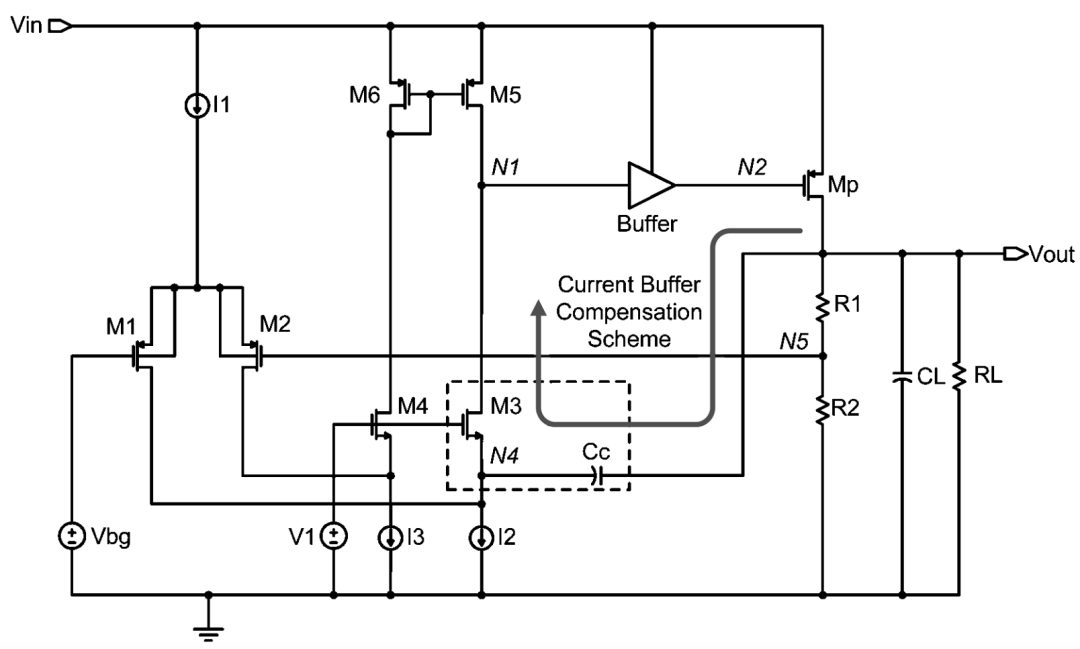

下面的架構是一種很好很實用的架構,reverse nested miller compensation。跟ahuja的思路一樣,嵌套補償的方法也是讓主密勒補償電容Cc1經過兩級增益級,以此來提高等效容值,把主極點p1往原點死推。P1=1/Cc1Av2Av3*Ro1; P2=1/Ro2*Co2; P3=gm3*Cc2/Cc1*CL。所以把p2和p3做到帶外就能形成單極點穩定系統。這種架構還需要設計一個動態零點來補償掉輕載和空載時帶寬處的相位裕度。

值得注意的是,因為p3會隨著負載變化,所以在某個負載下很容易跟內部的p2形成共軛極點。在根軌跡上當兩個極點相遇,如果負載繼續變化,兩個極點會向原點移動,影響系統的穩定性。

-

LDO電源

+關注

關注

0文章

62瀏覽量

10447 -

PMU

+關注

關注

1文章

108瀏覽量

21569 -

負載電容

+關注

關注

0文章

138瀏覽量

10430 -

LDO控制

+關注

關注

0文章

5瀏覽量

1578

發布評論請先 登錄

相關推薦

低壓電網中有哪幾種無功補償的方式

光纖通信中溫度場調諧的實現方式及色散補償器的研究介紹

pwm調制原理同步調制_幾種pwm調制方式介紹

介紹幾種LDO的補償方式

介紹幾種LDO的補償方式

評論