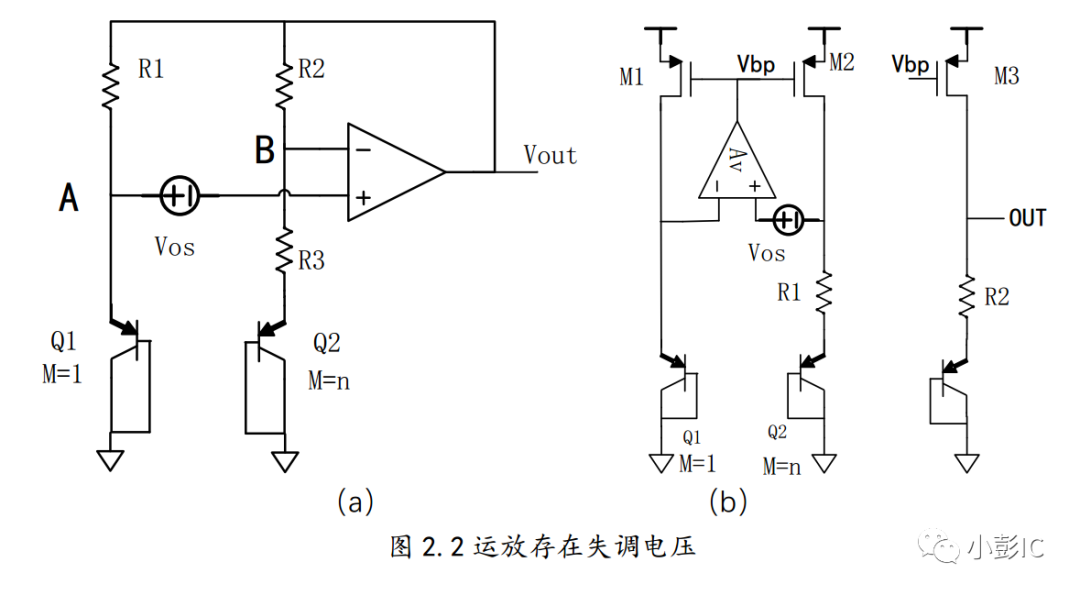

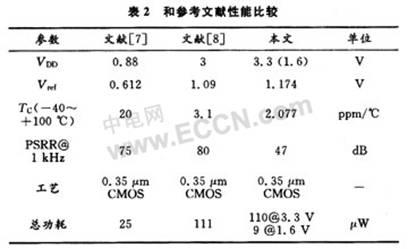

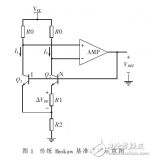

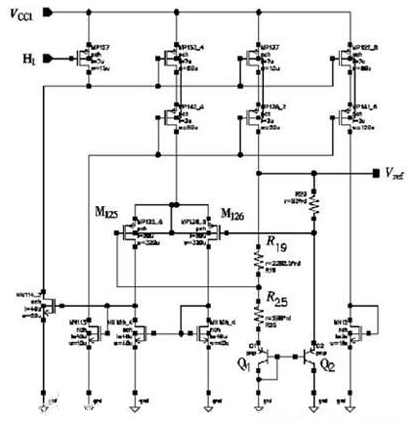

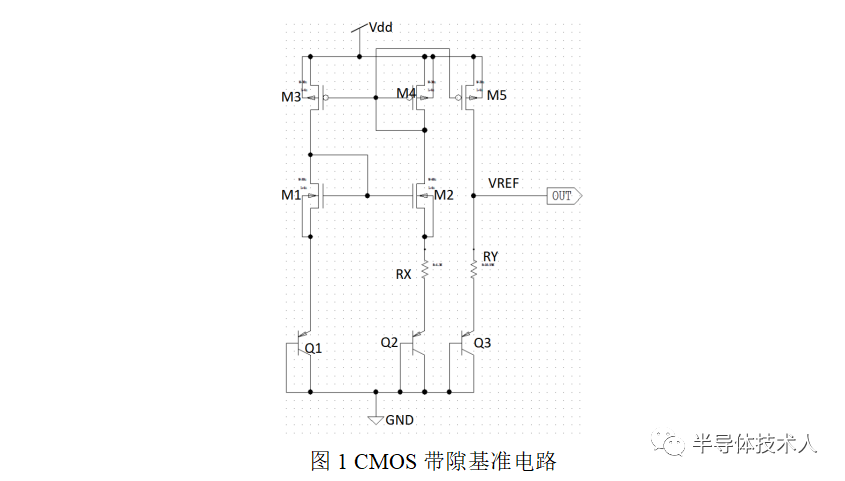

如圖2.2(a)是兩種常見的bg結構,對于這兩個bg模塊的輸出電壓誤差來源:

- 60%來自于運放的offset

- 30%來自于prosess

- 10%來自于mismatch(對于2.2(a)是R1和R2、2.2(b)指的是M1和M2)

以上為其電路設計師的經驗數據,僅供參考。

EA的offset是影響bg誤差的主要因素,本文只計算EA的offset對bg的影響

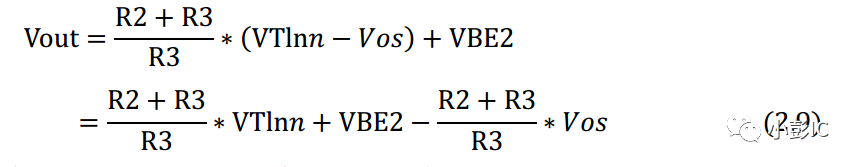

對于圖 2.2(a)(忽略失調電壓給兩個三極管造成的電流誤差)

假設 VBE 的溫度系數絕對值是 VT 溫度系數的 K 倍,也就是

式2.9就可以表示成:

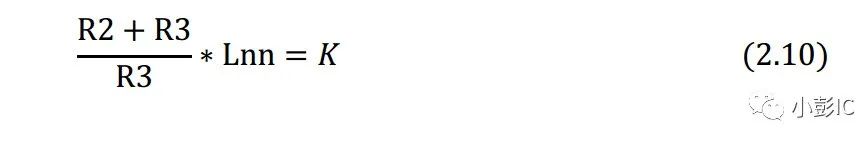

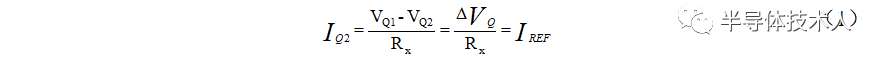

對于圖 2.2(b)(忽略M1和M2電流鏡的電流誤差)

根據2.13和式2.11,可以得到結論(實際上是片面結論):

同樣的EAoffset,對bg的輸出電壓影響一樣(實際上是錯誤的)

下面來分析并通過仿真證明錯誤的

由于本系列文章沒有分析bg的工作原理所以在這里補充(如有需要歡迎留 言):

bandgap電路的兩個主要前提條件是

- 兩個pnp的電流完全相同

- 運放的輸入兩點也就是(a)圖的A點和B點電壓完全相同

對于(a)(b)兩幅圖

如果不考慮每路電流的失配, 運放失調電壓的影響對于以上兩種拓撲結構的影響是一樣的,如果考慮電流失配呢?直觀感受是 (a)圖的運放除了運放的角色,還擔任電流鏡的角色,所以(a)圖的運放失配還會影響 BG 的溫度曲線。

仿真電路以及仿真結果:

在沒有手動加入失調電壓Vos的時候,設置好兩幅圖的其他工作條件相同(工作點、系統誤差、pnp個數以及比例、并設置好電阻比例)

圖(a)

仿真結果

如果不考慮電流的失配,兩種結構運放的 Vos 對 bgv 的影響一樣,已經通過計算證明。但要考慮圖 2.2(a)Vos 引起的電流失配, Vos 還會影響 bgv 的溫度曲線,如圖2.3 紅色的曲線,可知 2.2(a) Vos 對的 bgv 的影響較大,也會改變 bg 的溫度曲線。

失調電壓結論 :

圖 2.2(b) Vos 只對 bgv 的值有影響,沒有影響 bgv 的溫度曲線的形狀,圖 2.2(b), 不僅對 bgv 的值有影響,也影響了 bgv 的溫度曲線形狀。

-

三極管

+關注

關注

142文章

3600瀏覽量

121653 -

電流鏡

+關注

關注

0文章

44瀏覽量

17269 -

輸出電壓

+關注

關注

2文章

1092瀏覽量

38024 -

帶隙基準電路

+關注

關注

0文章

14瀏覽量

10718 -

PNP管

+關注

關注

1文章

28瀏覽量

7418

發布評論請先 登錄

相關推薦

低溫漂CMOS帶隙基準電壓源分析

14位Pipeline ADC設計的帶隙電壓基準源技術

CMOS帶隙基準電壓源曲率校正方法

帶隙電壓基準源的設計與分析

帶隙基準電壓模塊之EA offset影響分析

帶隙基準電壓模塊之EA offset影響分析

評論