今天我們要介紹的時序基本概念是 Timing arc ,中文名時序弧。這是timing計算最基本的組成元素,在昨天的lib庫介紹中,大部分時序信息都以Timing arc呈現。如果兩個pin之間在timing上存在因果關系,我們就把這種時序關系稱為Timing arc,主要分為定義時序延遲,和定義時序檢查兩種。為啥叫它時序弧?因為時序圖中經常用一條弧形線段來表示它。如下圖所示:cell的timing arc定義在lib中,net之間沒有timing arc, 它的delay則有RC參數計算而出。

時序延遲的Timing arc :有以下幾種

Combinational Timing Arc

Edge Timing Arc

Preset and Clear Timing Arc

Three State Enable & Disable Timing Arc

時序檢查的Timing arc :有以下幾種

Setup Timing Arc

Hold Timing Arc

Recovery Timing Arc

Removal Timing Arc

Width Timing Arc

首先看 Combinational Timing Arc ,Combinational Timing Arc 是最基本的Timing Arc。Timing Arc 如果不特別指明的話,就是屬于此類。如下圖所示,定義了從特定輸入到特定輸出(A到Z)的延遲時間。

Combinational Timing Arc 的Sense有三種,分別是 inverting (或 negative unate), non-inverting (或 positive unate)以及 non-unate 。當Timing Arc 相關之特定輸出(下圖Z)信號變化方向和特定輸入(下圖A)信號變化方向相反(如輸入由0變1,輸出由1變0),則此Timing Arc 為inverting sense。

反之,輸出輸入信號變化方向一致的話,則此Timing Arc 為non-inverting sense。當特定輸出無法由特定輸入單獨決定時,此Timing Arc 為non-unate。

其它的Timing Arc 說明如下。

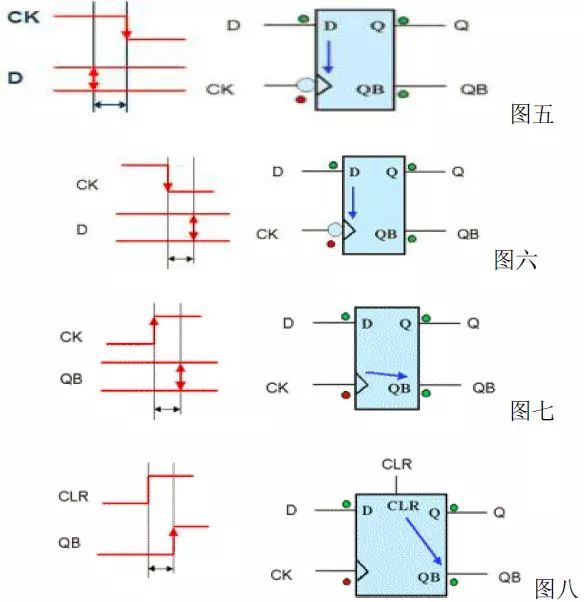

Setup Timing Arc :定義時序組件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time,依據Clock上升或下降分為2類(圖五)。

Hold Timing Arc :定義時序組件所需的 Hold Time,依據Clock 上升或下降分為2類(圖六)。

Edge Timing Arc :定義時序組件Clock Active Edge 到數據輸出的延遲時間,依據Clock上升或下降分為2類(圖七)。

Preset and Clear Timing Arc :定義時序組件清除信號(Preset或Clear發生后,數據被清除的速度,依據清除信號上升或下降及是Preset或Clear分為4類(圖八)。這個Timing Arc 通常會被取消掉,因為它會造成信號路徑產生回路,這對STA而言是不允許的。

Recovery Timing Arc :定義時序組件Clock Active Edge 之前,清除信號不準啟動的時間,依據Clock上升或下降分為2類(圖九)。

Removal Timing Arc :定義序向組件Clock Active Edge 之后,清除信號不準啟動的時間,依據Clock上升或下降分為2類(圖十)。

Three State Enable & Disable Timing Arc :定義 Tri-State 組件致能信號(Enable)到輸出的延遲時間,依據Enable或Disable分為2類。(圖十一)

Width Timing Arc :定義信號需維持穩定的最短時間,依據信號維持在0或1的位準分為2類。(圖十二)

-

時序分析

+關注

關注

2文章

127瀏覽量

22551 -

ARC

+關注

關注

0文章

42瀏覽量

16460 -

STA

+關注

關注

0文章

51瀏覽量

18945 -

時序分析器

+關注

關注

0文章

24瀏覽量

5271

發布評論請先 登錄

相關推薦

時序分析基本概念介紹—Timing Arc

時序分析基本概念介紹—Timing Arc

評論