引言

SDC是一個設計從RTL到netlist的橋梁,是FE/ME/BE都需要掌握的一項基本技能。通常情況來說,由前端工程師(designer)提供SDC文件是最合理的,因為只有designer才是最了解整個設計的結構的,所以最能夠合情合理的提供出約束文件,但是,ME/BE又必須要能夠看得懂,因為只有這樣,在做綜合和PR以及timing signoff的時候,在遇到問題時能夠最快的定位timing問題的合理性。所以,接下來連續更新的文章,會從基礎到深入,并結合實例的方式,跟大家一起探討一下SDC的各種語法構成和整體結構,最終達成的目標就是每個人能夠獨立完整的提供合理的約束文件。

基礎介紹

SDC全稱是Synopsys Design Constraints Format,是由S公司最早提出的一種約束文件格式。主要用于指定design內部的Timing關系,約束Power消耗和Area大小。但是在這當中,最為關鍵的便是指定design的時序。其語法結構是基于TCL語法實現的。主要應用于綜合、PR、以及STA過程當中,當然在其他方面也會有很大用途,比如CDC check。現在的SDC可以看做是一項標準的指令系統,基本上所有的EDA工具都可以兼容性識別。

tools行為簡介

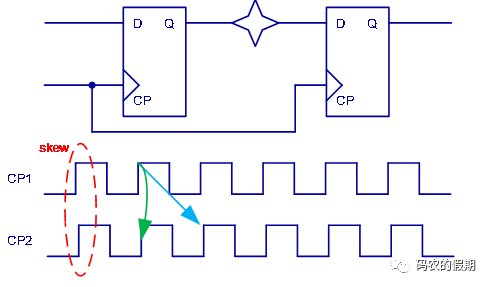

要想知道怎么約束一個design,我們首先需要清楚的知道,工具的行為是如何的。如圖1所示,我們design通常情況下都是同步結構的設計,tools在做timing分析的時候,會將design中所有的path都抽象成這樣前后兩級DFF的結構。并將前一級的DFF作為source register,也稱作launch register,將后一級的register作為destination register,也稱作capture register。如果check setup,tools的默認行為是從launch DFF的當前觸發沿到capture DFF的下一個觸發沿之間的時間,如圖中藍色箭頭所示。而check hold timing,tools的默認行為是從launch DFF的當前觸發沿到capture DFF的當前觸發沿之間的時間,如圖中綠色箭頭所示。

圖1 design中的基本timing path

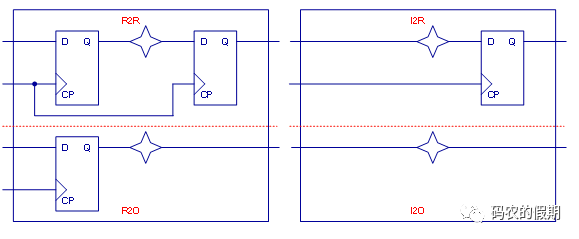

所以,要想讓tools能夠自動的check到design中的所有path的setup/hold。就需要保證design中所有的path都可以抽象成這種R2R的結構。而通常情況下,所有的design,在抽象之后,其timing path都可以抽象為圖2中示例的四種結構,分別是R2R,R2O,I2R,I2O。那現在問題來了,圖中的R2R的結構,是符合工具自動check timing的行為(當然,這里前提是clock定義好了);但是另外的三種結構,是不符合工具自動check timing的行為的。所以這就需要我們自己去構造出符合工具行為的path。

圖2 design結構抽象

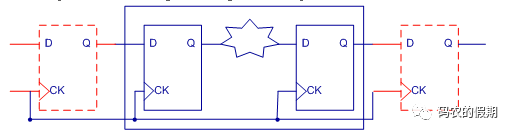

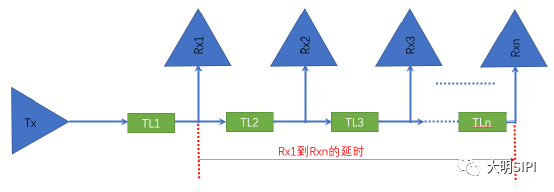

如圖3所示,對于另外的三種path,我們需要做的就是在整個design的輸入端、輸出端分別虛擬一級DFF,如圖中紅色虛線register所示。這樣,無論哪種結構(I2R/R2R/R2O/I2O),在工具看來都有了完整的launch DFF和capture DFF,從而就能夠自動的完成timing check。

圖3 timing path構造

我們虛擬構造前后級register的過程,其實就是我們SDC中,設置input delay、output delay的過程。

SDC構成分析

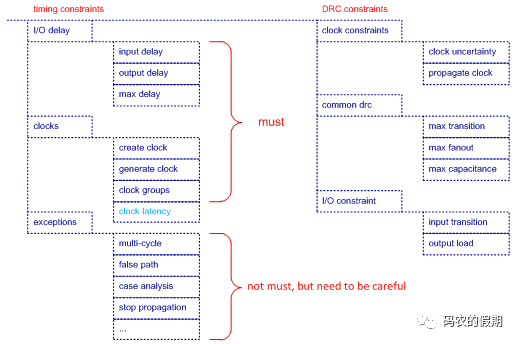

通過上面的分析,我們可以知道,對于一個design,我們需要設置input/output delay約束以構造前后兩級虛擬register。當然,要設置input/output delay,我們首先需要完成clock的定義;除此之外,我們整個design當中還有很多path,我們不想讓工具完全按照自己的行為去做timing分析,因此還需要設置一些timing exceptions;最后工具能夠完成這種自動timing check的過程,還需要我們提供一些DRC相關的約束。因此,總結之后,整個SDC結構可以劃分為兩大類,如圖4所示,其中一類是timing constraints,實現對design的timing約束;另一類是DRC constrains,實現對tools DRC方面的約束。當然,此劃分也是按照我自己的理解來做的,不同的方面來看,可以做出不同種類的劃分。

圖4 SDC構成

圖中timing constrains是最為關鍵的一部分,最好是由FE(即designer)提供,DRC constraints可以ME/BE或者timing signoff的相關人員,結合經驗來提供具體約束。圖中must部分,是每個SDC文件中基本上必須要有的,另外not must部分,通常情況下也是肯定存在的,并且這一部分約束通常會放松tools對timing的check,因此一定要謹慎…

-

EDA工具

+關注

關注

4文章

264瀏覽量

31715 -

RTL

+關注

關注

1文章

385瀏覽量

59706 -

DRC

+關注

關注

2文章

148瀏覽量

36128 -

虛擬機

+關注

關注

1文章

908瀏覽量

28096 -

SDC

+關注

關注

0文章

48瀏覽量

15528

發布評論請先 登錄

相關推薦

探討一下SDC的各種語法構成和整體結構

探討一下SDC的各種語法構成和整體結構

評論