目標

本實驗活動旨在通過構建說明性示例來探討模數轉換的概念。

背景信息

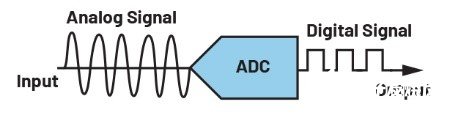

模數轉換器(ADC)將模擬信號——即溫度、壓力、電壓、電流、距離或光強度等實際信號——轉換為該信號的數字表示。然后,系統(tǒng)可以處理、控制、計算、傳輸或存儲此數字表示。

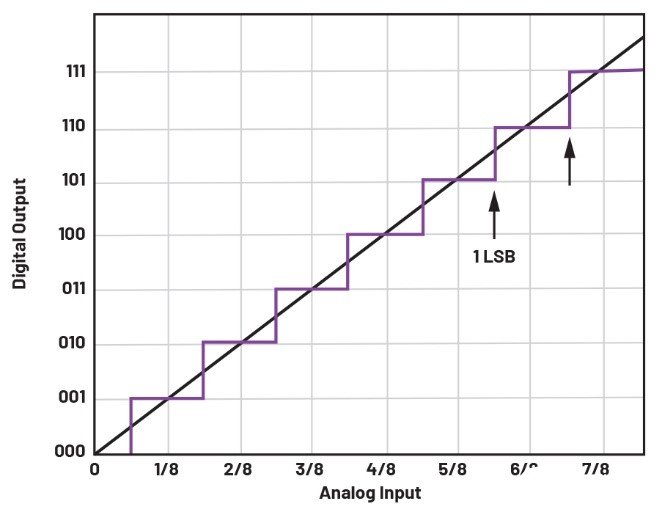

圖1.模數轉換

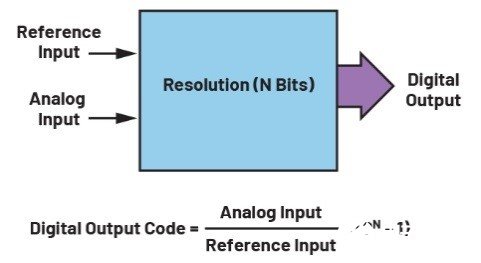

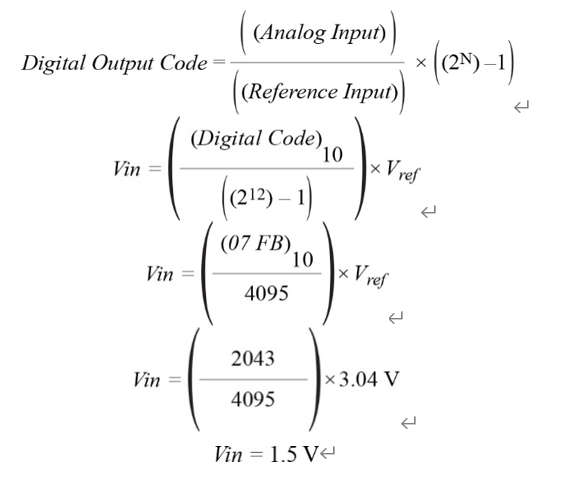

ADC以均勻的時間間隔對模擬波形進行采樣,并將數字值分配給每個樣本。數字值以二進制編碼格式在轉換器的輸出端顯示。通過將采樣模擬輸入電壓除以基準電壓,再乘以數字碼數得到此值。轉換器的分辨率由輸出碼中的二進制位數來設定。

圖2.數字輸出碼

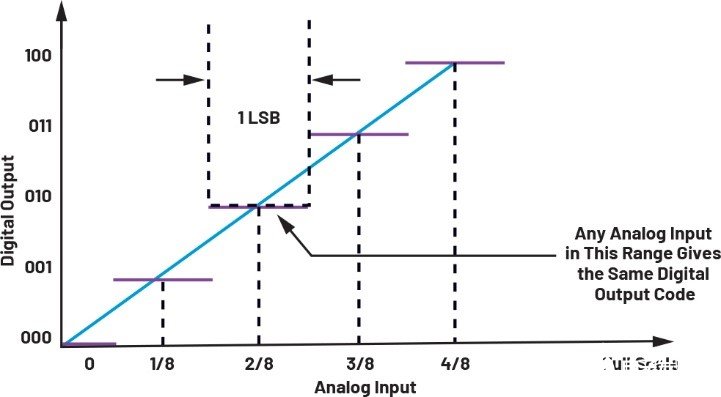

ADC執(zhí)行兩個過程:采樣和量化。ADC將無限分辨率的模擬信號表示為有限分辨率的數字碼。ADC會產生2N個數字值,其中N表示二進制輸出位數。由于轉換器的分辨率有限,模擬輸入信號將落在量化電平之間,從而導致固有的不確定性或量化誤差。該誤差可確定轉換器的最大動態(tài)范圍。

圖3.量化過程

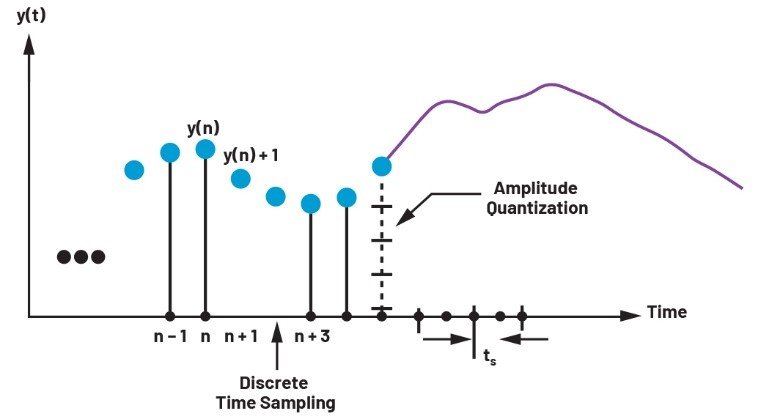

采樣過程提供連續(xù)時域信號,信號值以離散、均勻的時間間隔測量。通過此過程,根據奈奎斯特準則可確定采樣信號的最大帶寬。該理論認為,信號頻率必須小于或等于一半采樣頻率以防混疊。混疊是指通過采樣過程,目標帶寬內出現(xiàn)所需信號頻段之外的頻率信號的情況。不過,在通信系統(tǒng)設計中,可利用此混疊過程將高頻信號向下轉換為低頻信號。這就是欠采樣技術。欠采樣的標準就是ADC具有足夠的輸入帶寬和動態(tài)范圍來采集最高目標頻率信號。

圖4.采樣過程

采樣和量化都是重要的概念,因為它們確定了理想ADC的性能極限。在一個理想ADC中,碼躍遷恰好相距1 LSB(最低有效位)。因此,對于一個N位ADC,共有2N個數字碼,且1 LSB = FS/2N,其中FS為滿量程模擬輸入電壓。然而,實際ADC操作也受到非理想效應的影響,所產生的誤差超出了轉換器分辨率和采樣速率所決定的誤差。與ADC相關的許多交流和直流性能規(guī)格中都會體現(xiàn)這些誤差。

圖5.理想ADC的轉換函數

在此范圍內,任何模擬輸入會產生同樣的數字輸出碼。

材料

ADALM2000 主動學習模塊

無焊試驗板和跳線套件

一個OP482 運算放大器

兩個AD654 電壓頻率轉換器

三個1 kΩ電阻

五個10 kΩ電阻

一個1 nF電容

一個SN74HC08與門

一個SN74HC32或門

一個SN74HC04逆變器

一個1 μF電容

一個AD7920 12位ADC

閃存ADC

背景信息

Flash ADC,也稱為并行ADC,是將模擬信號轉換為數字信號的最快方法之一。Flash ADC非常適合需要極寬帶寬的應用,但其功耗比其他ADC架構高且通常限制為8位分辨率。典型示例包括數據采集、衛(wèi)星通信、雷達處理、采樣示波器和高密度硬盤驅動器。

Flash ADC由高速比較器級聯(lián)而成。對于一個N位轉換器,電路采用2N -1個比較器,同時有2N個電阻提供基準電壓。當比較器的模擬輸入電壓高于所施加的基準電壓時,其輸出1。否則,比較器輸出0。代碼從1變?yōu)?的點就是輸入信號小于相應比較器基準電壓電平的點。

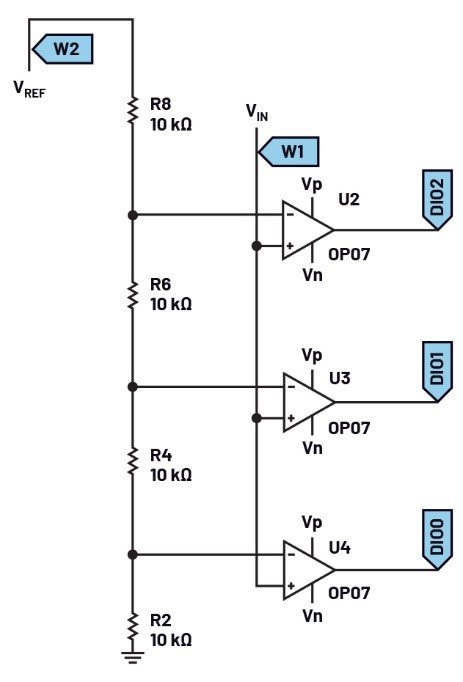

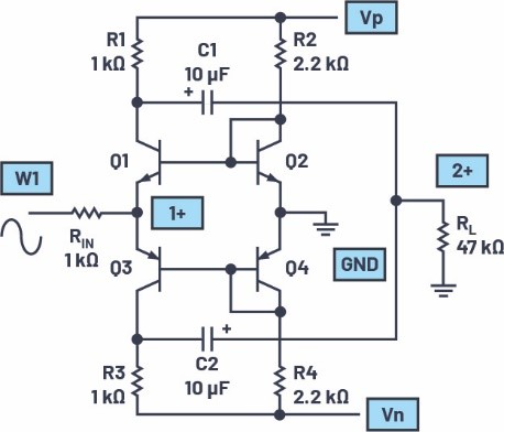

請看圖6所示的電路。

圖6.Flash ADC—模擬側電路

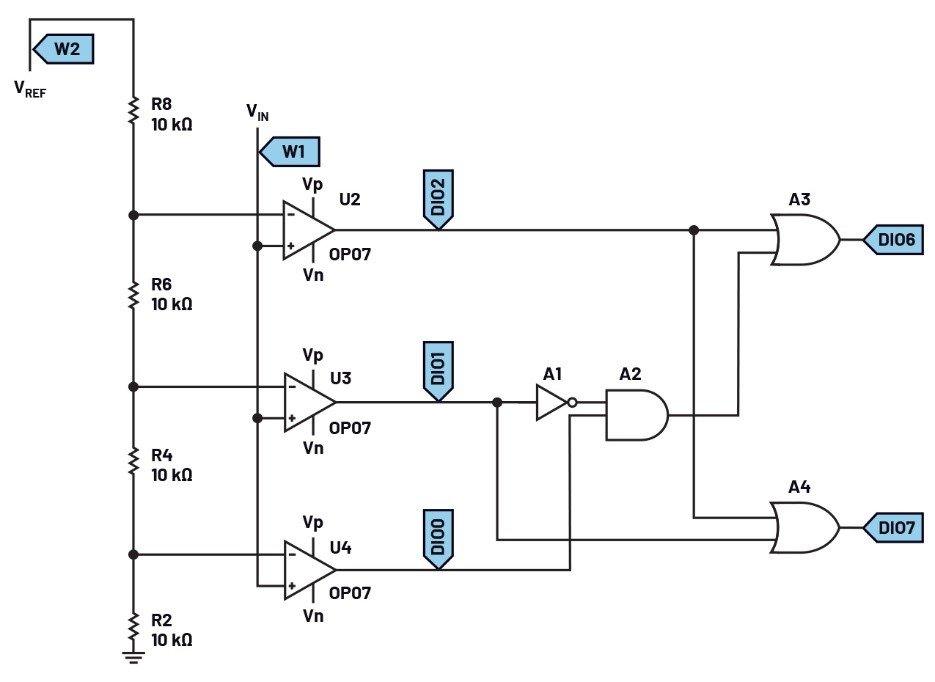

此電路表示2位Flash ADC的模擬側,其架構稱為溫度計代碼(一元碼)編碼。對于此類電路,需要使用額外的邏輯電路將一元碼解碼成適當的數字輸出碼。通過使用邏輯與門、或門和非門,我們可以構建專有編碼器。其輸出為原始數值的二進制表示,最高有效輸入位從0開始。

圖7.Flash ADC—編碼輸出

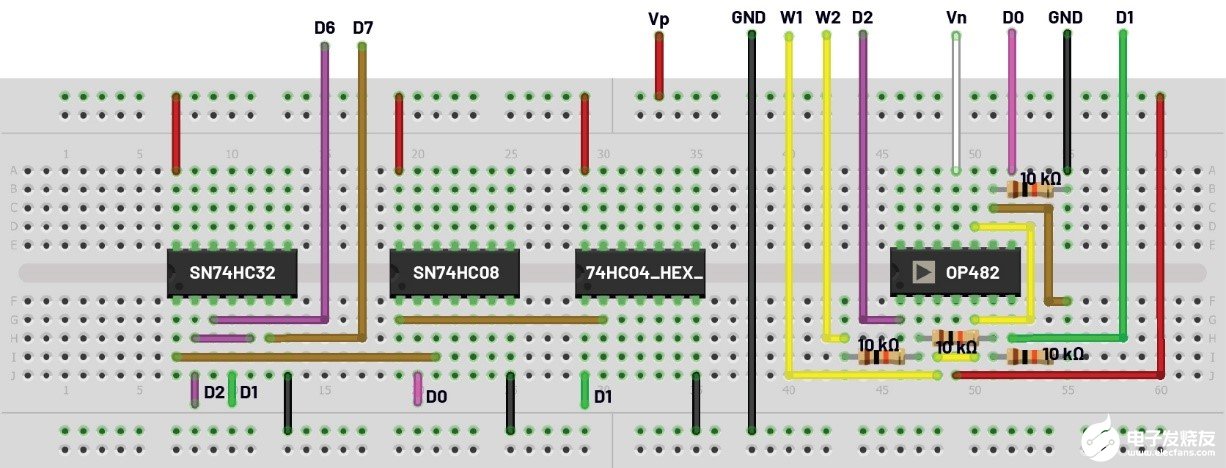

圖8.Flash ADC試驗板連接

如前所述,F(xiàn)lash ADC使用高速比較器構建而成,但為了方便起見,我們將使用OP482四通道運算放大器來介紹工作原理。或者,可以使用四個AD8561比較器來構建此電路。

硬件設置

在無焊試驗板上構建圖7所示的電路。這是一個用于具有編碼輸出的2位Flash ADC的電路。

程序步驟

向電路提供±5 V電源電壓。在Scopy中將信號發(fā)生器的AWG1配置為具有5 V峰峰值幅度、2.5 V偏移和100 Hz頻率的上升斜坡鋸齒波。將AWG2用于為ADC提供5 V恒定基準電壓。

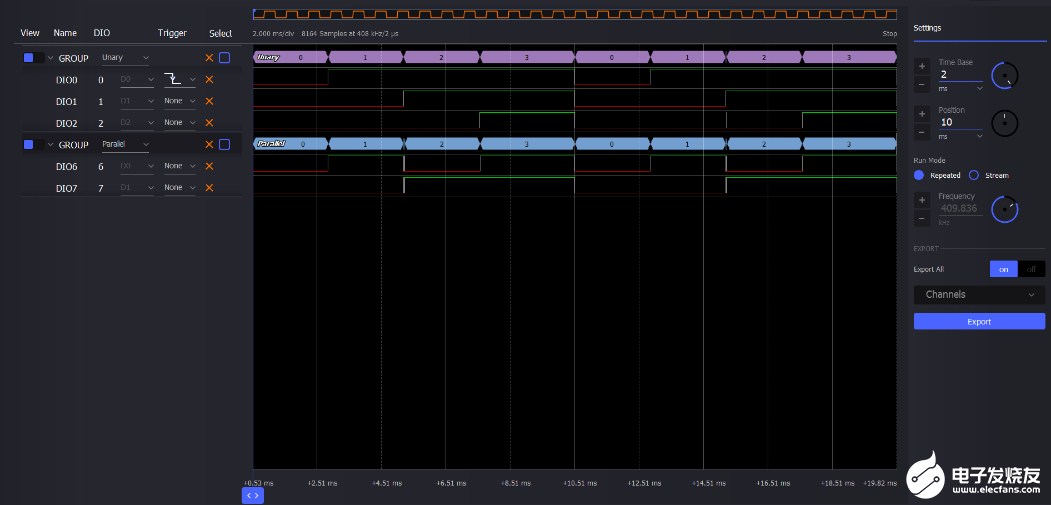

配置邏輯分析儀,使得數字通道DIO0、DIO1和DIO2形成一個針對一元碼解碼的通道組,通道DIO6和DIO7形成一個針對并行輸出解碼的通道組。

輸出信號波形如圖9所示。

圖9.Flash ADC—輸出碼

一元組通道表示2位Flash ADC的輸出溫度計代碼,通過在整個可用范圍(0 V至5 V)內改變輸入模擬電壓來提供所有可能的輸出值。并行通道表示相當于ADC輸出狀態(tài)的二進制值。

電壓頻率轉換器用作ADC

背景信息

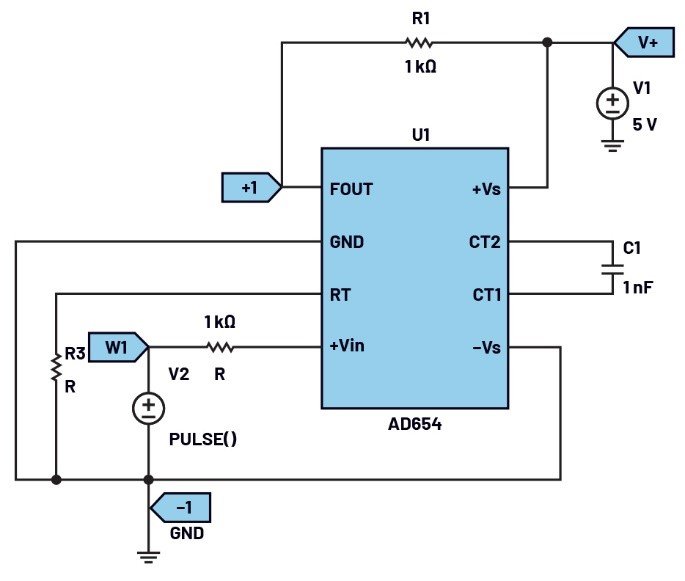

在這個特殊應用中,AD654電壓頻率轉換器用作ADC。

圖10.電壓頻率轉換器用作ADC

為了實現(xiàn)轉換,應將轉換器的輸出端連接到集成間隔定時器/事件計數器的微型計算機。

計數期間的信號邊沿(上升或下降)總計數與輸入電壓成正比。在此特定設置下,1 V滿量程輸入電壓會產生100 kHz信號。如果計數周期為100 ms,則總計數將為10,000。然后依據與該最大值的比例便可確定輸入電壓。因此,計數為5000時,相應的輸入電壓為0.5 V。

硬件設置

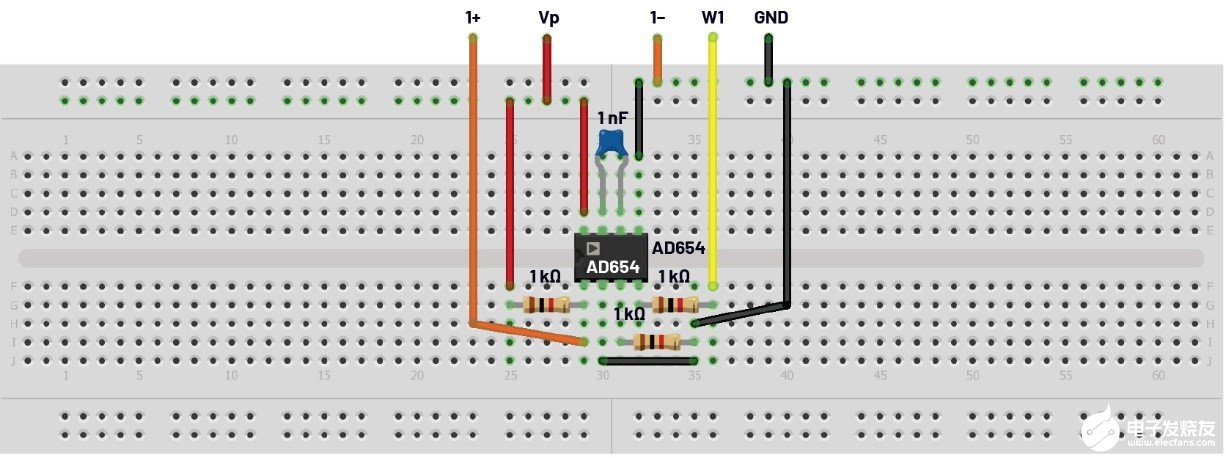

構建試驗板電路以將電壓頻率轉換器用作ADC,如圖11所示。

程序步驟

向電路提供5 V電源電壓。將信號發(fā)生器的AWG1配置為1 V恒定電壓。

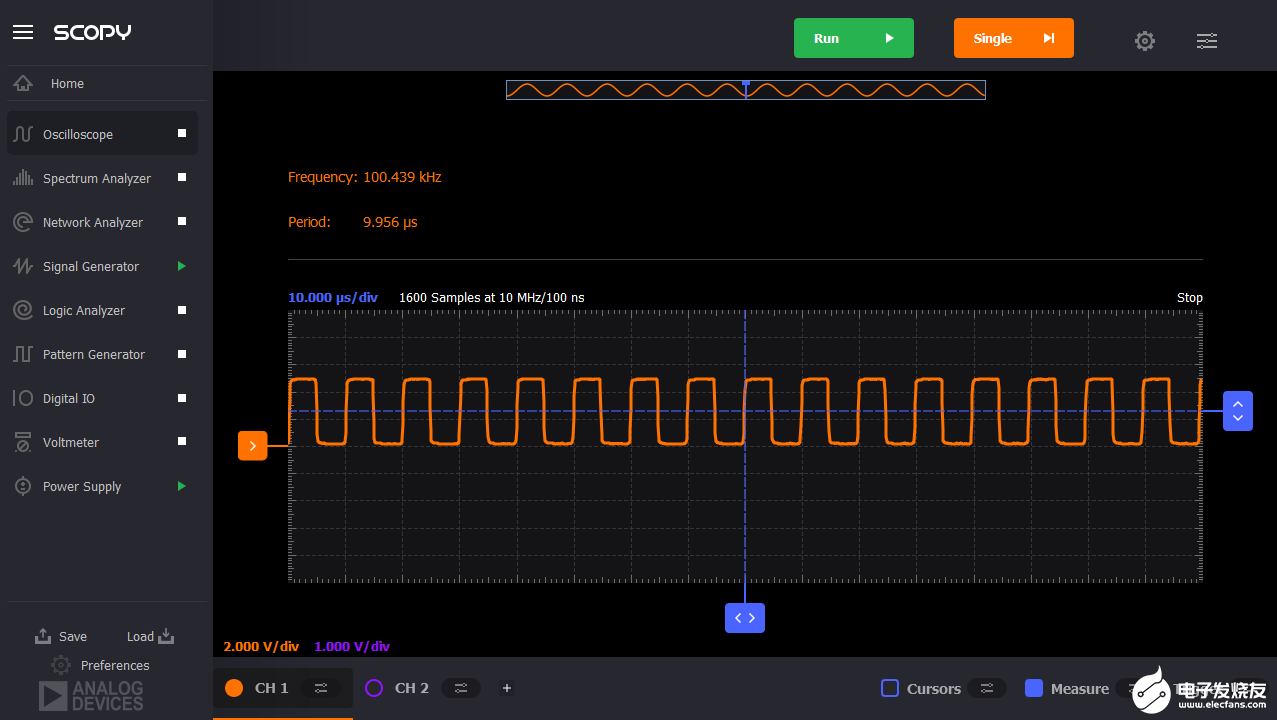

配置示波器,使通道1上顯示輸出信號,并從通道1“測量”選項卡中啟用頻率測量。輸出信號波形如圖12所示。

圖11.電壓頻率轉換器用作ADC—試驗板連接

圖12.滿量程輸入電壓下電壓頻率轉換器用作ADC

圖12中的曲線顯示了電壓頻率轉換器采用1 V滿量程輸入電壓時的輸出信號波形。請注意,相應輸出頻率為100 kHz。

現(xiàn)在將輸入電壓設置為0.5 V。輸出信號波形如圖13所示。

圖13.半量程輸入電壓下電壓頻率轉換器用作ADC

圖中顯示了電壓頻率轉換器采用0.5 V半量程輸入電壓時的輸出信號波形。請注意,輸出頻率現(xiàn)在為50 kHz。

逐次逼近寄存器(SAR) ADC

背景信息

逐次逼近寄存器(SAR) ADC在每次轉換時,針對所有可能的量化電平,通過二進制搜索將連續(xù)模擬波形轉換為離散數字表示,最后匯聚為數字輸出。

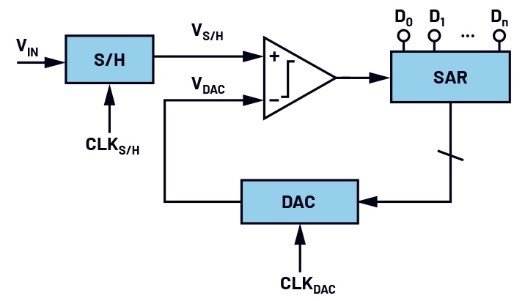

通常,SAR ADC電路由四個子電路組成:

用于采集輸入電壓(VIN)的采樣保持電路(S/H)。

模擬電壓比較器,它將VIN與內部DAC的輸出進行比較并將比較結果輸出至SAR。

SAR子電路,用于向內部DAC提供VIN的近似數字碼。

內部基準DAC,向比較器提供相當于SAR數字碼輸出的模擬電壓。

圖14.SAR ADC的典型架構

對SAR進行初始化,使最高有效位(MSB)等于數字1。將此代碼輸入DAC,然后DAC將此數字碼的模擬等效信號(VREF/2)提供給比較器電路,以便與采樣輸入電壓進行比較。如果此模擬電壓超過VIN,則比較器使SAR重置此位;否則,此位將保留為1。然后將下一位設置為1并進行相同的測試,持續(xù)執(zhí)行此二進制搜索直到SAR中的每個位都已經過測試。所得到的代碼是采樣輸入電壓的數字近似值,并最終由SAR在轉換結束(EOC)時輸出。

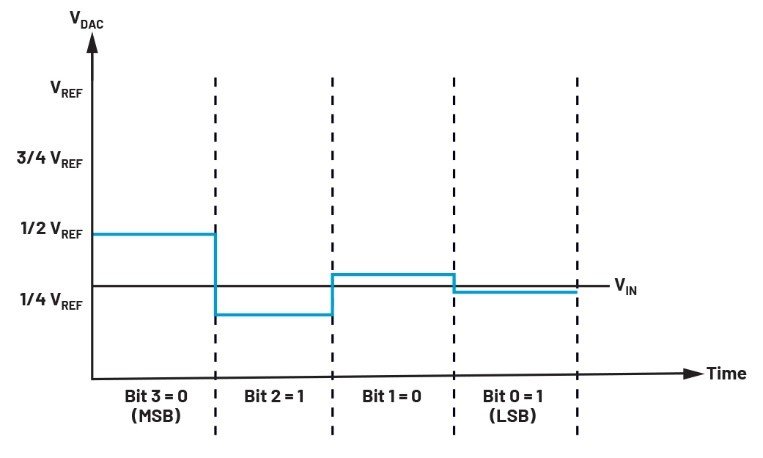

圖15.4位SAR ADC示例

圖15顯示了4位轉換的一個示例。y軸表示DAC輸出電壓。在此示例中,第一次比較顯示VIN < VDAC。因此,位3設置為0。然后將DAC設置為0100并進行第二次比較。由于VIN > VDAC,位2保持為1。然后將DAC設置為0110并進行第三次比較。將位1設置為0,然后將DAC設置為0101進行最終比較。最后,由于VIN > VDAC,位0保持為1。

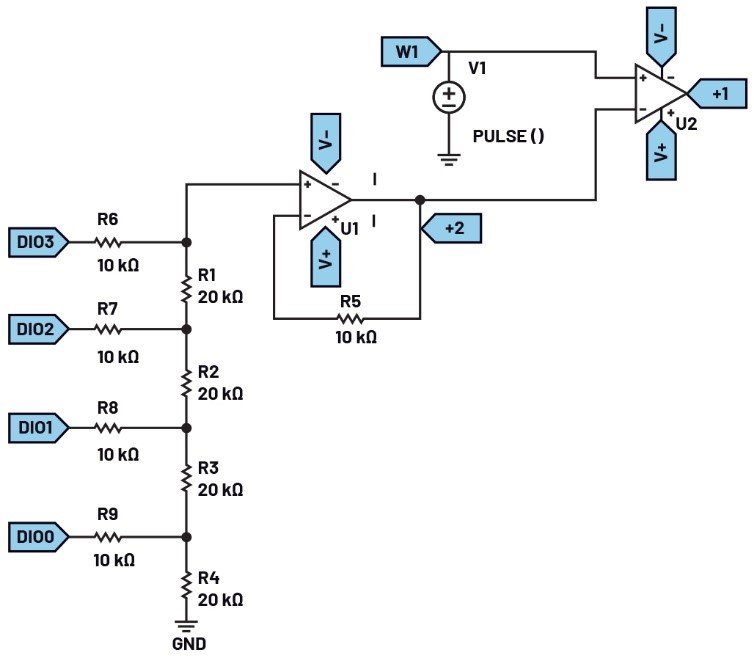

硬件設置

為了利用ADALM2000重點說明SAR ADC的工作原理,對于DAC器件將使用在下次實驗中探討的電路,但此設置中將使用4位DAC(而不是8位)。DAC的輸出端將連接到比較器,同時通過腳本對SAR進行仿真,該腳本基于比較器的輸出執(zhí)行二進制搜索并生成正確的二進制值。

圖16.SAR ADC原理圖

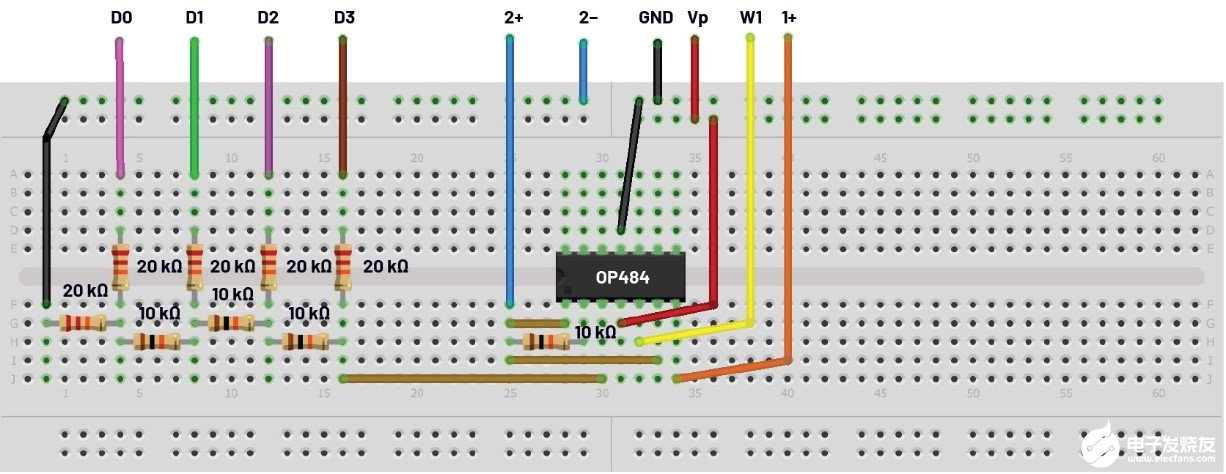

構建SAR ADC的試驗板電路,如圖17所示。

圖17.SAR ADC試驗板連接

將OP484集成電路中的兩個精密軌到軌運算放大器用于該SAR ADC,一個用于R-2R梯形DAC,另一個作為DAC輸出和輸入電壓之間的比較器。

程序步驟

向電路提供±5 V電源電壓。配置示波器,使通道1上顯示比較器輸出信號,通道2上顯示DAC輸出信號。

將邏輯分析儀中的前4個數字通道分組,并將解碼器設置為并行。

下載SAR ADC腳本,并使用Scopy界面運行腳本。

使用逐次逼近法,根據從比較器輸出端收到的反饋更新數字碼。

利用示波器在時域內實現(xiàn)DAC輸出的逼近行為可視化。產生的波形如圖18所示。

圖18.SAR ADC逐次逼近波形

經過幾個逼近步驟后,輸出值接近輸入值(設置為2 V)。

AD7920 12位ADC

背景信息

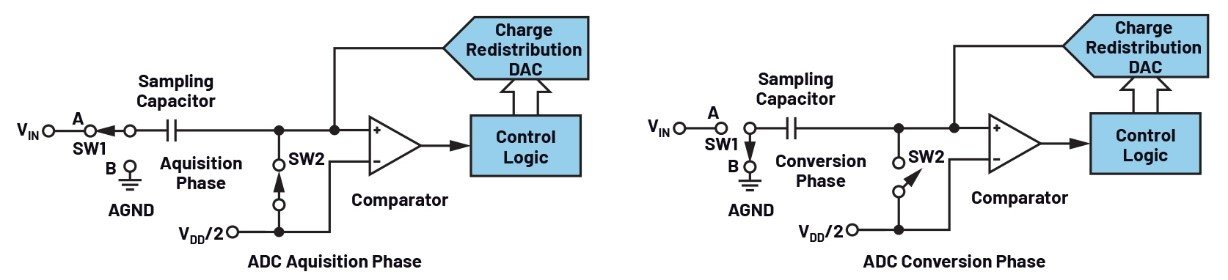

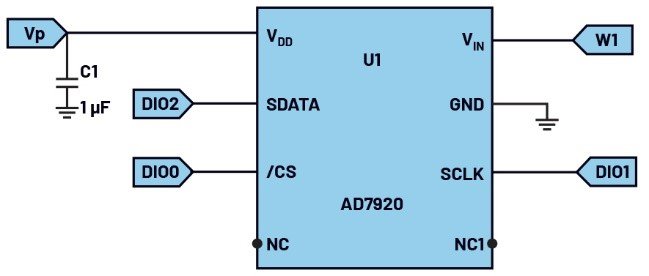

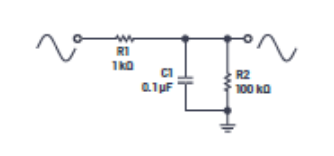

AD7920是一款12位高速、低功耗SAR ADC。它可以采用單電源供電,電源電壓范圍為2.35 V至5.25 V。此ADC支持串行接口。串行時鐘提供轉換時鐘,并在轉換期間控制來自AD7920的信息傳輸。轉換過程和數據采集過程通過/CS和串行時鐘進行控制,從而為器件與微處理器或DSP接口創(chuàng)造了條件。輸入信號在/CS的下降沿進行采樣,而轉換同時在此處啟動。圖19顯示了ADC采樣階段和轉換階段的簡化原理示意圖。

在采樣階段,SW2閉合且SW1置于A。在此設置下,比較器保持在平衡狀態(tài),采樣電容采集VIN的信號。為使ADC啟動轉換,SW2斷開,而SW1移至位置B,使比較器變得不平衡。控制邏輯和電荷再分配DAC可以加上和減去采樣電容中的固定電荷數量,使得比較器恢復到平衡狀態(tài),進而轉換完成。

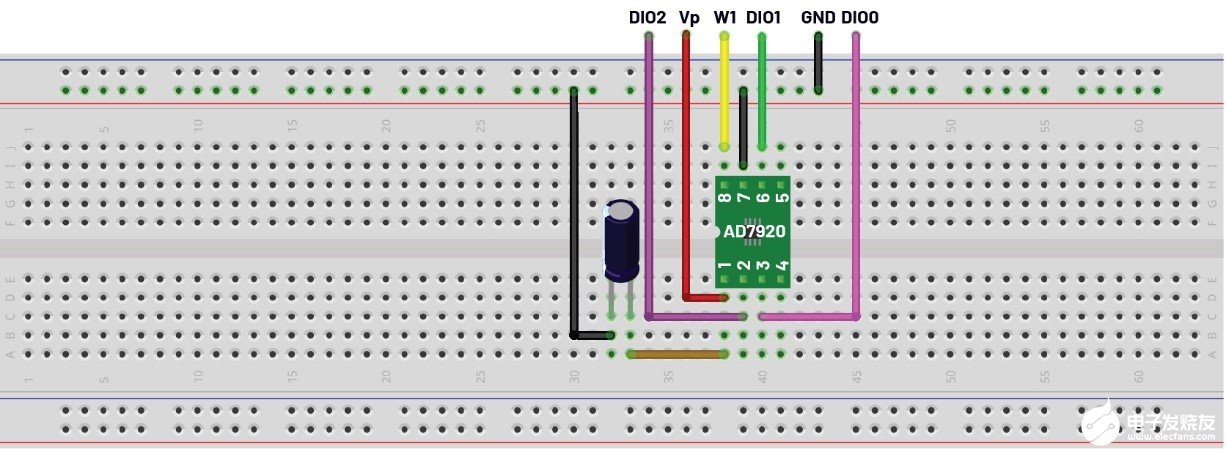

硬件設置

圖21給出了AD7920的典型連接設置。VREF取自內部VDD,因此其應充分解耦。這將提供0 V到VDD的模擬輸入范圍。轉換結果以16位字輸出,前4位為0,后12位或10位MSB為結果。

圖19.AD7920采樣和轉換階段

圖20.AD7920試驗板連接

圖21.AD7920典型連接

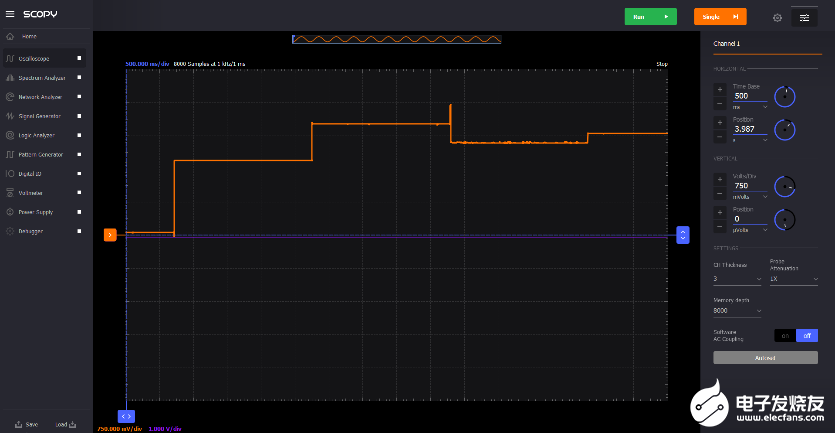

程序步驟

打開Scopy,使能正電源為3 V。配置信號發(fā)生器的通道1為0 V到3 V之間的某一恒定值,例如該域的中間值1.5 V。可以在示波器上監(jiān)視這些電壓的實際值。

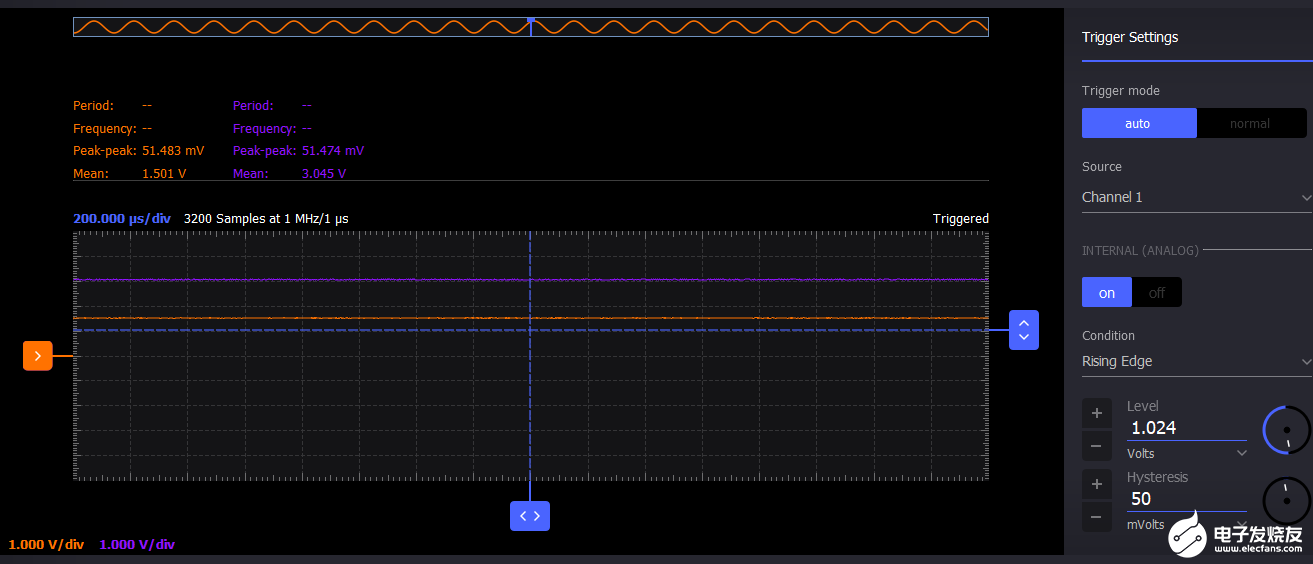

圖22.VIN(通道1)和VREF(通道2)電壓

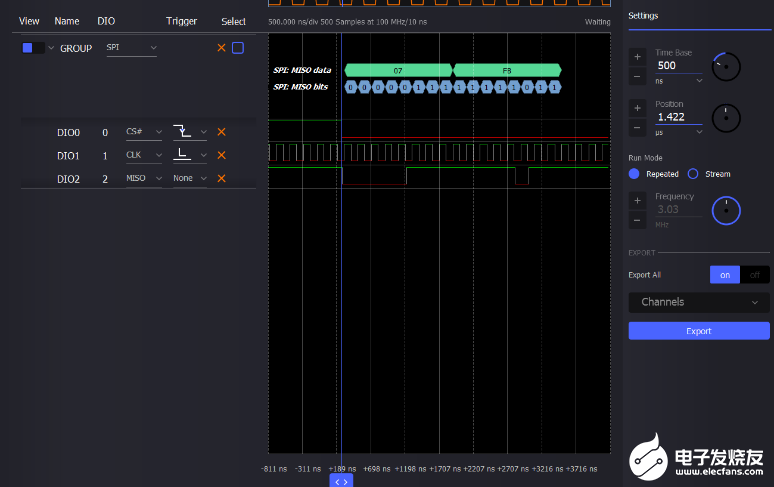

在邏輯分析儀中,將DIO0、DIO1和DIO2配置為一個組通道。將該組通道設置為SPI,各通道設置為對應的SPI信號——DIO0為CS#,DIO1為CLK,DIO2為MISO。當CS#下降沿啟動數據傳輸時,應將DIO0觸發(fā)器設置為下降沿。將DIO1觸發(fā)器設置為低電平,并從觸發(fā)器設置中將“觸發(fā)器邏輯”設置為AND。DIO2是ADC的輸出信號,不需要觸發(fā)器設置。使能邏輯分析儀,它應在等待觸發(fā)信號。

在模式發(fā)生器中配置時鐘信號。使能DIO1通道,將其“模式”設置為5 MHz頻率的時鐘,然后單擊Run(運行)。可以從數字IO工具控制CS#。當切換配置為輸出引腳的DIO0引腳時,轉換機會開始。如果CS#的下降沿和CLK的低電平狀態(tài)同時發(fā)生,轉換將啟動,應能在邏輯分析儀中看到輸出信號和MISO十六進制數據,如圖23所示。

圖23.AD7920的SPI接口

可以使用ADC轉換函數的公式檢查結果,其中MISO數據為數字輸出碼,示波器通道1上讀取的電壓為模擬輸入,示波器通道2上讀取的電壓為基準輸入,N為AD7920的位數。

以上計算得出的結果是ADC輸入電壓為1.5 V,在示波器通道1上讀出的也是該值。

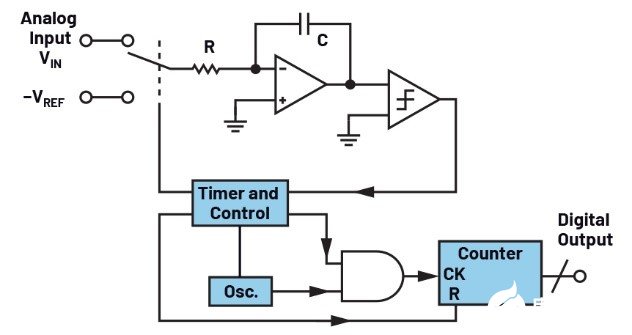

額外活動:雙斜率ADC

雙斜率ADC(或變體)是許多高精度數字電壓表的核心器件。此架構具有幾個有用的特性:由于大多數誤差源都會抵消,因此只需要幾個精密元件,還可以通過配置來抑制特定噪聲頻率,如50 Hz或60 Hz線路噪聲,并且對高頻噪聲不敏感。

圖24.雙斜率ADC結構

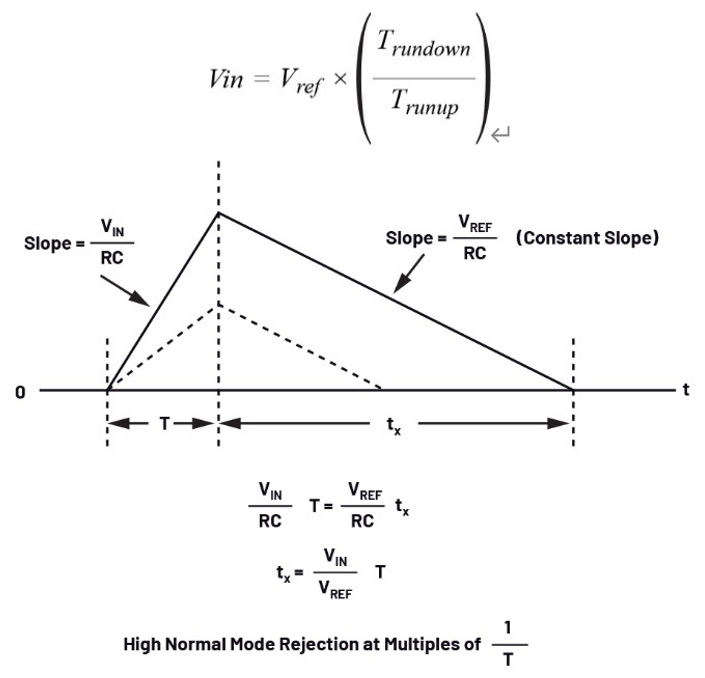

轉換器的工作原理如下:在固定時間內對積分器施加未知輸入電壓(稱為上坡(runup)),然后對積分器施加與輸入極性相反的已知基準電壓(稱為下坡(rundown))。因此,輸入電壓可以根據基準電壓和下坡-上坡時間比計算得到:

圖25.雙斜率ADC積分器輸出波形

可以看出,雙斜率轉換器的精度不受大多數元件容差的影響:

積分器的電阻和電容容差會影響輸出斜率,但同時也會影響上坡和下坡。

用于設置上坡時間和測量下坡時間的時基誤差對兩個時間的影響是相同的。

基準電壓必須準確,因為它會直接影響測量結果。另一個誤差源是積分器電容中的電介質吸收,因此聚丙烯或聚苯乙烯是理想選擇,而鋁電解不太合適。

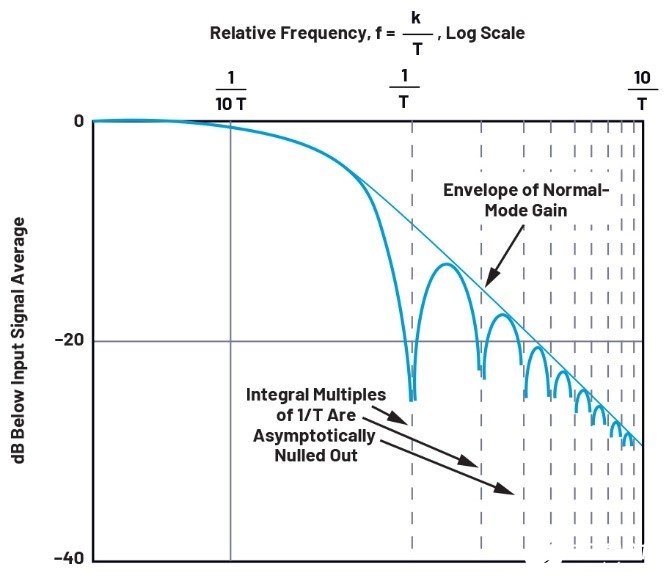

圖26.雙斜率ADC積分器輸出波形

圖26所示為雙斜率ADC的頻率響應。在固定時間間隔(上坡)內對輸入采樣,上坡開始時電壓對結果的影響與上坡結束時電壓對結果的影響一樣。有時也將此稱為箱式平均值,它能夠抑制在1/T、2/T、3/T等頻率下發(fā)生的干擾(噪聲)。200 ms積分時間對應于10個周期的50 Hz噪聲和12個周期的60 Hz噪聲;由于它能夠抑制線路噪聲,因此通常將其作為上坡時間。

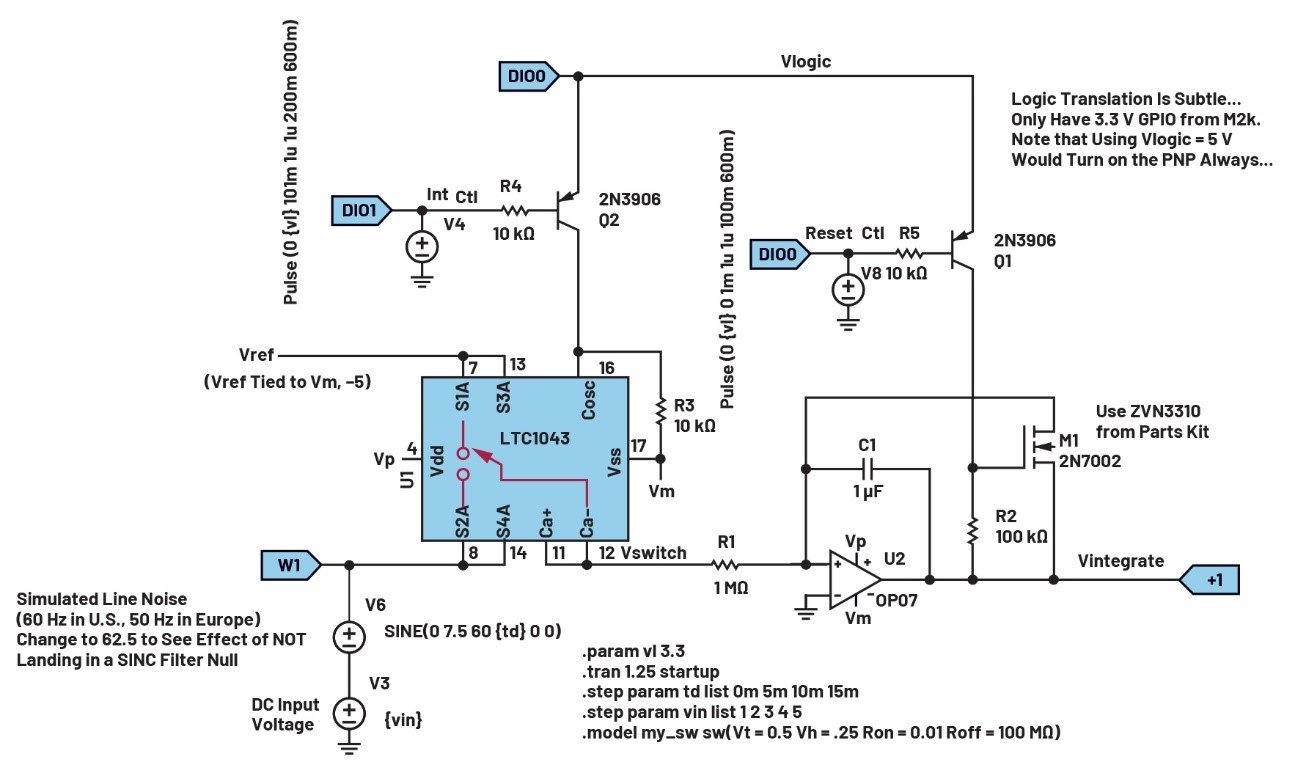

仿真

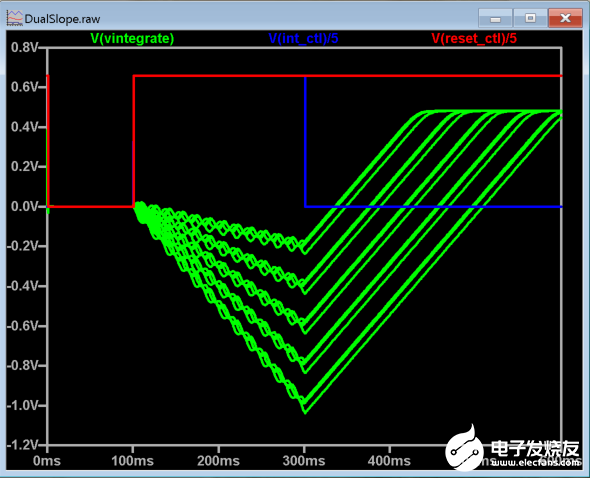

打開這里提供的LTspice?文件DualSlope.asc。

圖27.雙斜率ADC積分器原理圖

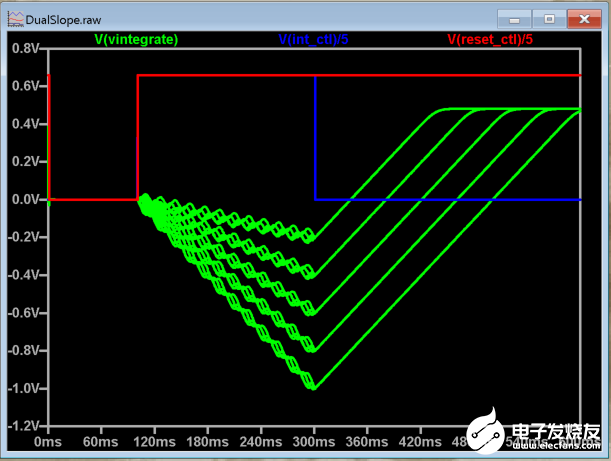

運行仿真,探測Vintegrate節(jié)點。

圖28.雙斜率ADC積分器仿真1

該仿真將60 Hz線路噪聲添加到直流輸入電壓中。通過.step指令運行幾種情況——1 V、2 V、3 V、4 V 5 V輸入電壓以及60 Hz線路噪聲的幾個不同相位。由于200 ms上坡時間是60 Hz線路周期的整數,所以噪聲在頻率響應中為零,并且無論相位如何,下坡時間都不受影響。將頻率更改為62.5 Hz,使其處于頻率響應的峰值。

圖29.雙斜率ADC積分器仿真2

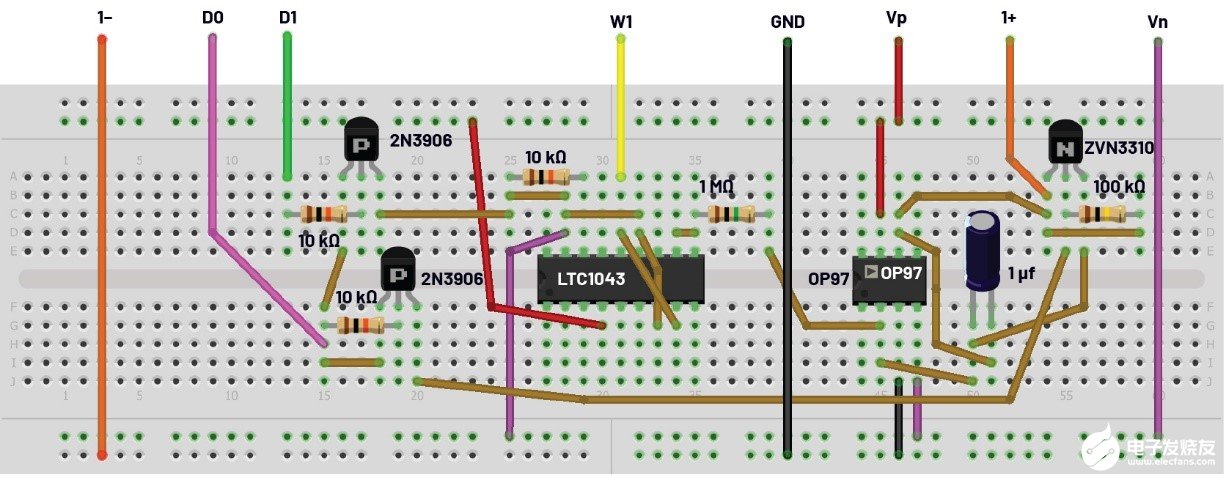

硬件設置

為雙斜率ADC構建試驗板電路,如圖30所示,并按照圖示對M2K進行連接。

圖30.雙斜率ADC積分器試驗板電路

程序步驟

打開Scopy。內核Scopy初始化文件Dual_slope_scopy_setup.ini以幫助設置。

電源:使能跟蹤,設置為±5 V。

數字IO:DIO2設置為OUT,設置為1。

模式發(fā)生器:組DIO0、DIO1,模式:導入(加載文件dual_slope_pattern.csv)。頻率設置為5 Hz。

信號發(fā)生器:通道1初始設置為恒定2.5 V。

示波器:200 ms時基,通道1設置為400 mV/刻度。下降沿觸發(fā)器,200 mV(將在積分器重置間隔開始時觸發(fā)M2K)。

圖31.雙斜率ADC積分器波形

當基準電壓源連接到-5 V電源并將輸入電壓設置為2.5 V時,請注意下坡為2格(400 ms),而上坡為1格(200 ms)。因此:

VIN = 5 V × (200 ms / 400 ms) = 2.5 V

通過改變輸入電壓,可以看到上坡時間發(fā)生變化。波形如圖32所示。

圖32.不同輸入電壓的雙斜率ADC積分器波形

實際實現(xiàn)雙斜率轉換器時,將使用一個微控制器來控制積分器并設置上坡/測量下坡時間。大多數微控制器都提供計數器外設,因而很容易實現(xiàn)。

-

adi

+關注

關注

144文章

45796瀏覽量

245980 -

模數轉換

+關注

關注

1文章

210瀏覽量

36572

發(fā)布評論請先 登錄

相關推薦

學子專區(qū)—ADALM2000實驗:放大器輸出級

學子專區(qū)—ADALM2000實驗:BJT差分對

ADALM2000 schematic中輸入電路AD8066前面的并聯(lián)RC是干什么的呢?

Seeed ADALM2000-M2K 示波器

學子專區(qū)—ADALM2000實驗:MOS差分對

學子專區(qū)—ADALM2000實驗:跨阻放大器輸入級

如何使用Python和ADALM2000創(chuàng)建示波器

虛擬電子實驗室:如何使用Python編程語言和ADALM2000創(chuàng)建示波器

ADALM2000實驗:CMOS邏輯電路、D型鎖存器

【官網直購】ADALM2000 高級主動學習模塊ADI 官網現(xiàn)貨發(fā)售!

ADALM2000實驗:模數轉換

ADALM2000實驗:模數轉換

評論