保證覆蓋率的同時優化仿真回歸

隨著應用要求的激增和用戶需求的增加,硬件設計變得更加復雜。市場趨勢的快速變化,以及對電動汽車等技術的更多關注,決定了對高效電源管理和高性能處理的需求水漲船高。隨著 SoC 設計規模的擴大,復雜程度的增加,驗證吞吐量仍然是一個瓶頸,單純依靠增加 CPU 核數量和運行更多的并行測試治標不治本。上述因素的疊加讓驗證工程師面對復雜設計的壓力與日俱增。

驗證永遠不會完成;當你的時間用完時,它就結束了。目標是在你耗盡時間之前使驗證過程收斂。每個人都希望看到關鍵指標收斂到目標,并在嚴格的成本和時間限制下做到這一點。想象一下,坐在駕駛艙里,向黑匣子輸入信息,然后等待奇跡發生(按一個按鈕,你的工作就完成了)。當務之急是人工智能和機器學習(AI/ML)如何幫助我們更快地完成回歸,節省調試時間,實現驗證/覆蓋率目標,并管理資源和資金——換句話說,我們如何使用 AI/ML 來提高驗證的效率?

瑞薩公司也面臨著類似的挑戰。市場壓力和嚴格的投片時間表促使他們尋找一種技術/方法來優化仿真回歸,并在整個產品開發過程中加速設計驗證過程。他們希望減少風險,盡早發現盡可能多的錯誤,能夠快速調試,并滿足其終端用戶的要求。

瑞薩開始探索 Cadence Xcelium 機器學習應用。這個應用程序使用機器學習技術來優化仿真回歸,以產生一個更緊湊的壓縮回歸。然后這個優化的回歸被用來重現與原始回歸幾乎相同的覆蓋率,并通過運行現有隨機測試平臺可能出現的邊界場景,快速找到設計錯誤。

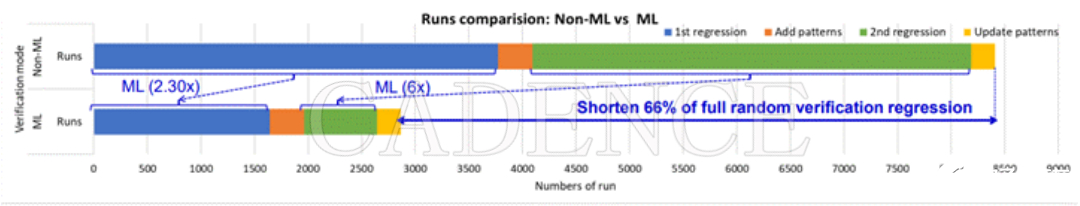

瑞薩的測試結果非常完美,整個隨機驗證回歸的時間縮短了 66%,大幅節省了資源,成本和時間。Xcelium ML App 幫助瑞薩在保證 100%覆蓋率的同時將壓縮效率提高 2.2 倍。此外,將 ML 回歸用于首次設計迭代時,瑞薩再次實現了 100%覆蓋率下,將時間縮短 3.6 倍。

基于 ML 的測試回歸次數僅為 1168,相當于 3774 次原始回歸的 1/3。實現目標所需時間縮短了 30%,滿足了嚴格的上市需求。

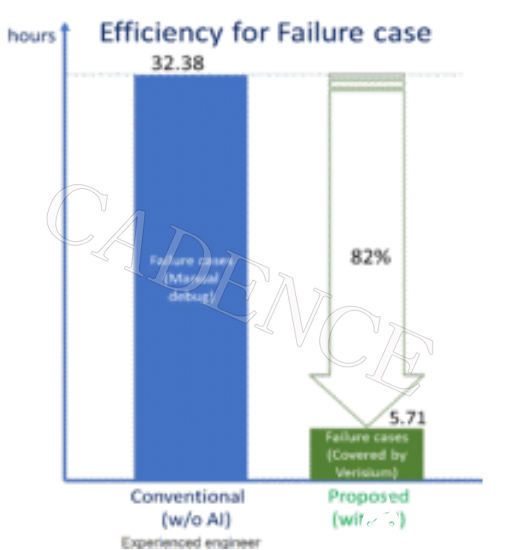

除了利用 Xcelium ML App 節省資源和時間,加速實現設計收斂,瑞薩也評估了由 3款 Verisium App 組成,基于 AI 的 Cadence Verisium 平臺,將驗證生產力提高了 6 倍,共節省 27 個工時。

瑞薩評估的 App 如下:

Verisium AutoTriage,一款基于 ML 的自動化測試失敗分類程序,可以將相同錯誤導致的測試失敗自動分組。失敗分組耗時降低了 70%,整體效率提升了 3.3 倍。

Verisium SemanticDiff 幫助瑞薩快速識別失敗原因,比傳統 diff 工具更加高效。SemanticDiff 專注于設計環境,可以提供更相關的差異分析。此外,逐條檢查 diff 指令的歷史文件是很繁瑣的,SemanticDiff app 可以大幅縮短糾錯時間,顯著提升效率。

Verisium WaveMiner 可以高效識別差異點,用戶可以在 PASS 和 FAIL 中將差異點可視化,便捷地比較 PASS 和 FAIL 的波型及源代碼。瑞薩的糾錯時間得以縮短 89%-97%,帶來 9 倍的效率提升。

Cadence 的 Verisium 平臺和 Xcelium ML 應用一起提供了一套利用 AI/ML 的應用,以優化驗證工作負載,提高覆蓋率,并加速復雜 SoC 上設計錯誤的根源分析。瑞薩公司利用人工智能平臺,將其驗證生產率提高了 10 倍。

-

Cadence

+關注

關注

64文章

915瀏覽量

141866 -

瑞薩

+關注

關注

35文章

22292瀏覽量

86069

發布評論請先 登錄

相關推薦

新一代AI/ML加速器新型內存解決方案——HBM2E內存接口

富士通AI平臺“Fujitsu Kozuchi”加速AI與ML解決方案交付

海量干貨分享!XDF(賽靈思開發者大會)北京站各分論壇演講資料公布

如何加速電信領域AI開發?

X-CUBE-AI和NanoEdge AI Studio在ML和AI開發環境中的區別是什么?

新思科技發布業界首款全棧式AI驅動型EDA解決方案Synopsys.ai

基于軟件的Vitis AI 2.0加速解決方案

AI驅動芯片驗證:VSO.ai在手,覆蓋率收斂更快、更好、更高效

下周五|AI驅動芯片驗證:VSO.ai在手,覆蓋率收斂更快、更好、更高效

本周五|AI驅動芯片驗證:VSO.ai在手,覆蓋率收斂更快、更好、更高效

深入探討工業AI/ML技術的發展趨勢及相關解決方案

Supermicro推新AI存儲方案,助力AI和ML應用加速

是德科技推出AI數據中心測試平臺旨在加速AI/ML網絡驗證和優化的創新

AI/ML 解決方案加速驗證曲線收斂

AI/ML 解決方案加速驗證曲線收斂

評論