隨著量子計算的出現,對外圍容錯邏輯控制電路的需求達到了新的高度。在傳統計算中,信息的單位是“1”或“0”。在量子計算機中,信息單位是一個量子比特,可以描繪為“0”、“1”或兩個值的疊加(稱為“疊加態”)。

由于其高性能和低功耗,傳統計算機中的控制電路都基于 CMOS(半導體)。傳統計算機的“1”和“0”可以使用在室溫下運行的 CMOS 芯片進行操控、存儲和輕松讀取。如今,大多數量子計算機都在低溫下運行,以確保量子比特盡可能長時間地保持一致(處于疊加態)。在量子計算機中,一致的時間通常非常短(納秒到毫秒),因此需要更多能夠執行高速、容錯操控的控制電路。如果傳統的CMOS控制電路可以在低溫下運行,則可以滿足這一要求。

A.K. Jonscher 曾在《Proceedings of the IEEE》期刊上發表過題為“低溫下的半導體”的文章,其中首次嘗試描述低溫下的半導體材料[1]。他的兩個基本結論是:1) 由于“在這樣的極端溫度下進行大規模實驗沒有切實的技術理由”,半導體器件在當時沒有重要的低溫應用;2) “半導體材料在低溫下的特性與我們熟悉的較高溫度下特性有顯著不同,因此可以合理地預期,通過在這個方向上持續進行研究和開發,將會出現更多的器件應用”。幾年后,IBM 開始對低溫下的半導體器件操控產生興趣[2-3]并得出結論:MOSFET半導體器件在低溫下表現出更高的性能。低溫操控雖有優勢,但按比例縮小冷卻裝置仍然是使用基于半導體的控制電路的障礙。

進入量子力學。1959 年,Richard Feynman 向科學界提出挑戰,要求在信息處理系統的設計中使用量子力學。他設想了涉及量子化能級和/或量子化“自旋”(量子粒子的角動量)相互作用的新信息系統和功能。這在1980 年代得到實現,當時證明了基于能量的量子力學方程可以代表通用的圖靈(計算)機[4]。1994年的研究表明,(“在多項式時間內”)量子計算機可以比傳統計算機更快地分解整數[5]。這一發現激發了人們對構建量子計算系統的持續興趣,直到今天在眾多商業、研究和學術組織中還持續存在。

即使人們對構建量子計算機有濃厚的興趣,但事實是,這種計算機的成功運行目前仍然需要低溫環境,量子邏輯控制電路也需要在低溫下工作才能高效運轉。因此,我們看到人們對基于 CMOS 的電路的低溫性能重新產生了興趣。

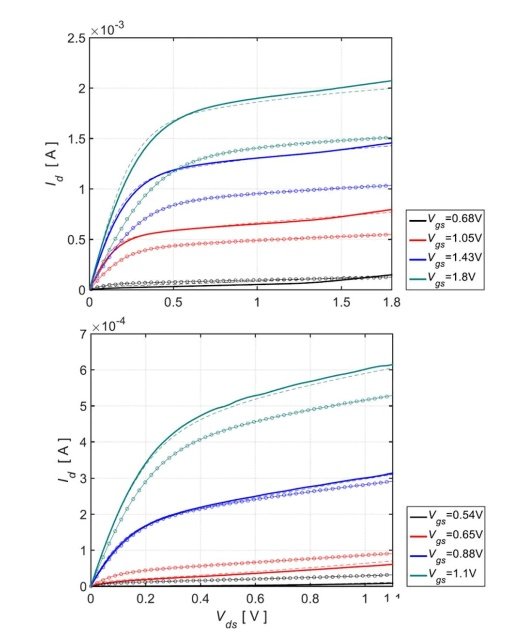

量子計算機不需要最先進的CMOS電路,但CMOS器件在低溫和室溫下的運行方式不同。最近研究人員分別在室溫和 4.2 開爾文溫度下,在 40nm 和 160nm 為主體的 CMOS 器件上測量了 CMOS 晶體管性能(以及相關的電流-電壓特性)(如圖1所示)。由于在這些溫度下硅中的遷移率提升,低溫下的驅動電流也將增加。不幸的是,基底凍結等其他因素會限制在這些低溫下驅動電流的增加。

圖1: 在 160nm(上)和 40nm(下)CMOS 中制造的 nMOS 晶體管測量電流-電壓特性。點狀曲線顯示室溫操控,實線顯示液氦操控,短劃虛線顯示擬合實驗數據的 Spice 兼容模型[6]

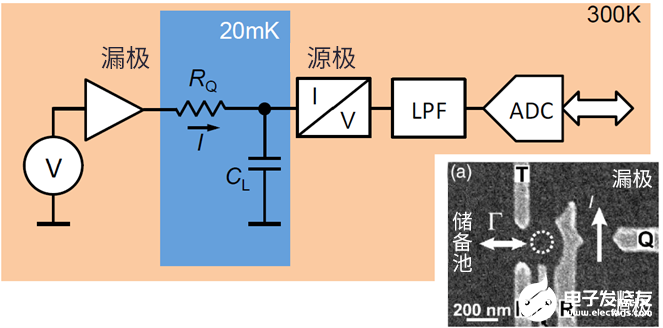

量子計算機的控制電路目前在室溫下運行。如前所述,由于在較高溫度下讀取量子比特的“狀態”很敏感,這可能成為一個問題。在與量子計算機一樣的低溫冷凍柜中,在低溫或接近低溫的情況下運行 CMOS 電路,可以部分緩解這一挑戰。這種集成可以減少延遲并提高整體系統的可擴展性。盡管存在一些二階問題,但低溫下的CMOS晶體管可以執行與量子計算機一起工作所需的各種功能。這些功能包括以 I/V 轉換器、低通濾波器以及模擬信號/數字信號間的相互轉換等的執的能力(如圖2所示)。

圖2: 以虛線圓圈為中心的硅自旋量子比特、控制和讀出信號(M、P、R、T 和 Q),以及量子點接觸和配套電路的簡化示意圖。電壓源極在室溫下作為數模轉換器[6]

為了實現容錯量子計算機系統的預期性能,需要可以在極低溫下運行的新一代深亞微米 CMOS 電路[6]。通過將這一想法推演為其合乎邏輯的結果,最終得到一個量子集成電路 (QIC),其中量子比特陣列與讀取量子比特狀態所需的 CMOS 電子器件集成在同一芯片上。這種集成顯然是實現可擴展、可靠性和高性能兼備的量子計算的最終目標。

在未來的應用中,與量子比特之間的光通信可能也是必要的。在這種情況下,集成 CMOS電路還需要包括微米和納米光學結構,例如光導和干涉儀。這些類型的光學功能已在室溫CMOS器件上成功實現,在未來的量子計算應用中可能也需要在低溫下實現同等級別的光通信功能。

責任編輯:彭菁

-

CMOS

+關注

關注

58文章

5689瀏覽量

235170 -

驅動電流

+關注

關注

0文章

81瀏覽量

16041 -

量子計算機

+關注

關注

4文章

528瀏覽量

25373

發布評論請先 登錄

相關推薦

量子計算機和CMOS半導體的發展回顧與未來預測

量子計算機和CMOS半導體的發展回顧與未來預測

評論