今天我們要介紹的時(shí)序分析概念是 Critical Path 。全稱是關(guān)鍵路徑。剛接觸后端的同學(xué)可能經(jīng)常會(huì)聽到這個(gè)概念,什么是Critical Path? 一般是指我們?cè)O(shè)計(jì)中時(shí)序最關(guān)鍵的路徑,通常也就是timing最差或者最難修的路徑。

實(shí)際工作中,leader或者同事也經(jīng)常問你Critical Path在哪里。 這時(shí),我們要學(xué)會(huì)從時(shí)序報(bào)告中去找到timing最差的path并去分析它。

那如何分析呢?下面提供幾點(diǎn)建議

首先,我們可以看下這條path的走向是否合理,也叫作detour,通俗的解釋就是有沒有繞遠(yuǎn)路。

Innovus可以采用Global timing debug工具顯示path path的路徑

report_timing -machine_readable > critcal_path.mtarpt

ICC更加簡(jiǎn)單,可以直接在“ Import Path Pins ”里面黏貼timing path report顯示

其次,我們可以看下設(shè)計(jì)的clock tree做得平不平。 通常來說,我們還是希望clock tree能盡可能做平一點(diǎn),這樣timing更容易meet。簡(jiǎn)單一點(diǎn)的方法,我們能直接從時(shí)序報(bào)告中得到clock tree的skew,就是自己算下launch clock path和capture clock path的delay差值(下圖箭頭差值),如果差值過大,那就要重點(diǎn)看一下clock tree的質(zhì)量了。

最后,我們也可以分析下具體data path上,有沒有一些bad buffering, 過大的 load或者transition,甚至一些距離比較長(zhǎng)的net都可以研究下。

-

時(shí)序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22551 -

時(shí)序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5270

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

時(shí)序分析基本概念介紹<Operating Condition>

時(shí)序分析基本概念介紹&lt;Latency&gt;

時(shí)序分析Slew/Transition基本概念介紹

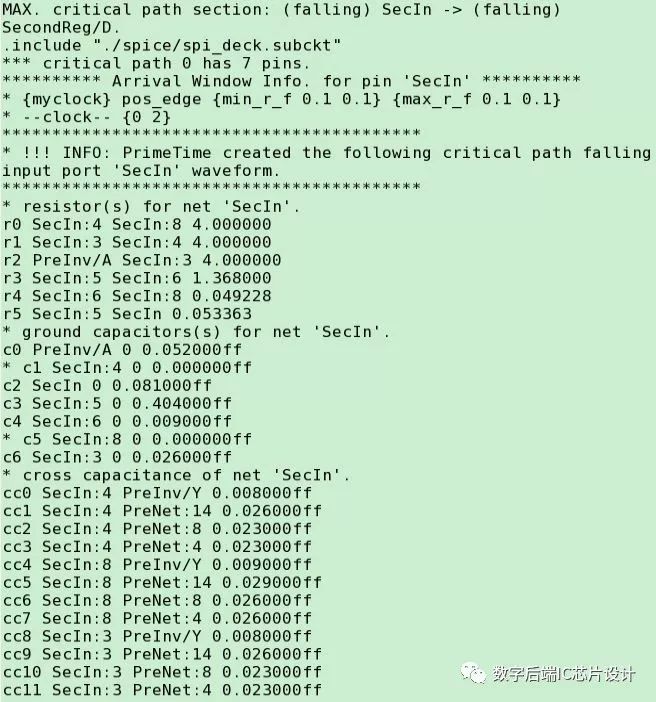

時(shí)序分析基本概念介紹&lt;spice deck&gt;

時(shí)序分析基本概念介紹&lt;generate clock&gt;

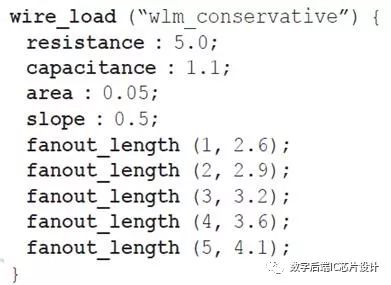

時(shí)序分析基本概念介紹&lt;wire load model&gt;

時(shí)序分析基本概念介紹&lt;ILM&gt;

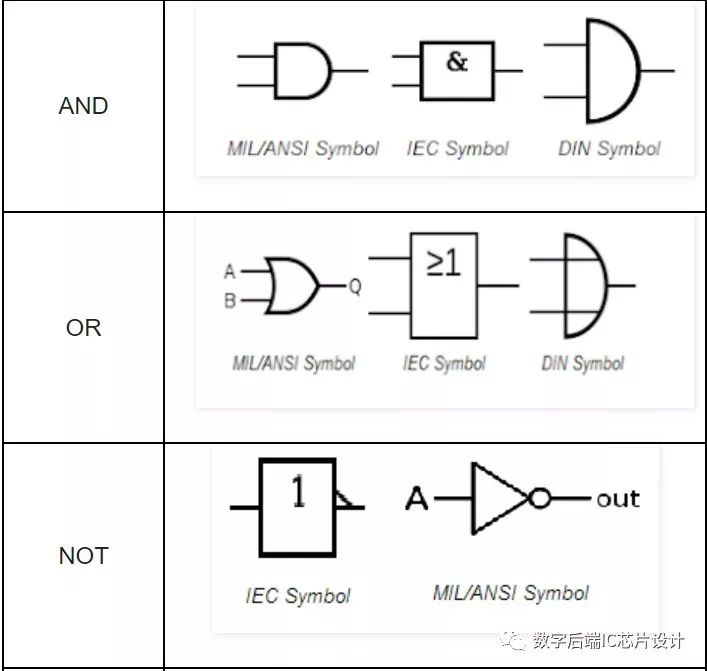

時(shí)序分析基本概念介紹&lt;Combinational logic&gt;

時(shí)序分析基本概念介紹<Critical Path>

時(shí)序分析基本概念介紹<Critical Path>

評(píng)論