在FPGA的設計中的,內部的FIFO和RAM是兩種非常常見的存儲單元。有的場景是只能使用RAM,比如存放表項的時候,有的場景是RAM和FIFO都可以使用,比如存放數據的時候,從功能的角度來講,FPGAer都知道這兩種存儲單元如何使用,但是從工程的角度,比如板上問題的定位、存儲單位讀寫邏輯的修改和維護等方面來看,用FIFO還是用RAM還是有點點講究了。

FIFO

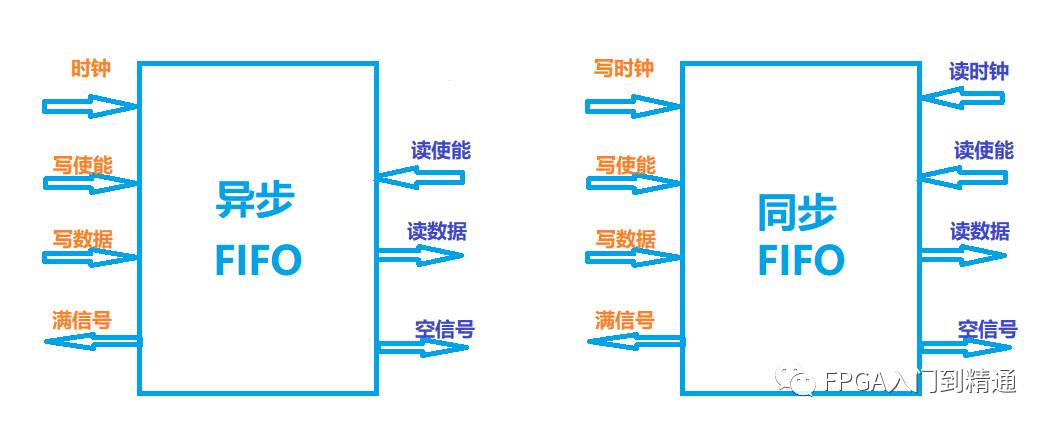

關于FIFO的基本原理,可以參考FIFO的應用,里面對FIFO有非常詳細的介紹。這里從優缺點2個方面重新看到FIFO

FIFO的優點

從使用FIFO的角度來看,FIFO優點很明顯,使用簡單,問題定位也方便。

首先是時序簡單:FIFO通過讀寫使能控制,只要不滿,就可以寫入數據;只要不空,就可以讀出數據。不需要關心數據在內部的存儲位置。

定位問題簡單:在工程實踐中,對FIFO的問題定位比較簡單,常見的錯誤就是上下溢出、非空情況下不讀、長空長滿等。這些現象FIFO一般都給出了相應的信號,所以非常好定位。

擴展性好:FIFO不僅僅是一個緩存,同時也很好的邏輯隔離單元,寫邏輯部分的修改不影響讀邏輯;同理讀邏輯部分的修改不影響寫邏輯,減少了邏輯的耦合性。

FIFO的缺點

FIFO的缺點,首先不能控制地址,也就不能控制數據寫入和讀出的位置,所以不能存放表項;還有一個缺點就是從資源的角度來看,需要有額外的邏輯來控制讀寫,還要產生空、滿信號等;最后在一些特殊的應用場景下,比如對數據從寫入到讀出有延時需求的場景,不同的FIFO設計,有可能不滿足要求。

RAM

關于RAM的基礎原理,前面有也有過詳細的介紹,可以參考RAM的應用。

RAM的優點

存放表項:由于RAM的讀寫地址可以由用戶自己控制,所以RAM是FPGA內存放大表項的幾乎唯一的選擇。

覆蓋:在數據需要丟棄的場景中,可以通過重復寫的方式來覆蓋原來的數據,從而實現丟棄的功能。

回讀:在有的場景中,同一個數據可能需要從緩存中多次讀出,這種場景下RAM也是唯一的選擇。

RAM的缺點

讀寫控制:相比FIFO的讀寫控制,增加了地址這個控制信號。從以往的經驗來看,地址信號是比較容易引起問題的,常見的就是地址錯誤導致數據寫入錯誤。

溢出:由于RAM沒有空滿狀態,RAM作為緩存的時候,寫入和讀出的邏輯,需要從方案上保證不溢出,復雜度略有增加。

問題定位難:除了上述地址錯誤導致寫入的數據錯誤不好定位外,RAM沒有空滿狀態,做緩存的時候,RAM的溢出同樣不好定位。

總結

經過上面的分析,從功能、控制難易程度、問題定位難易程度考慮,我們可以總結出如下幾條原則:

1、表項的存儲采用RAM;

2、對數據有覆蓋和回讀需求的,使用RAM,使用的時候要做好讀寫長度的控制以及狀態的監測;

3、除上述2種情況外,既可以用RAM又可以用FIFO的場景,一律用FIFO;

審核編輯:湯梓紅

-

存儲單元

+關注

關注

1文章

63瀏覽量

16142 -

RAM

+關注

關注

8文章

1367瀏覽量

114528 -

fifo

+關注

關注

3文章

387瀏覽量

43548

發布評論請先 登錄

相關推薦

vs1003中的指令RAM和代碼RAM是干什么用的?

Xilinx FPGA入門連載59:FPGA 片內ROM FIFO RAM聯合實例之功能概述

請問TI的C6678UART外設到底是用的哪個時鐘作為源?

勇敢的芯伴你玩轉Altera FPGA連載90:FPGA片內ROM FIFO RAM聯合實例

Xilinx FPGA片內ROM FIFO RAM聯合實例之功能概述

哪個使用RAM或FIFO更好?

RAM接口控制器系列之FIFO

高速異步FIFO的設計與實現

異步FIFO的設計分析及詳細代碼

如何使用FPGA內部的RAM以及程序對該RAM的數據讀寫操作

FIFO的閾值如何設置

常見的流控機制之fifo與帶外流控

FIFO和RAM,到底用哪個?

FIFO和RAM,到底用哪個?

評論