本文繼續講解時序約束的第四大步驟——時序例外。

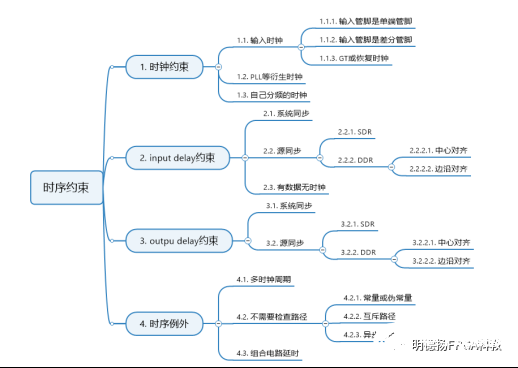

首先看一下圖1,最后一步才進行時序例外的相關約束。再講一下步驟,第一步是時鐘約束,這一步會影響FPGA內部時序,第二步和第三步也會使用生成時鐘的約束作為參考時鐘約束輸入輸出端口。時鐘約束完內部實際邏輯都沒問題之后,第二步是input delay,第三步是output delay,這兩步是對FPGA外圍的接口進行約束。在外圍接口約束都做好之后,才做最后一步,時序例外。

圖1 時序約束步驟

時序例外就是指有些時序路徑是不需要約束的,要把force掉的,或者有些情況是很特殊的。

時序例外做好之后,基本上項目就是完工的一個階段。時序例外一般有幾種情況,第一個是多周期的路徑,第二個是不需要檢查路徑,一般要把這個路徑force掉,而不需要檢查路徑又有三種情況,一種是常亮或偽常亮,第二種是互斥的路徑或時鐘,第三種是異步的時鐘。最后是純組合邏輯延時。

第1節 多周期路徑

1.1、概述

第一種多周期的路徑顧名思義,多周期路徑其實就是指某個電路路徑不可能在一個時鐘周期內完成,需要多個時鐘周期才能得到正確結果,這時需要告知綜合軟件哪條路徑需要幾個時鐘周期才能得到正確結果,綜合軟件根據約束條件對相應路徑進行調整,常見的就是乘法器之類的。

1、多周期約束改變默認的setup和hold的默認檢查方式。

2、設計中有些邏輯并不要求在單周期內完成穩定采樣,在寄存器間不是按照連續時鐘周期改變的時候就多時鐘周期路徑問題。

-通常出現在存在時鐘使能信號的情況。

-從源寄存器、目的寄存器要求數據更新的時間是N個時鐘周期

3、可以使得工具關注于更加難滿足timing的path,便于時序收斂;工具更加關注于真實的關鍵路徑。

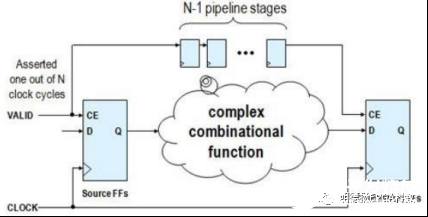

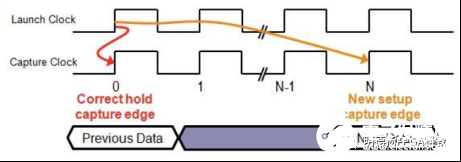

圖2就是一個N個時鐘周期的例子:

圖2 多周期約束實例

1.2、創建多周期路徑例外

多周期路徑通過set_multicycle_path命令進行定義:

set_multicycle_path

?

標志識別哪些路徑使用多周期約束命令,可以使用-from、-through和-to。

? 決定靜態時序檢查的類型,是建立時間還是保持時間。

? 決定multicycle 路徑有多少個時鐘周期。

如上面兩段代碼,分別表示對建立時間和保持時間進行約束,其中從寄存器C到寄存器D的路徑建立時間約束為需要兩個時鐘周期,保持時間需要1個時鐘周期。

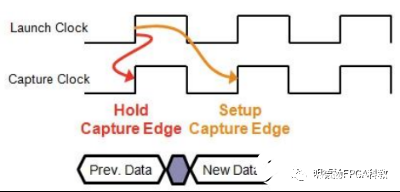

1.3、常規的建立保持時間檢查

靜態時序路徑就是從一個時鐘的元素開始和結束,并且是同一個時鐘驅動的周期內,如圖3所示。

圖3 常見的建立時間、保持時間檢查規則

—建立時間檢查在啟動時鐘邊緣后的目標1個時鐘周期執行,也就是建立時間的發射沿launch edge和捕獲沿capture edge一般情況下相差一個時鐘周期。

—保持時間檢查在啟動時鐘后的目標0時鐘周期執行,保持時間的發射沿launch edge和捕獲沿capture edge一般是重合的,后面講保持時間概念時就清楚了。

而進行多周期約束后,這些路徑的建立時間和保持時間檢查規則會發生相應的改變,因為需要多個時鐘周期才能完成相應的計算,那么建立時間的檢查要求也就會對應的增加。

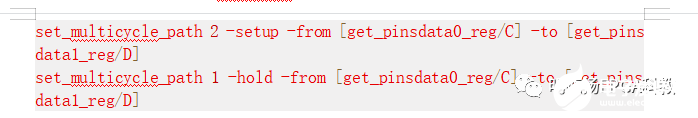

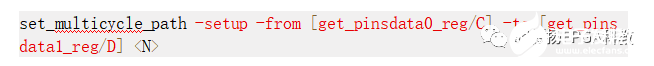

如下面約束:

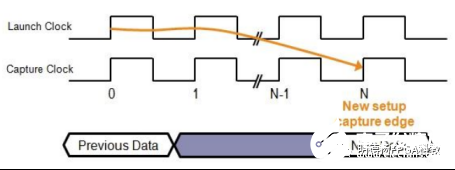

上面代碼把寄存器C到寄存器D的路徑設置為N個時鐘周期,那么捕獲沿setup capture edge 相對于發射沿launch edge會延遲N個時鐘周期,如圖4所示。其實不對建立時間進行多周期約束時,就是N=1。

圖4 N周期建立時間多周期約束

默認情況下保持時間的檢查規則只會比建立時間的檢查規則少一個時鐘周期,這是在進行多周期約束時需要考慮的,如果寄存器C到寄存器D的路徑只做了上面的N個時鐘周期的建立時間約束,那么保持時間約束的檢查規則將還是默認的,即保持時間的檢查規則會變為N-1個時鐘周期,如圖5所示:

圖5 不對保持時間約束的檢查規則

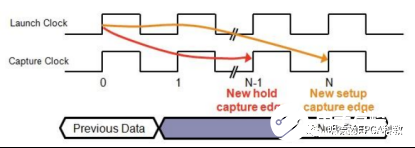

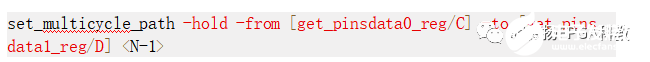

根據保持時間的概念,很明顯圖5的檢查規則是錯誤的,原因是保持時間的目的是讓下一個時鐘的數據不會來得太快,將目前的有效數據刷新,導致數據丟失。為了彌補這個錯誤,還需要對相同路徑的保持時間進行約束,使得保持時間的檢查規則依舊為0個時鐘周期。對應的命令如下:

上述命令會讓該路徑保持時間捕獲沿提前N-1個時鐘周期,與發射沿重合,如圖6所示

圖6 路徑保持時間約束之后檢查規則

上面只是一些簡單的使用方式,多周期約束還可以用來調節信號的相位,比如SDRAM的接口時鐘與內部工作時鐘的相位關系,一般是將一個時鐘經過反相器之后,相位相差90°的兩個時鐘分別作為接口時鐘和內部工作時鐘,其實這個步驟還可以使用多周期約束完成。

其實多周期約束在很多時候都是可以通過程序設計解決的,比如在程序中添加一些指示信號,或者打拍來完成多個周期的等待。所以明德揚一般不會用多周期約束,都是在程序設計時就會去考慮和解決這些問題,也推薦大家在設計時就去考慮這些延遲問題,不要等最后的時序約束才解決這些問題。

第2節 不需要檢查路徑

第二個不需要檢查路徑是重點講解的內容,什么是不需要檢查路徑呢?第一種就是常量或偽常量信號。

什么叫常量或偽常量信號?比如一個單bit信號一般會有高低兩種電平,會存在電平變換。但是也會存在一些信號會被賦值成常數,一直為高電平或者低電平,電平狀態不會改變。所以通過其它時鐘、跨時鐘域處理的時候,其實是不需要處理的。因為它不會變,那在其他時鐘上升沿時,該信號是不會變的,建立時間和保持時間是一直滿足的,就不會有壓穩態。這種情況下,該信號不會存在時序不滿足的情況,常量或偽常量信號是不需要對它進行約束的,可以把它排除掉。

第二種是互斥的路徑或時鐘,其實就是雙向端口,即雙向端口inout 類型的端口,其輸入路徑與輸出路徑其實是沒有關系的,故把它排除掉。

第三種是異步的時鐘,是最常見的,也是FPGA肯定會用到,也一定要排除掉的。而且在任何一個項目里面,如果使用多個時鐘,一定會用到的異步時鐘處理。一般都會通過一些跨時鐘域的處理方式之后,就可以做相關約束了。但把相關路徑設置為不需要檢查路徑之前,一定要先對這寫路徑的時鐘已經做跨時鐘域處理。比如已經打了兩拍,或者通過一個異步FIFO、雙口RAM把它隔離了,否則這時候把它force 掉,就是會出現錯誤。

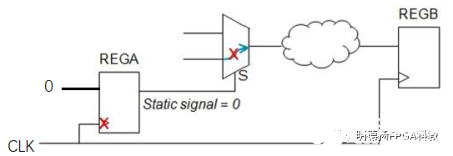

2.1 常量和偽常量信號

首先是常量或為常量信號,如圖7,數據選擇器的S端雖然是一個經過觸發器輸出的信號,但觸發器REGA的輸入信號一直為零,導致數據選擇器的S端也一直為零。只要一直是零,那這個路徑就可以把force 掉,即不用去分析該路徑,包括經過這個數據選擇器的路徑也是不用分析的。

圖7 實例

約束語句語法如下:

– set_false_path

–

表示約束的路徑。

– 指定類型-setup 或者 –hold,不指定時建立setup和保持hold檢查都受到影響

所以圖7可以進行如下約束:

-set_false_path -from [get_cells REGA]

-set_false_path -through [get_pins_MUXA/I1]

其中第一句表示從REGA輸出的信號都不需要檢查時序,第二句表示綜合軟件對經過數據選擇器的信號也不需要進行時序檢查。

在一般情況下,如果是同一個時鐘,可以也不用約束。但如果在跨時鐘,而又沒有做跨時鐘域處理。其值是永遠不會變的,就可以通過set false path這種約束方式來告知綜合軟件不用檢查相關路徑的時序。

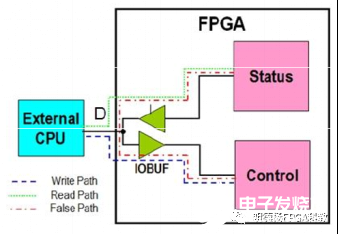

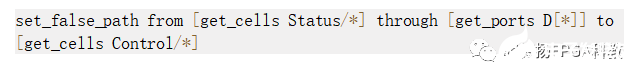

2.2 互斥路徑_雙向端口

第二種是互斥路徑,即雙向端口。如圖8的inout類型信號端口示意圖,比如這個D端口是inout類型,那這種路徑哪個是不需要分析的呢?

其實輸入路徑與輸出路徑對應的寄存器是不需要分析的,如圖8中紅色虛線所示路徑是不需要分析的,綠色代表輸出路徑,而藍色代表輸入路徑,這兩條都是需要綜合軟件分析的,但是紅色是輸出經過D端口后到達輸入寄存器的,所以該路徑是不需要分析的。即從Status經過D端口到達Contorl的路徑是不需要分析的。

圖8 inout類型端口

相應的約束語句如下,從Status寄存器,經過D端口到達Control的信號都不需要檢查其時序,其中*表示通配符。

2.3 異步時鐘

第三個異步時鐘,再強調一下,一般比較大的系統,不可避免會有多個時鐘。多個時鐘域下面的信號會存在交互,就會跨時鐘域。綜合軟件在對設計進行綜合和時序分析后,一般會對這些路徑報錯,提示開發人員這些路徑存在時序違逆。這時候發現異步時鐘域的信號肯定不能滿足建立時間要求,但是一定要用不同的時鐘,那怎么辦呢?

一般會做異步時序處理,比如通過打兩拍,把亞穩態出現的機率降低,或者是用異步FIFO、雙口RAM把兩個時鐘域的信號同步。這樣做了異步時鐘域處理之后,綜合軟件仍然會報告這個時序不滿足建立時間保證要求,那怎么辦呢?

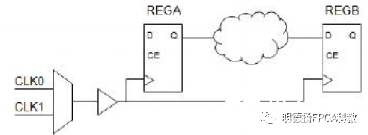

這時就可以把這個報告錯誤的路徑給屏蔽掉,就是告知軟件不要去分析了,這段路徑已經人為處理過了,時序是沒有問題的,如圖9所示,這個系統會選擇CLK0或者CLK1中的一個作為系統時鐘,很顯然時鐘域CLK0到CLK1之間的路徑是不需要進行分析的,可以使用set_false_path進行約束。

圖9 多時鐘域信號

這種會存在兩種約束方式,方式一如下,表示綜合軟件從CLK0到CLK1、從CLK1到CLK0的路徑都不需要分析。

set_false_path -from [get_clocks CLK0] -to [get_clocks CLK1]

set_false_path -from [get_clocks CLK1] -to [get_clocks CLK0]

方式二是通過set_clock_groups進行約束,如下所示,表示綜合軟件不需要檢查CLK0與CLK1之間的路徑。

set_clock_groups-physically_exclusive -group CLK0 -group CLK1

這樣就可以正確的處理,綜合軟件不去對這些路徑進行分析,也就會不會提示錯誤了。但強調一點,首先一定要做異步時序處理,然后才能把這個路徑給force掉。假如沒有做異步時序處理,而綜合軟件報告要說時序出錯了,開發人員不對時序做處理,而是直接把這個報告給屏蔽掉了,這就是典型的解決不了問題就解決提出問題的人。后續系統功能出現問題,而綜合軟件報告的錯誤又被屏蔽了,這可能會出現災難性后果。所以在使用set_false_path忽略路徑的時候,特別是異步時鐘,要特別小心。要確保真的做了時序處理,才能把相關路徑force 掉。

語句相對簡單,但非常重要,在不需要檢查路徑類型中,這個是最常見的,也是最重要的,也要小心處理的一種類型。

第3節 組合電路延時

第三種情況就是組合邏輯延時。組合邏輯延時是什么情況?

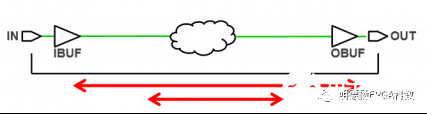

假如FPGA的兩個端口,一個作為輸入管腳,一個作為輸出管腳。信號從輸入管腳進入之后,會經過一些加法器、乘法器、減法器等組合邏輯電路,然直接從輸出管腳輸出。期間不會經過時序邏輯電路,即不會經過觸發器,沒有時鐘參與,如圖10所示。

圖10 純組合邏輯傳輸示意圖

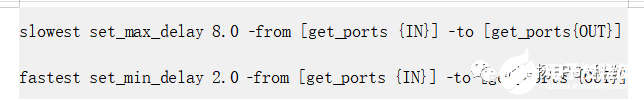

中間沒有經過任何時鐘的情況,此時需要告知綜合軟件這條路徑的最大傳輸延遲和最小傳輸延遲是多少,即輸入信號最快和最慢傳輸多久能得到輸出。約束如下:

上述語句表示從IN端口到OUT端口最大延遲是8ns,即信號傳輸最慢的時候,需要8ns才能得到輸出。最小延遲是2ns,即信號傳輸最快的時候,只需要2ns就能得到輸出。一般這個延遲都不會很大,應該是沒有影響的,也不推薦這種設計方式。

第4節 總結與建議

這是實際例外的情況,還是按照前面的順序去找到對應情況,按要求進行約束。

內容最多的是多周期路徑,做了簡單的介紹。最核心是設置異步時序約束的內容,簡單但重要且常用。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602022 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

時序約束

+關注

關注

1文章

115瀏覽量

13409

發布評論請先 登錄

相關推薦

工程師談FPGA時序約束七步法

VIVADO時序約束及STA基礎

時序約束之時序例外約束

【時序約束資料包】培訓課程Timing VIVADO

正點原子FPGA靜態時序分析與時序約束教程

時序約束連載02~時序例外

時序約束連載02~時序例外

評論