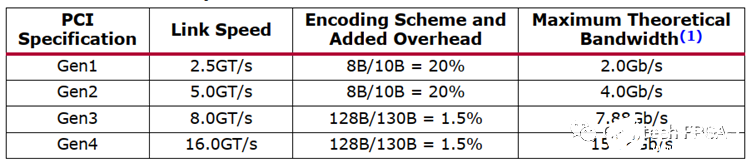

AMD FPGA自帶PCIE硬核,實現了PCIE協議,把串行數據轉換為并行的用戶數據,以UltraScale系列FPGA為例,其支持Gen1.02.03.04.0,1~16 Lanes,如下圖所示:

另外當前最新7nm系列器件Versal? ACAP可支持到PCIE Gen5.0,單個Lane可達32G的線速率,如下圖所示:

1.1 PCIE IP功能介紹

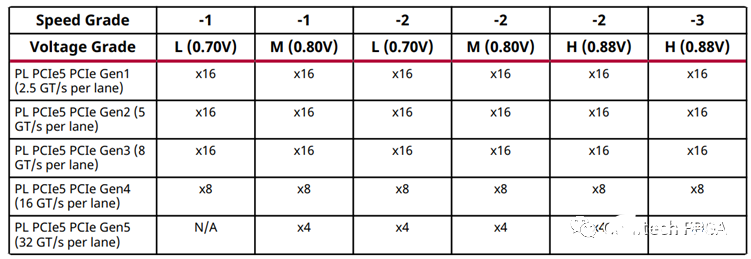

用戶接口采用AXI接口實現PCIE TLP報文收發,從而完成PCIE傳輸事務的收發,最終實現PCIE的各種數據傳輸模式,系統架構如下圖所示:

圖左側為FPGA PCIE IP,實現了PCIE協議,其與用戶邏輯的數據交互主要通過AXI CQ,CC,RQ,RC四個接口,可以實現PCIE上行和下行的數據傳輸。

1.2 PCIE協議TLP報文介紹

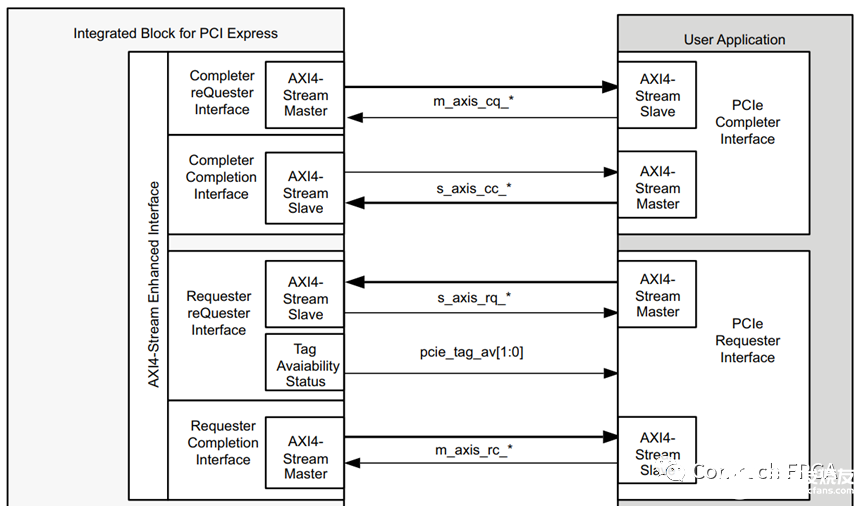

使用PCIE IP用戶需要了解PCIE協議,至少了解TLP報文的構造,如下圖所示為32位地址寫請求TLP報文:

R:保留位,一般填0;

Fmt:報文長度類型,指示當前TLP報文是3DW長度還是4DW長度(此處主要是跟地址位寬相關,PCIE協議可支持32位地址和64位地址);

Type:包類型,指示包括Mrd(讀數據)、Mwr(寫數據)、Cfg(配置PCIe)、Msg(消息事務)、Cpl(讀地址數據請求后返回的數據包);

TC:傳輸優先級,數值越大表示優先級越高;

Attr:包屬性,指示當前包是順序或者是亂序,cache一致性等;

TH:PCIe V2.1 總線規范引入的一個重要功能。TLP 的發送端可以使用 TPH 信息,通知接收端即將訪問數據的特性,以便接收端合理地預讀和管理數據,一般很少應用;

TD:指示接收端是否需要做ECRC校驗;

EP:指示當前TLP包的有效性;

AT:地址種類,與 PCIe 總線的地址轉換相關;

Length:指示TLP長度;

Requester ID:請求者ID,包括PCIe設備的總線號(Bus Number)、設備號(Device Number)和功能號(Function Number),通過該ID可以找到對應的目標設備;

Tag:數據包標簽,可以指示當前TLP數據包是屬于哪一組數據中分拆的數據塊;

Last DW BE:指示最后一個DW中有效的字節,主要是針對在傳輸數據粒度比較小的情況,比如最小粒度為1字節;

1st DW BE:指示第一個DW中有效的字節。

1.3 PCIE IP邏輯設計

用戶在實現PCIE數據傳輸功能時可通過上圖中AXI CQ,CC,RQ,RC四個接口來完成各種PCIE事務的數據收發:

RQ:請求者請求接口,通常是主機向終端設備發送數據傳輸請求;

RC:請求者完成接口,通常是終端設備向主機發送需要的返回數據;

CQ:完成者請求接口,通常是終端設備向主機發送數據傳輸請求;

CC:完成者完成接口,通常是主機向終端設備發送需要的返回數據;

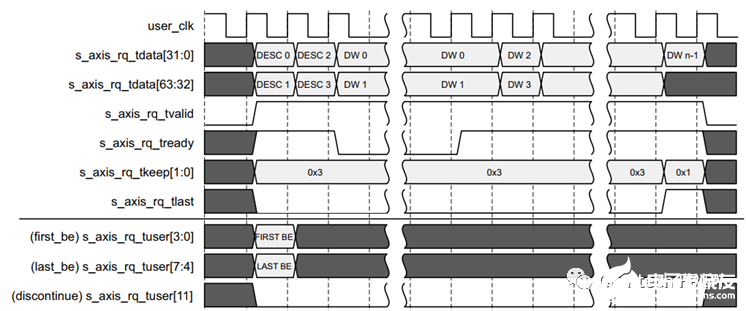

用戶需要通過這4個接口構造TLP報文可以實現從主機到終端或者終端到主機的訪問請求和相應的數據傳輸,下面是主機向終端發起寫數據請求的時序:

用戶在邏輯設計時可以先通過右鍵IP生成一個example工程,工程里面就有構造TLP報文的代碼,用戶可以在這個工程代碼上修改TLP報文的相關數據來實現具體的數據傳輸需求。

二、AMD PCIE DMA功能實現

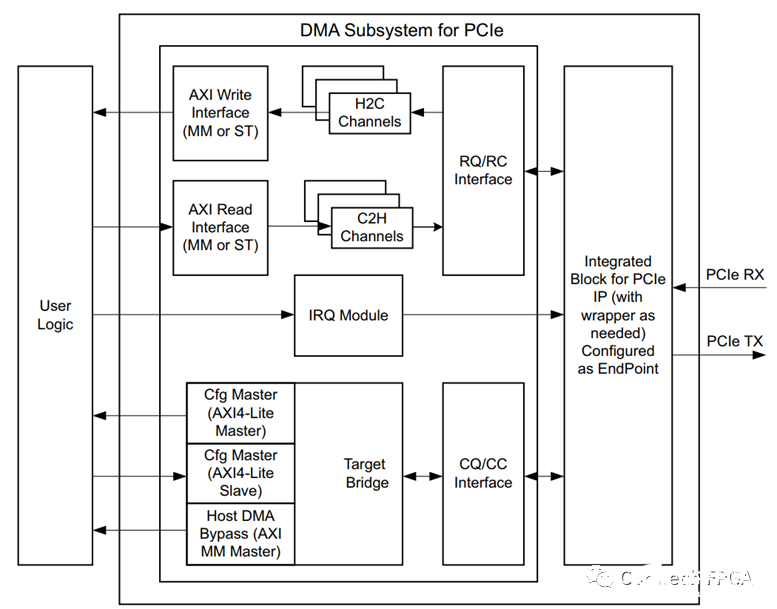

AMD PCIE DMA功能主要是通過XDMA IP來實現,其作用本質上是通過這幾個接口實現PCIE DMA傳輸流程,用戶不需要關注PCIE TLP報文的構造細節,只需要通過XDMA的AXI接口完成數據傳輸即可,如下圖所示:

用戶只需關注AXI用戶接口的邏輯設計,通過該接口就可以實現DMA傳輸。另外,AXI用戶接口包括MM接口和ST兩種接口,MM接口是可以直接對接內存,其包括了地址控制,可以直接實現內存讀寫。

2.1 XDMA AXI-MM接口實現DMA傳輸

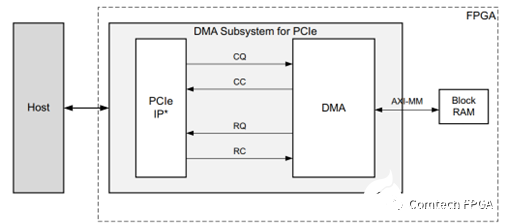

AXI-MM接口的操作相對簡單,其與用戶邏輯對接的接口為標準的AXI接口,包括了地址信息,可以直接對接內存,最簡單的方式就是例化一個AXI接口的RAM直接對接,PC端就可以直接訪問該RAM,如下圖所示:

AXI-MM接口主要應用場景是直接訪問FPGA內存,但對于視頻流,采集數據流等場景,特別是需要用到多通道的場景通常采用ST接口會更加方便。

2.2 XDMA ST接口實現DMA傳輸

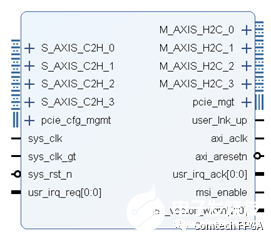

ST(AXI4-Stream)接口是實現數據流傳輸接口,用于傳輸連續的數據流,比如視頻數據流,特別是在實現多通道DMA的情況下通常會采用該接口,如下圖所示:

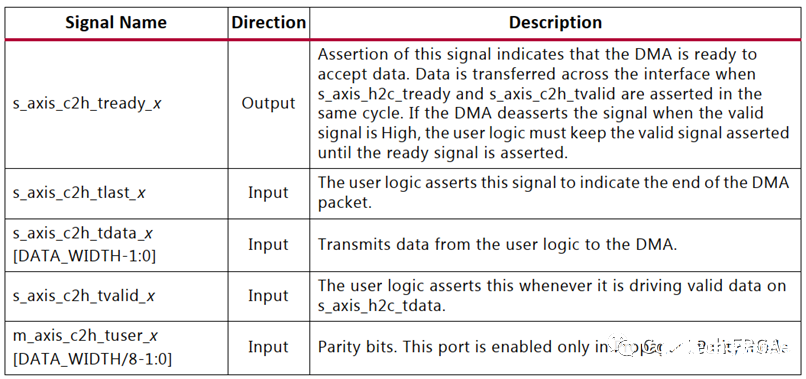

S_AXIS_C2H是終端設備向主機發送數據接口,S_AXIS_H2C是主機向終端設備發送數據接口,均為AXI Stream接口,只實現數據流傳輸,典型特征是不傳輸地址,其端口如下圖所示:

其時序跟上述PCIE IP的AXI接口類似,所以,通過XDMA的ST接口可以很方便實現數據流傳輸,只需要跟PC驅動程序配對好地址和長度信息,邏輯設計只需要通過ST接口收發數據。

2.3 DMA邏輯設計方法

邏輯與主機上層軟件實現DMA數據傳輸主要有查詢和中斷兩種方式,以ST接口為例,邏輯可以通過AXI LITE接口實現PC的寄存器訪問,PC可以通過查詢寄存器來確定是否可以啟動DMA下發數據,或者通過發起DMA獲取邏輯需要上傳的數據,邏輯根據當前數據需要上傳或者允許PC下發數據的具體情況來設置寄存器的狀態。

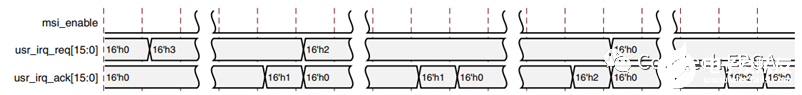

中斷模式首先要在例化XDMA IP時要選擇一個中斷,IP自動生成一個可供用戶產生中斷的接口,時序如下圖所示:

用戶產生中斷的方法很簡單,只需要拉高usr_irq_req,等待usr_irq_ack拉高即可產生中斷。需要注意的是當usr_irq_ack拉高時用戶不能立刻把usr_irq_req拉低,因為此刻不能確定PC已經響應并完成中斷處理,最簡單的方式是設置一個清中斷寄存器,PC通過向這個寄存器寫1來通知邏輯,中斷事務已經被處理完成。

另外,PCIE協議支持3種中斷:

INTx中斷:主要是為了兼容PCI設備,是電平觸發中斷;

MSI中斷:消息中斷,PCIE設備通過構造對應的中斷消息發送到主機,從而觸發中斷;

MSI-X中斷:是MSI中斷的擴展,可以通過中斷向量表的方式把中斷個數擴展到2048個;

當PC啟動DMA下發數據時,XDMA IP會通過H2C接口向邏輯發送數據,邏輯可以通過s_axis_h2c_tready信號來決定是否允許數據下發;當邏輯向PC上傳數據時可通過C2H接口向PC傳輸數據,在發送數據前邏輯需要向PC產生一個中斷,PC檢測到中斷后就會啟動DMA上傳數據,邏輯側看到的是s_axis_c2h_tready信號拉高,說明邏輯可以開始通過C2H接口發送數據給PC。所以,整個DMA傳輸都是由PC發起的,無論是上傳還是下發數據,邏輯只是被動完成數據傳輸。

值得注意的是當使用多通道DMA時每個通道的操作是完全獨立的,包括ST接口和中斷都是獨立的,相關的寄存器用戶最好也采用獨立的寄存器來實現與PC的交互。

責任編輯:彭菁

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598900 -

amd

+關注

關注

25文章

5376瀏覽量

133378

發布評論請先 登錄

相關推薦

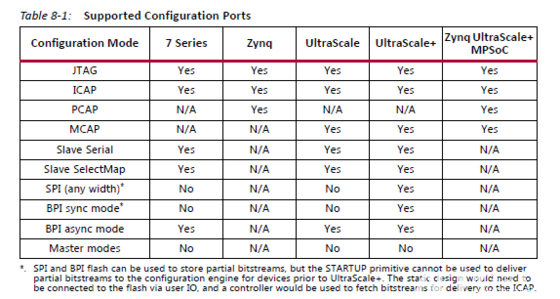

基于PCIE(mcap)的部分可重構實現方案

基于Xilinx V6的PCIE DMA高速傳輸模塊

Xilinx PCIe Master DMA設計

PCIe DMA設計實現

關于PCIE DMA操作的一個疑問

尋求fpga大牛開發一個簡單的fpga pcie設備

如何通過PCIe進行FPGA到PC的通信?

如何利用PCIe DMA總線實現一個基于FPGA的PCIe 8位數據采集卡?

基于FPGA的PCIe總線接口的DMA控制器的實現并進行仿真驗證

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

Xilinx高性能PCIe DMA控制器IP,8個DMA通道

基于AMD FPGA的PCIE DMA邏輯實現

基于AMD FPGA的PCIE DMA邏輯實現

評論