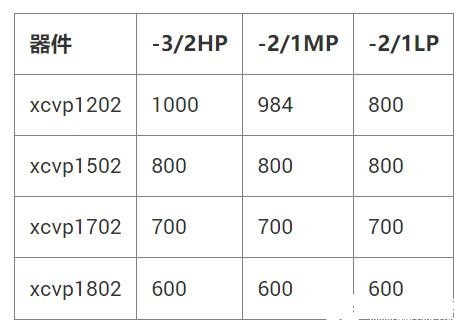

對于較長的時鐘布線,可以降低時鐘網絡的 FMAX。下表列出了不同器件/速度等級組合下的最差情況 FMAX。

在 2022.2.2 版本中,DRC BFGCHK-1 會將設計中每個時鐘網絡的頻率與以上最差情況 FMAX 表中的 FMAX 數值進行比對。

如果時鐘網絡的頻率超出最差情況 FMAX,那么 DRC 會阻止比特流生成,因為按此頻率操作時鐘可能不安全。

[DRC BFGCHK-1] BUFG_has_device_restricted_FMAX:如果使用最大時鐘擴展范圍,時鐘信號線 design_1_i/clk_wizard_0/inst/clock_primitive_inst/clk_out1 上的周期要求會超出此器件的 FMAX 規格 (600.00 MHz)。請參閱答復記錄 AR34820,了解您是否可以為自己的時鐘網絡豁免此 DRC 檢查。

* 注釋:請參閱以下“Versal 時鐘設置背景”部分,獲取有關時鐘拓撲結構擴展范圍的更多詳細信息。

解決方案:

當 DRC 檢查 BFGCHK-1 報告違例時,并不一定暗示時鐘信號線無法支持所需時鐘頻率,因為 DRC 僅基于最差情況 FMAX 檢查最大時鐘擴展范圍。 為根據時鐘網絡的實際擴展范圍來判定其支持的 FMAX,我們為每個時鐘提供了一個 Tcl 腳本,用于計算最大時鐘擴展范圍和 FMAX。

如果針對每條時鐘信號線計算所得 FMAX 低于時鐘網絡的實際時鐘頻率,那么可豁免 DRC,設計可以繼續生成器件鏡像。以下是如何豁免 DRC 的示例:

create_waiver -type DRC -id {BFGCHK-1} -user "" -desc "Ignore this DRC as all clocks are within FMAX specification."

檢查確認所有時鐘都在給定時鐘擴展范圍的 FMAX 規格范圍內之后,僅限在器件鏡像生成前將 DRC 嚴重性降級。

如果您重新編譯設計,則可更改時鐘信號線的最大擴展范圍,并且需要在新布線的檢查點上運行 validate_fmax Tcl 命令,查看是否可將 DRC 嚴重性降級。

Tcl 腳本詳細信息

提供的 validate_fmax.tcl Tcl 腳本可用于計算當前設計中針對每個時鐘網絡遍歷的時鐘區域的最大數量,并從表中查找關聯的 FMAX 值。該腳本計算遍歷的時鐘區域數量時會考量不同時鐘布線資源。 例如,穿過 XPIO 時鐘區域的時鐘布線不影響 FMAX 并且不會添加到遍歷的時鐘區域數量中用于計算時鐘網絡的 FMAX。

使用 source 運行 Tcl 腳本時,會創建 validate_fmax Tcl 命令。運行 validate_fmax Tcl 命令時,如果沒有 FMAX 違例,那么此命令會返回 1,如果設計中任意時鐘信號線違反 FMAX 規格,則返回 0

source -quiet ./validate_fmax.tcl

validate_fmax

您也可以運行 validate_fmax 并搭配 -verbose 選項來提供設計中每條全局時鐘信號線的詳細信息。

% validate_fmax -verbose

Global clock net: clknetwork/inst/clock_primitive_inst/clk_out4:

PERIOD: 16.252

FMAX: 1070

Number Fabric CR traversed: 4

Global clock net: clknetwork/inst/clock_primitive_inst/clkout2_primitive_bufg:

PERIOD: 11.327

FMAX: 1070

Number Fabric CR traversed: 4

注釋:該腳本應僅在已布線的設計/DCP 上使用。

Versal 時鐘設置背景

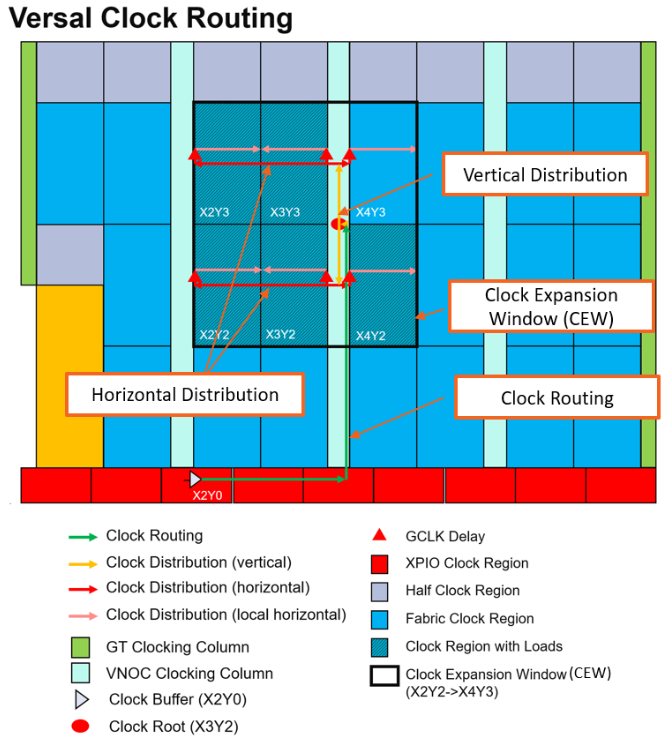

Versal 器件中的全局時鐘網絡的入口點是全局時鐘緩沖器。時鐘信號線通過水平和垂直布線資源,從全局時鐘緩沖器布線到時鐘根。 時鐘使用垂直分布 H 樹狀和水平分布從時鐘根分布到負載時鐘區域。

下圖顯示了 SLR0 中跨時鐘區域 X2Y2 到 X4Y3 的時鐘的時鐘布線示例。 X2Y0 中的全局時鐘緩沖器用于驅動時鐘穿過 XPIO 時鐘區域到達 VNOC 時鐘設置列,而后再到 X3Y2 中的時鐘根的過程。 時鐘從中分布到所有負載時鐘區域。 負載時鐘區域 X2Y2 和 X2Y3 都位于距離時鐘根最遠處,因此都存在最大數量的躍點。

如何為時鐘網絡改善 FMAX

可通過減少躍點數量或者選擇最優時鐘列來改善時鐘網絡的 FMAX。 穿過 VNOC 時鐘列的時鐘布線所得 FMAX 會好于穿過器件左右兩側 GT 時鐘列的時鐘布線。 穿過負載時鐘區域中心的 VNOC 列布線的時鐘到達最遠端負載時鐘區域過程中所產生的躍點數量較少,故而能得到更好的 FMAX。 您可使用 USER_CLOCK_ROOT 約束強制使用與負載時鐘區域相關的更接近中心的時鐘列。如需了解有關 USER_CLOCK_ROOT 的更多信息,請參閱UG1387。

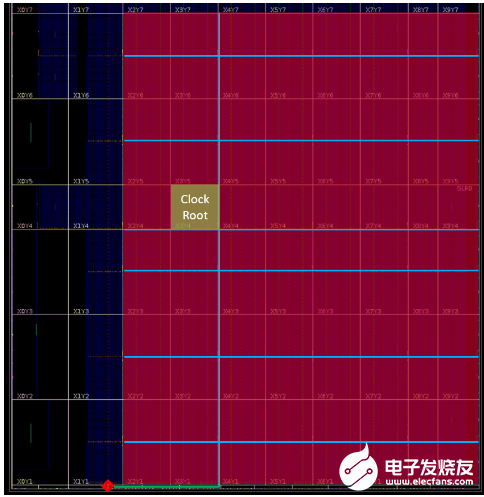

在以下示例中,XPIO 時鐘區域 X3Y0 中的 BUFGCE 用于驅動時鐘擴展窗口中的時鐘負載,該窗口從 X2Y1 擴展至 X9Y6。 時鐘根偏離中心,位于時鐘區域 X3Y4 處。 當時鐘根偏離中心時,相比于位于水平方向時鐘擴展窗口上中心位置的時鐘根,時鐘區域的最大躍點數量會增加。

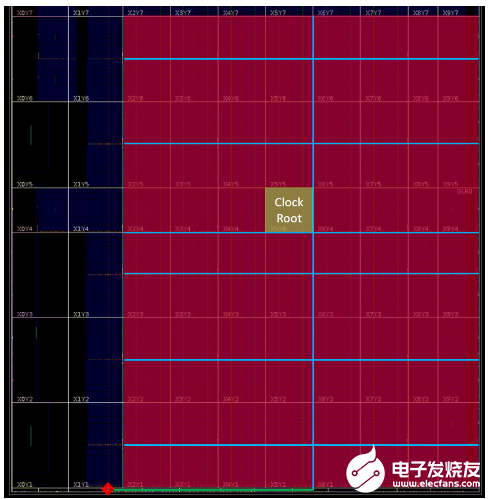

將時鐘根移至 X5Y4 會選擇更偏向中心的 VNOC 列用于時鐘布線,從而減少躍點數量并提高 FMAX。 在時鐘網絡的 FMAX 計算中,不會計入從 BUFGCE 穿過 XPIO 時鐘區域到 VNOC 的時鐘布線。

審核編輯:湯梓紅

-

時鐘

+關注

關注

10文章

1721瀏覽量

131378 -

布線

+關注

關注

9文章

766瀏覽量

84295 -

DRC

+關注

關注

2文章

148瀏覽量

36132

發布評論請先 登錄

相關推薦

貿澤電子開始備貨Maxim Integrated的多種適用于醫療耗材的安全器件

適用于STM32芯片的開發教程

適用于家電應用的優化參考設計

適用于PDA的PLC編程系統開發

USB標準適用于哪些應用

適用于節能家電的創新功率轉換器件

英飛凌推出適用于節能家電的創新功率轉換器件

適用于Arduino的Adafruit NeoPixel Shield

適用于SSIT器件的Versal Fmax限制

適用于SSIT器件的Versal Fmax限制

評論