76889 - Versal HDIO/MIO:以 3.3V 或 2.5V 上電時,如果使用三態(tài),則在數(shù)據(jù)與三態(tài)之間可能存在爭用條件是一篇面向 Versal ACAP 的設(shè)計咨詢,其中詳述了三態(tài)控制發(fā)生更改時的 MIO 要求和 HDIO 要求。

本文則著重探討 JTAG TDO 用例。

如果 VCCO_503 為 3.3V 或 2.5V,那么三態(tài)數(shù)據(jù)爭用條件可能會影響 JTAG TDO_503。

由此導(dǎo)致 TDO 輸出可能無法驅(qū)動可編程邏輯 (PL) 的 LSB 位的“1”值。此問題不影響處理子系統(tǒng) (PS) Arm DAP 和 PL BYPASS 數(shù)據(jù)輸出功能特性。

解決方案

您可使用以下選項作為此問題的變通方法:

1) 將 VCCO_503 設(shè)為 1.8V。

注釋:如果您使用的是 SSIT 器件,請聯(lián)系賽靈思技術(shù)支持。

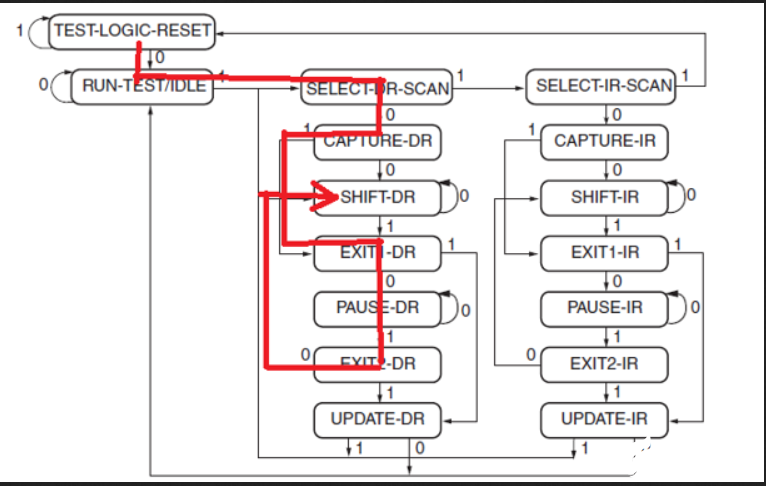

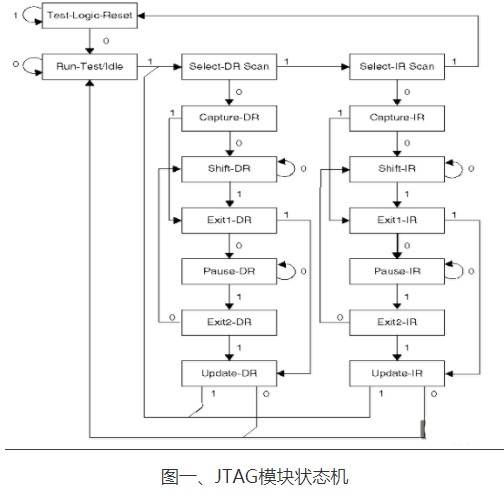

2) 如果 VCCO_503 必須設(shè)為 2.5V 或 3.3V,那么可改用備用 TAP 狀態(tài)路徑來進(jìn)入“Shift IR”(移位指令寄存器)或“Shift DR”(移位數(shù)據(jù)寄存器)狀態(tài),以避免發(fā)生此問題,如下圖所示。

在 Vivado 2021.2 及后續(xù)軟件版本中,如果在 JTAG 鏈中包含 Versal 器件,那么該工具會默認(rèn)自動檢測并使用備用 TAP 狀態(tài)路徑。

在 2021.2 版本及后續(xù)軟件版本中,用戶也可以使用以下命令手動啟動 hw_server:

hw_server -e "set jtag-pause-before-shift 2"

在 XSDB 2021.2 及后續(xù)軟件版本中,使用以下命令“連接”后,必須應(yīng)用 configparam 命令:

xsdb% configparam jtag-pause-before-shift 2

此備用路徑僅顯示進(jìn)入移位 DR 狀態(tài)。該備用路徑應(yīng)同樣用于移位 IR 狀態(tài)。

以上 configparam 會將此變通方法應(yīng)用于 Shift-DR 操作和 Shift-IR 操作。

3) 如果 VCCO_503 必須設(shè)為 2.5V 或 3.3V,請向您的 JTAG 工具供應(yīng)商申請采用此備用 TAP 狀態(tài)路徑作為 JTAG 變通方法。

審核編輯:湯梓紅

-

寄存器

+關(guān)注

關(guān)注

31文章

5250瀏覽量

119179 -

JTAG

+關(guān)注

關(guān)注

6文章

392瀏覽量

71422 -

指令

+關(guān)注

關(guān)注

1文章

595瀏覽量

35499 -

Versal

+關(guān)注

關(guān)注

1文章

151瀏覽量

7596

發(fā)布評論請先 登錄

相關(guān)推薦

簡單認(rèn)識JTAG接口

TDO沒有信號切換

哪里可以找到將CC2640 5*5 JTAG TDO 與TDI復(fù)用為IO口的資料?

tms320c6416的TCK、TDO、 TDI、TRST、TMS、EMU等能否直接接到JTAG上?

XC2C384是否具有TDO引腳的內(nèi)部上拉?

在JTAG配置階段TDO沒有給出任何結(jié)果是為什么?

S32K-連接失敗- JLink日志:無法測量總IR len,TDO恒定高的問題如何解決?

JTAG的原理

jtag工作原理詳解

基于S698PM芯片的JTAG控制G接口的設(shè)計及應(yīng)用

IEEE1149.1標(biāo)準(zhǔn)JTAG接口與ISP接口,ISP interface

STM32單片機(jī)JTAG的復(fù)用方法解析

JTAG接口定義

構(gòu)建多電壓JTAG鏈

JTAG的基本原理

Versal:JTAG TDO

Versal:JTAG TDO

評論