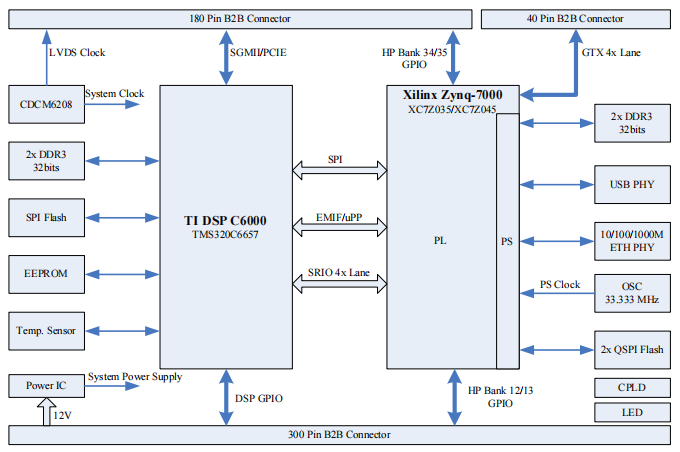

[基于TI KeyStone架構C6000系列TMS320C6657雙核C66x 定點/浮點DSP以及Xilinx Zynq-7000系列SoC處理器XC7Z035-2FFG676I設計的異構多核評估板,由核心板與評估底板組成。]

1.1 ZYNQ與DSP之間EMIF16通信

1.1.1 例程位置

ZYNQ例程保存在資料盤中的DemoZYNQPLFPGA_DSP_EMIF文件夾下。

DSP例程保存在資料盤中的DemoDSPXQ_EMIF16文件夾下。

1.1.2 功能簡介

實現DSP與ZYNQ PL端之間EMIF16接口傳輸功能。

DSP首先通過EMIF16接口往ZYNQ PL端發送4096字節數據,然后再讀回來,并檢測數據是否有錯,數據發送、讀回以及錯誤情況實時打印。

ZYNQ PL端開辟了一塊RAM空間,用于存放DSP通過EMIF16接口寫入的數據,同時用作DSP通過EMIF16接口讀數據時的數據源。

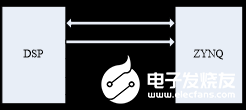

DSP與ZYNQ PL端之間EMIF16接口連接示意圖如下圖所示:

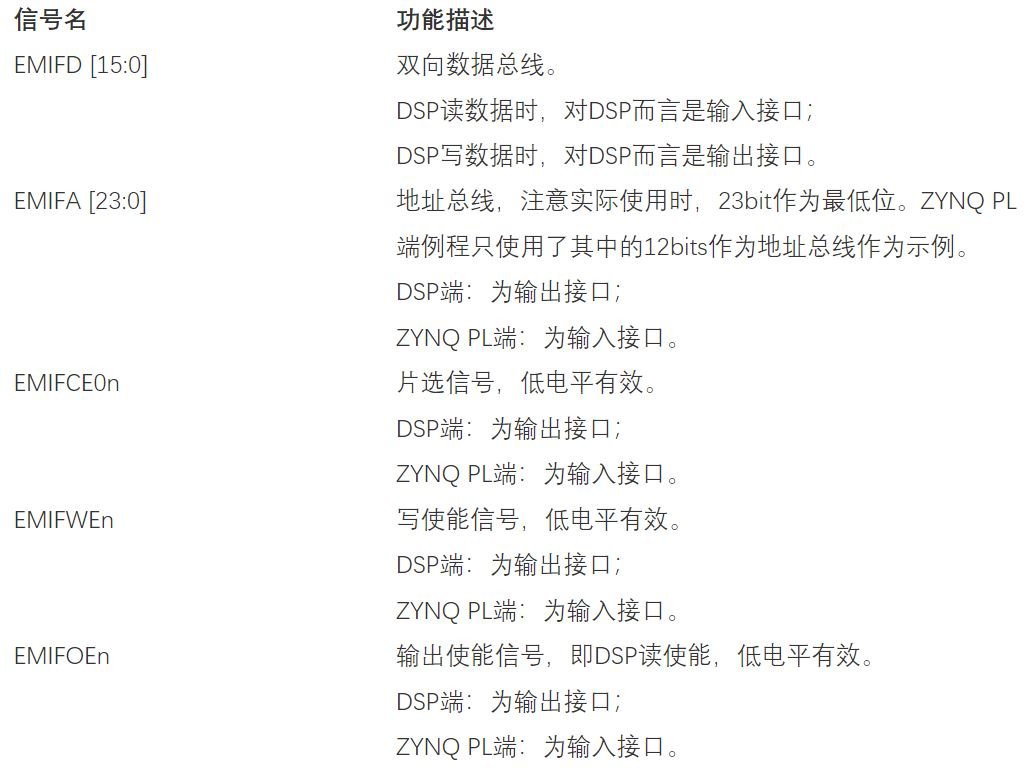

EMIF16接口信號定義說明如下表格所示:

1.1.3 例程使用

1.1.3.1 加載運行ZYNQ程序

1.1.3.1.1 打開Vivado工程

打開Vivado示例工程:

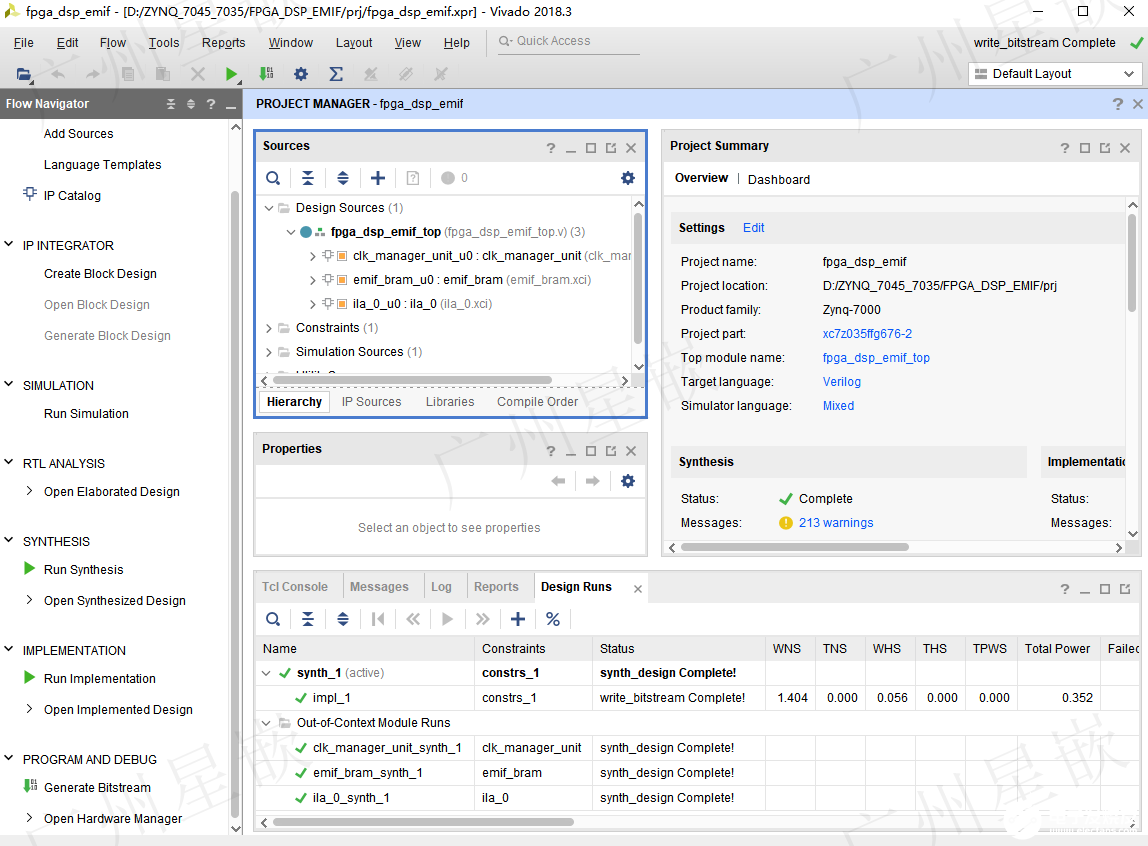

工程打開后界面如下圖所示:

1.1.3.1.2 下載ZYNQ PL程序

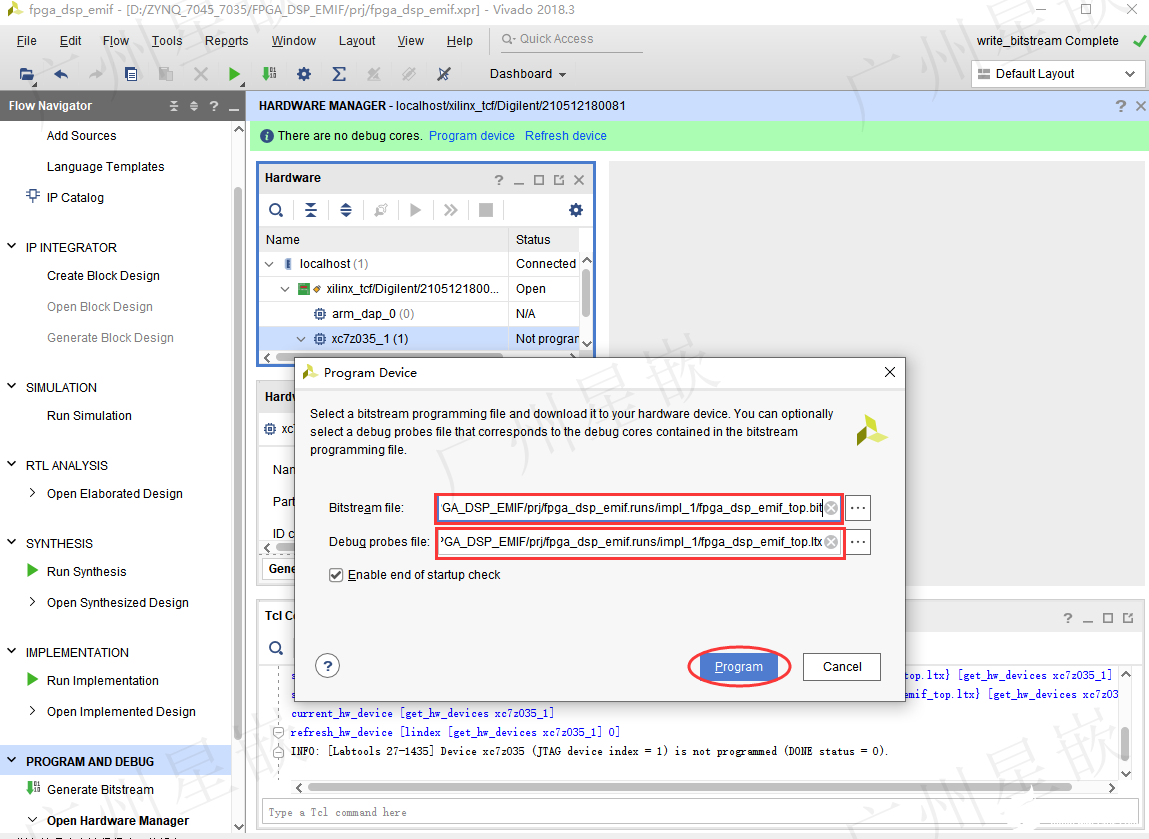

下載bit流文件fpga_dsp_emif_top.bit,并且配套fpga_dsp_emif_top.ltx調試文件,如下圖下載界面所示:

1.1.3.2 加載運行DSP程序

1.1.3.2.1 CCS導入例程

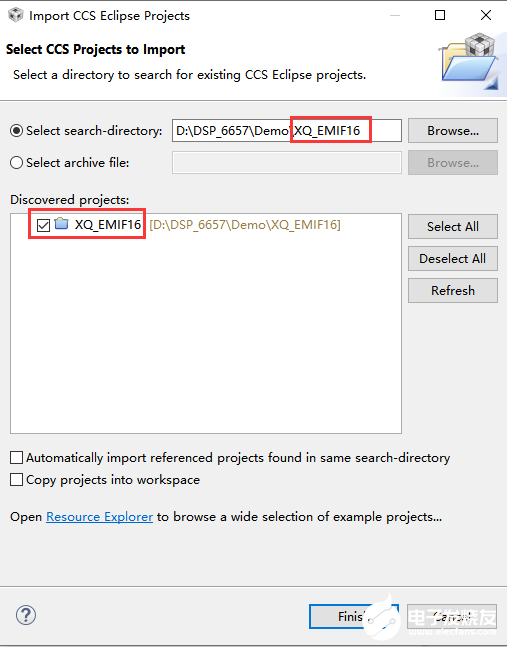

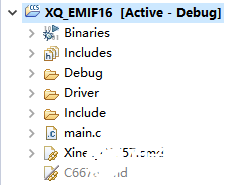

CCS軟件導入EMIF16示例工程XQ_EMIF16,如下圖所示:

1.1.3.2.2 下載運行CCS程序

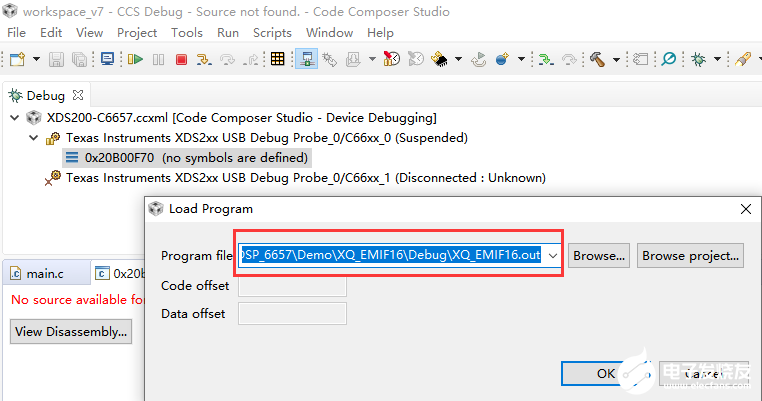

下載DSP可執行文件XQ_EMIF16.out:

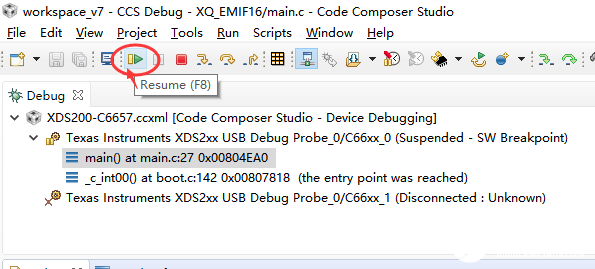

點擊Resume運行DSP程序:

1.1.3.3 運行結果說明

1.1.3.3.1 DSP程序運行結果

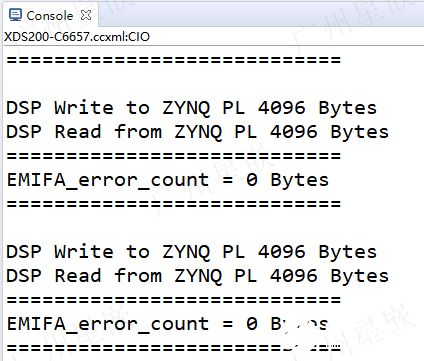

DSP首先通過EMIF16接口往ZYNQ PL端發送4096字節數據,然后再讀回來,并檢測數據是否有錯,數據發送、讀回以及錯誤情況實時打印,如下圖所示:

1.1.3.3.2 ZYNQ PL程序運行結果

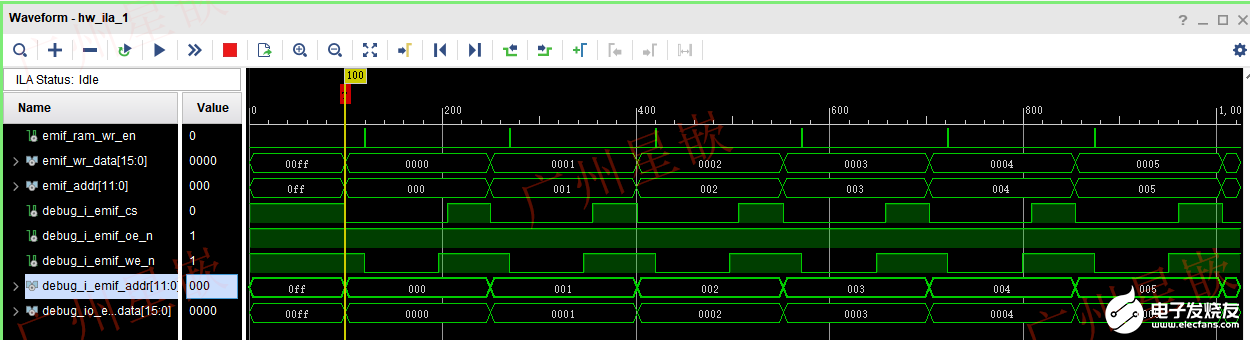

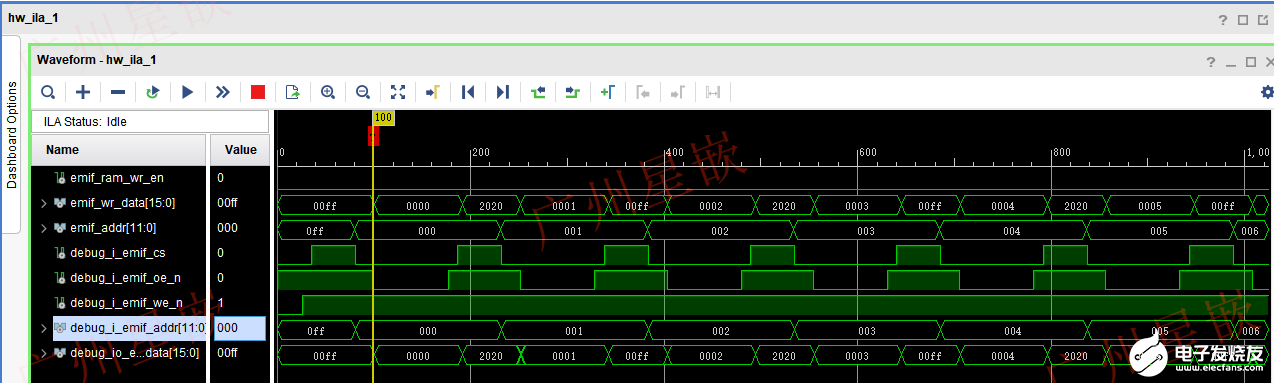

ZYNQ PL端提供的ILA調試窗口,可以實時抓取采集EMIF16總線信號時序波形。

DSP通過EMIF16總線接口發送數據(即寫ZYNQ PL端RAM)示例如下圖所示:

DSP通過EMIF16總線接口讀回數據(即讀ZYNQ PL端RAM)示例如下圖所示:

1.1.3.4 退出實驗

CCS軟件窗口上,點擊Terminate斷開DSP仿真器與板卡的連接。

Vivado調試界面Hardware Manager窗口,右鍵單擊localhost(1),在彈出的菜單中點擊Close Server,斷開ZYNQ JTAG仿真器與板卡的連接。

最后,關閉板卡電源,實驗結束。

文章來源:星嵌電子

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19178瀏覽量

229201 -

dsp

+關注

關注

552文章

7962瀏覽量

348310 -

仿真器

+關注

關注

14文章

1016瀏覽量

83647 -

Zynq

+關注

關注

10文章

608瀏覽量

47129

發布評論請先 登錄

相關推薦

請問6678的EMIF16支持32MB norFLASH不?

C6678 EMIF16 地址空間只有32M bytes 這個疑惑怎么理解?

C6678 EMIF16 NOR FLASH BOOT

c6678 emif16

通過EMIF16將外接FPGA輸出的信號傳給DSP,請問下能不能提供個EMIF的例程?

基于C66x平臺DSP與FPGA通信測試

請問C6655的EMIF16與DDR EMIF有什么區別?

6678 EMIF16 Nor Flash多核boot

DSP+ZYNQ多核例程使用手冊-XQTyer【開源】

ZYNQ與DSP之間SRIO通信的設計實現

ZYNQ與DSP之間EMIF16通信

ZYNQ與DSP之間EMIF16通信介紹說明

ZYNQ(FPGA)與DSP之間GPIO通信實現

XQ6657Z35-EVM 的DSP + ZYNQ核心板,SRIO通訊

ZYNQ與DSP之間EMIF16通信

ZYNQ與DSP之間EMIF16通信

評論