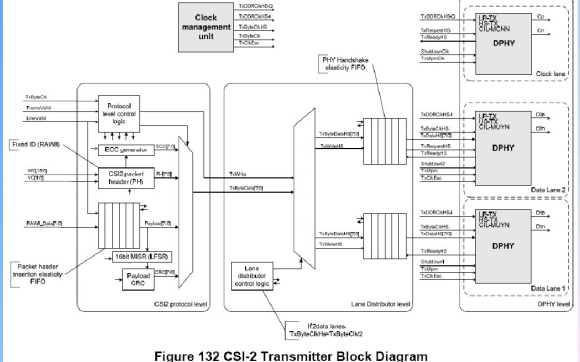

MIPI CSI-2 RX Subsystem IP實現(xiàn)MIPI CSI-2 v2.0協(xié)議以及底層的MIPI D-PHY v2.0協(xié)議, 這個IP是用來抓取來自MIPI CSI-2攝像頭的視頻流, 把該視頻流輸出到AXI4-stream的接口, 進行下一步處理.

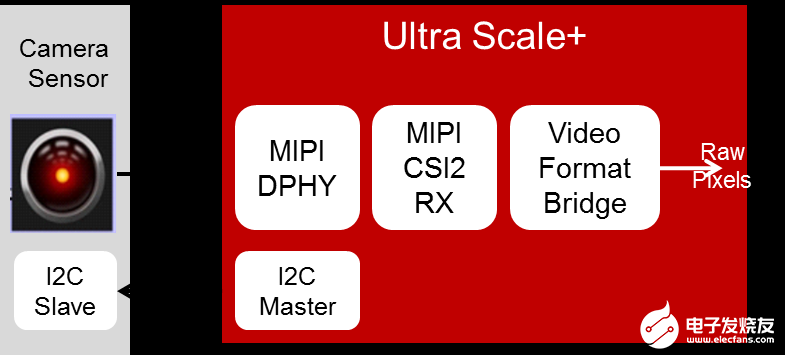

下面是MIPI CSI-2 RX Subsystem IP典型的應用示例:

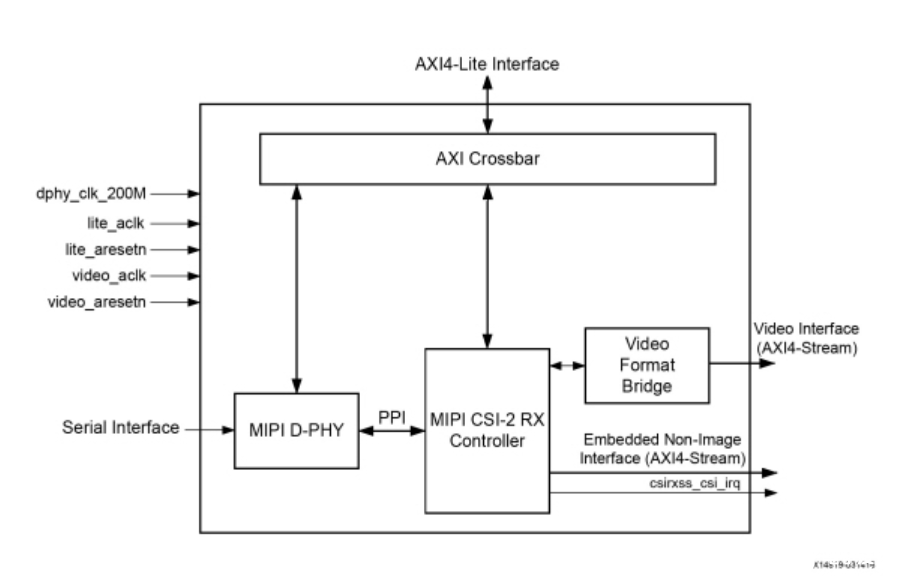

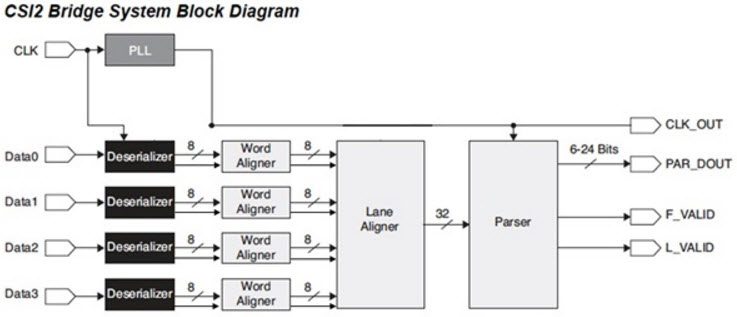

該IP是由MIPI D-PHY和MIPI CSI-2 controller, 以及VFB(Video format bridge)組成, 其中VFB可選. 下面是該IP的簡略系統(tǒng)框圖:

該IP支持7-series, UltraScale+, Zynq-7000, MPSoC, RFSoC, Versal. 對于UltraScale+, MPSoC, RFSoC, 在HP IO bank, 有可以支持MIPI_DPHY_DCI的I/O, 該I/O standard可以在同一個I/O上在low-power mode(0-1.2V single ended)和high speed mode(0.1-0.3v)之前切換。

對于Versal, 在其XPIO bank, 也有支持MIPI_DPHY_DCI I/O standard的I/O, 因此符合MIPI協(xié)議的sensor可以直接與FPGA的這些IO連接。

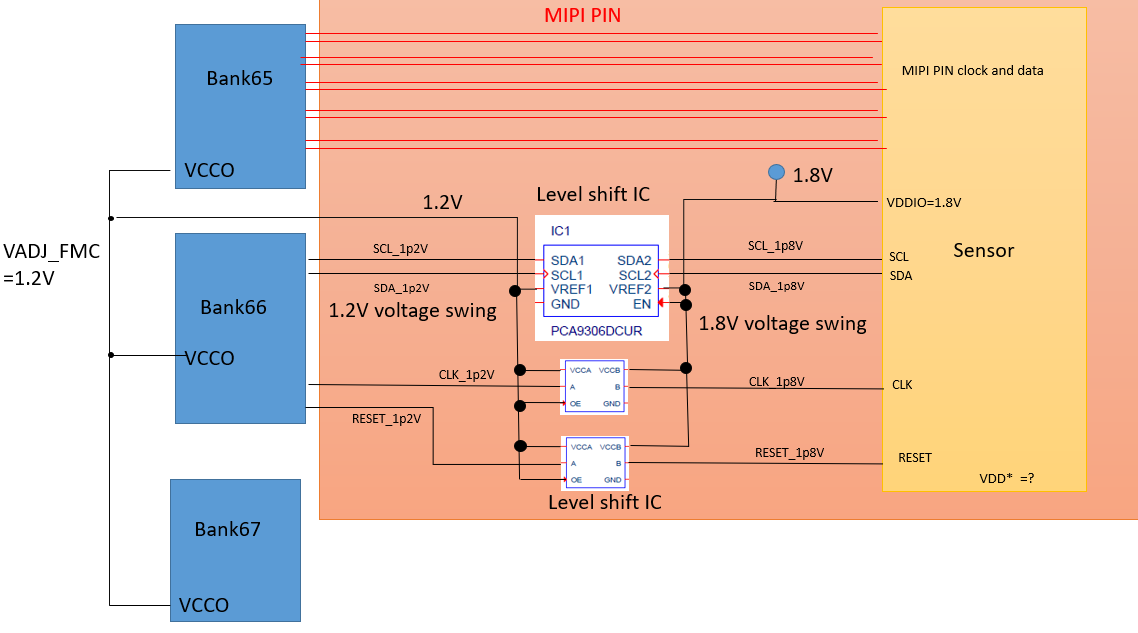

需要注意的是, 因為, MIPI_DPHY_DCI 無論對于input還是output, Vcco的要求都是1.2v, 見FPGA的手冊, 如果sensor需要的電壓是1.8v, 那么這時候, 對于那些控制信號, 因為有電壓差異, 所以需要level shift。

下面是一個例子, sensor需要的VDDIO是1.8v(見sensor的手冊), FPGA與sensor連接的簡略框圖, 左邊是FPGA I/O bank, 右邊是Sensor.x

對于7 series和zynq-7000的支持, 因為FPGA沒有支持MIPI協(xié)議的I/O, 因此, 需要用到XAPP894實現(xiàn)PHY, 當然, 如果用戶直接用MIPI CSI-2 RX Subsystem該IP, 因為該IP支持 7 series, 不需要考慮PHY實現(xiàn)。

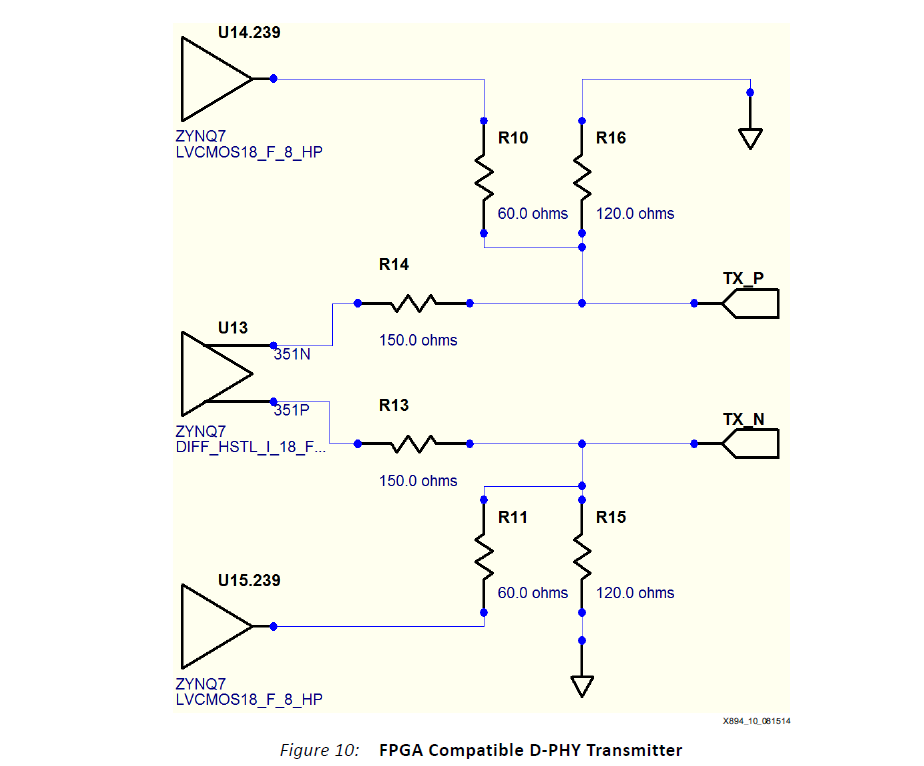

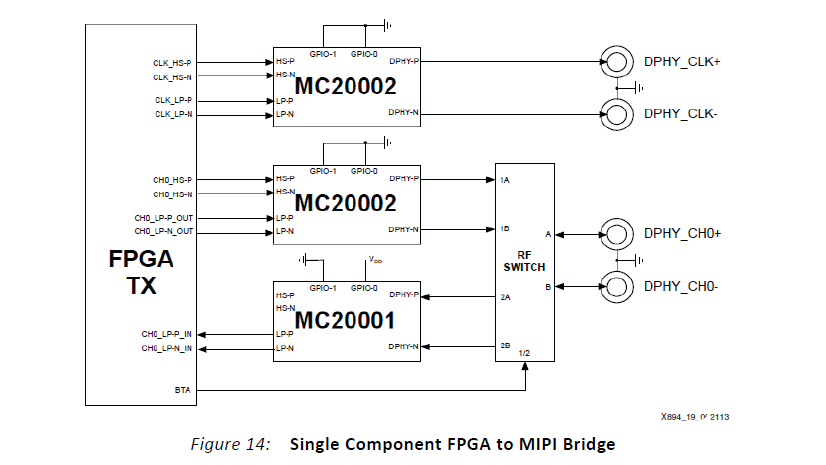

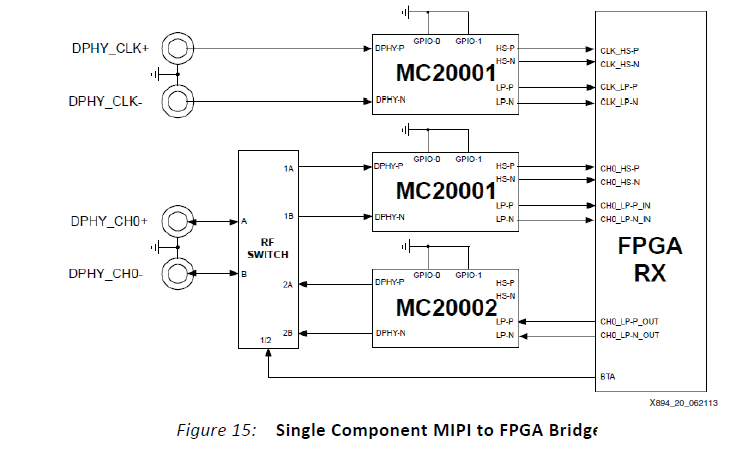

如果目標器件是Spartan, 該IP不支持. 那么用戶需要用到XAPP894實現(xiàn)PHY, XAPP894提供的兩種方式實現(xiàn)DPHY IO, Compatible Solution和Compliant Solution.

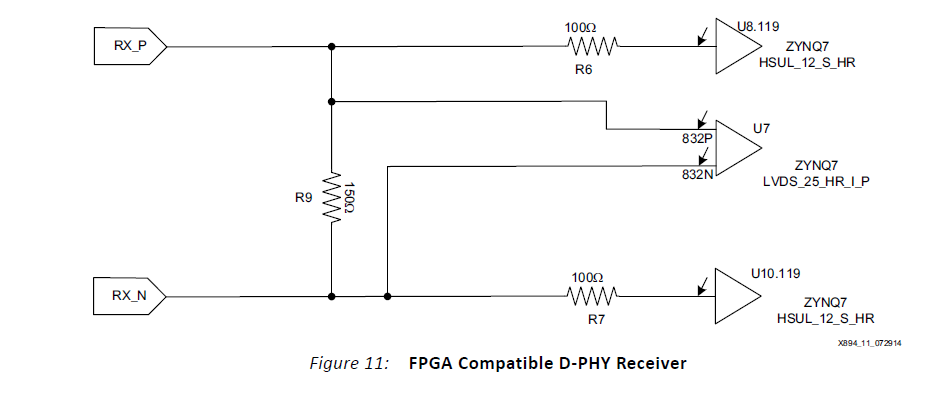

Compatible Solution:

Compliant Solution:

Compatible solution適用于不超過800Mbps的應用, 不管是哪種實現(xiàn)方式, 需要做board level SI simulation。

對于7series以及其他MIPI CSI-2 RX Subsystem支持的這些器件. 需要注意I/O pin以及bank的要求。

審核編輯:湯梓紅

-

攝像頭

+關注

關注

59文章

4808瀏覽量

95420 -

PHY

+關注

關注

2文章

301瀏覽量

51693 -

MIPI

+關注

關注

11文章

308瀏覽量

48555

發(fā)布評論請先 登錄

相關推薦

camera module CSI-2 MIPI解壓這塊沒有

CX3 3065: HOW TO CFG MIPI CSI-2

mipi-csi2-rx示例設計許可證錯誤

請問是否有MIPI CSI-2解決方案可了解FPGA?

移動行業(yè)處理器接口MIPI CSI-2接收橋參考設計

MIPI CSI-2 D-HPY協(xié)議詳細資料介紹免費下載

基于MIPI CSI-2 Receive Bridge圖像傳感器的參考設計

基于MIPI CSI-2 Transmit Bridge圖像傳感器的參考設計

AN-1337:ADI視頻解碼器與MIPI CSI-2接收器連接的設計考慮

HDMI_1.4_2.0_RX_Subsystem_IP介紹和基礎debug建議

MIPI CSI-2 相機規(guī)格增加了先進的始終在線成像解決方案

Gowin MIPI D PHY RX TXAdvance IP用戶指南

如何在ADAS應用程序中使用MIPI?CSI-2端口復制記錄傳感器數(shù)據(jù)

MIPI CSI-2 RX Subsystem IP和D-PHY基本調試

MIPI CSI-2 v2.0:物聯(lián)網(wǎng)、無人機和汽車領域的新興應用

MIPI CSI-2 RX Subsystem IP介紹和PHY實現(xiàn)淺談

MIPI CSI-2 RX Subsystem IP介紹和PHY實現(xiàn)淺談

評論