引 言

并行測試的實現途徑分為軟件方式和硬件方式。用軟件方式實現并行測試,關鍵是對測試任務的分解和調度,但可能會產生競爭或者死鎖現象。因此,在測試資源有限并且任務分解和調度算法不成熟的情況下,用軟件實現并行測試會很困難。用硬件方式實現并行測試時,需要通過提供充足的測試資源來滿足并行測試的需求,而并行測試過程中激勵資源不足同樣會造成任務分解和調度難度增加,甚至導致競爭和死鎖,影響并行測試實現。因此,對多通道并行激勵信號的需求也是影響并行測試的關鍵因素。

1 并行測試技術

并行測試技術是把并行技術引入測試領域中,可以較好地完成同時對多個被測對象(UUT)任務進行測試的一種先進的測試方法和技術,屬于下一代測試技術范疇,是支撐NxTest ATS的新技術之一。它根植于并行處理技術,其宏觀表現為:在并行測試程序的控制下對多個被測對象(UUTs)同時測試。相比傳統順序測試技術,它通過對系統資源的優化利用,可以大幅度提高測試效能及測試質量,提高測試資源利用率,降低整個武器裝備測試成本。因此,研究并行測試技術對我國測試技術的發展和提高武器裝備戰時的快速維護保障能力具有重要意義。

2 多通道波形產生模塊

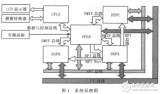

設計采用Altera公司的EP2C35作為整個系統的控制芯片,承擔整個并行多通道信號產生模塊的控制工作,內部主要包括Nios II嵌入式軟核、波形產生控制器、PCI控制器等。

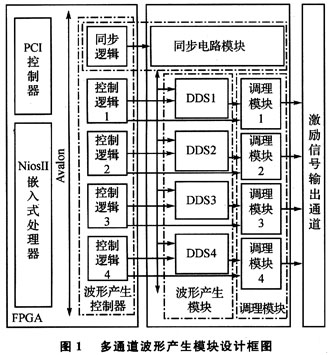

多通道波形產生模塊主要包括4個子模塊,分別為波形產生控制模塊、信號產生模塊、同步電路模塊和調理輸出模塊。波形產生模塊采用DDS技術,該技術產生的波形具備波形頻譜純凈,穩定度高,切換時間短,頻率、相位和幅度可調等特點。設計中采用ADI公司的AD9854芯片來實現此模塊的功能。

波形產生模塊為4個通道,各通道之間相互獨立,且可以在不影響其他通道工作的情況下獨立地發起或者終止輸出。同時為了滿足測試系統對多路同步激勵的需求,模塊還需具備多通道同步的能力,并可以配置同步的通道數量及各通道間相互信號關系。輸出激勵的控制命令信號經PCI總線傳輸到FPGA中,FPGA將接收到的命令經過解析后分別送入同步模塊、DDS信號產生模塊和調理輸出模塊。各通道的DDS信號產生模塊接收到控制命令后與同步模塊配合產生同步或者異步激勵,最后由調理輸出模塊實現輸出波形的濾波和幅度控制。圖1為多通道波形產生模塊硬件設計原理框圖。

3 多通道波形控制器

3.1 結 構

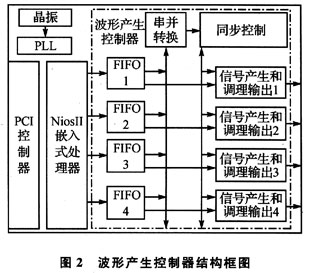

波形產生控制器是整個模塊正常運行的核心,主要完成信號產生控制、信號增益控制以及同步控制。多通道波形產生控制器主要由異步FIFO、同步邏輯與信號產生和調理輸出組成,圖2為波形產生控制器的結構框圖。用戶控制命令經PCI控制器傳輸至Nios II嵌入式軟核后,首先經過譯碼處理,將控制命令按通道進行分類,而后傳輸至波形產生控制器中的異步FIFO進行緩沖。此刻各通道的控制命令主要包括同步命令、信號產生控制字以及增益控制命令,經過串/并轉換后的同步命令控制著通道間的同步時序關系,而信號產生控制字和增益控制字則以并行方式輸出至外圍電路中,完成信號產生和調理輸出。

3.2 實 現

3.2.1 異步FIFO

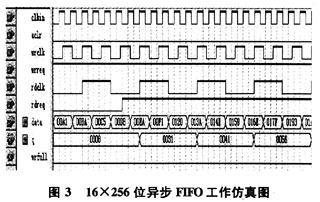

多通道信號產生控制器中具有4個獨立的FIFO,主要用于緩沖PCI控制器與波形產生控制器2個異步時鐘域的數據傳輸,主要包括讀/寫時鐘信號、讀/寫請求信號、數據輸入/輸出信號和空/滿標志位。讀請求信號(rdreq)有效時,在讀時鐘(rdclk)的上升沿處FIFO輸出數據;寫請求信號(wrreq)有效時,在寫時鐘(wrclk)的上升沿處FIFO寫入信號;空/滿標志位決定了數據能夠寫入或讀出,模塊中采用寫滿標志位(wRFull)來表示FIFO內部存儲空間的使用情況。圖3為16×256位的異步FIFO工作仿真圖。

3.2.2 同步邏輯

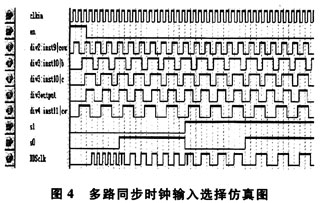

同步邏輯實現多通道波形產生控制模塊的同步控制。信號產生通道的工作狀態有閑置、異步工作和同步工作3種狀態,由用戶提供的同步控制命令決定。當波形產生控制命令加載到輸出寄存器后,在接收到“準備好”命令后同步邏輯控制指定通道同步的輸出控制命令。設計要求各通道具有獨立產生信號的能力,且任意通道間可實現同步操作。首先由同步邏輯產生2分頻、3分頻和4分頻電路分別同步2路、3路和4路的信號輸入,只有1路信號輸出時采用串行時鐘即可。然后根據用戶同步通道控制命令,控制多路選擇通道輸出相應的同步時鐘。采用同步時鐘選擇方法設計的多路同步時鐘仿真圖如圖4所示。

從圖中可見,2位的同步時鐘控制地址s1、s0控制著同步時鐘DDSclk的輸出。當地址位s1和s0分別為00、01、10和11時,同步時鐘DDSclk分別輸出了串行時鐘和串行時鐘2分頻、3分頻與4分頻。其中2分頻和4分頻通過對串行時鐘計數跳轉即可實現,方法簡單且效果良好。對于3分頻的實現則要復雜一點,方法是通過將2個占空比不為50%的3分頻信號相與得到1個占空比為50%的時鐘輸出,如圖中div3:inst10/b與div:inst10/c相與得到的3分頻時鐘輸出div3output。

3.2.3 信號產生和調理輸出

信號產生和調理輸出部分的作用是通過接收控制命令對各通道的DDS電路進行控制。經過FIFO緩沖的16位來自用戶的控制命令FIFO_DATA,由數據控制部分識別、解析、校驗后傳輸到數據串/并轉換模塊,串/并轉換模塊按照數據格式的要求將其轉換為2位通道地址總線部分(c1,c0)、6位DDS寄存器地址總線部分(d5~d0)和8位數據總線部分(d7~d0),組成16位控制字,如下所示:

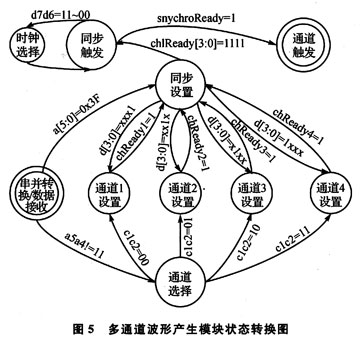

由2位的通道地址選中命令接收通道,6位的DDS寄存器地址總線輸出后控制AD9854的寄存器的0x00~0x27單元,8位的數據總線傳輸波形產生信息和增益控制信息。其中6位的地址總線除了作為DDS寄存器地址外,還用于同步狀態的設置。當地址總線為0x3F時,控制器進入同步設置狀態,此刻的8位數據總線用于傳輸同步設置內容。圖5為并行多通道波形產生模塊的部分狀態轉換圖。

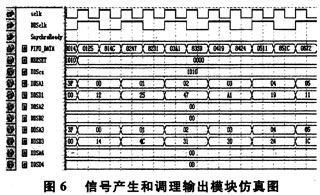

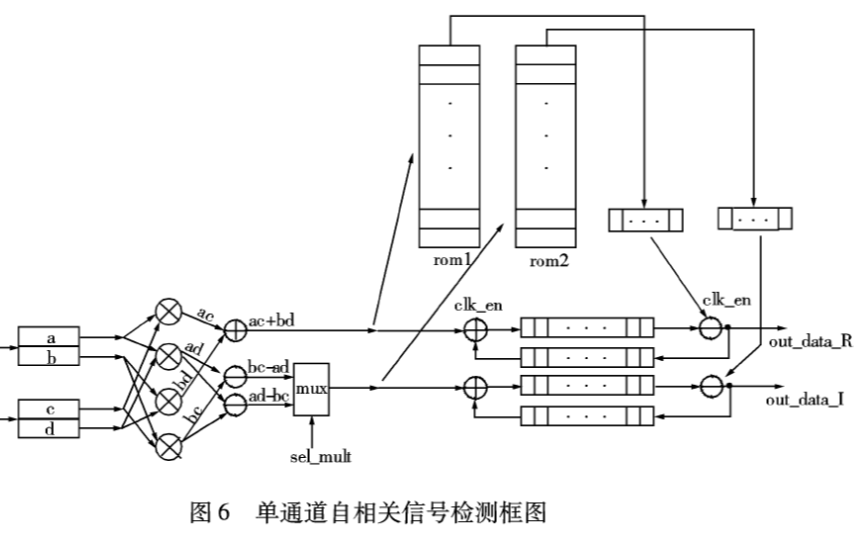

圖6為信號產生和調理輸出模塊的邏輯仿真圖,圖中DDSA1~DDSA4為6位的DDS寄存器地址總線,DDSD1~DDSD4為8位的數據總線,DDSclk為同步時鐘。通過同步設置,選擇了1、3通道輸出波形,并使DDSclk輸出串行時鐘的2分頻。從圖中可看出,此次是對1、3通道進行信號產生的控制,而沒有對2、4通道進行操作。同時將16位的FIFO_DATA控制命令譯碼后輸出,圖中FIFO_DATA的0x0125經譯碼后,選中通道1,并驅動DDSAl輸出0x01,DDSD1輸出0x25。

4 模塊測試

首先對各通道的信號產生電路進行單獨的測試,然后任意選擇2路通道產生獨立的激勵信號,再分別選擇3路和4路通道進行測試。進行以上測試測得模塊各通道間異步工作正常,而后進行通道同步測試。設置多通道波形產生模塊16位控制字中的a[5:0]為0x3F,進入同步設置模塊,設置通道選擇和通道輸出頻率后,對同步通道進行測試,測得同步通道模塊工作正常,滿足設計要求。

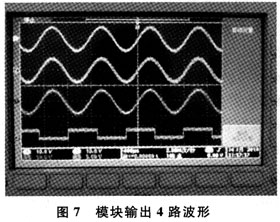

圖7為7個通道同時輸出波形的測試,其中1、2、3通道為同步方式輸出的3路正弦波,4通道為獨立輸出的方波。測試后發現,模塊具備產生高質量的并行多通道激勵信號的能力。

結 語

本文以并行多通道信號產生模型為依據,設計并實現了以FPGA為核心器件的并行多通道信號產生模塊,主要包括FPGA系統設計和多通道波形產生模塊設計。通過模塊測試后發現,該模塊具備產生高質量并行多通道激勵信號的能力。在后續的研究中,以產生各種復雜的激勵信號為主,并通過增加并行算法或采用多嵌入式軟核等方法改善模塊通道之間的并行機制,充分挖掘各通道的并行特性。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602024 -

正弦波

+關注

關注

11文章

639瀏覽量

55290 -

激勵信號

+關注

關注

0文章

4瀏覽量

8226

發布評論請先 登錄

相關推薦

利用FPGA做一個多通道超聲信號采集分析的系統的基本工作原理

哪些因素影響了FPGA的并行多通道激勵信號產生?

FPGA并行多通道信號產生模塊有什么特點?

多通道信號采集記錄 多通道采集存儲 多通道記錄存儲介紹

基于NiosII的多通道PWM信號測量產生器節點設計

基于USB的并行多通道頻率測試儀的設計

基于DSP與FPGA的多視頻通道的切換控制

基于FPGA的并行多通道激勵信號產生模塊

基于DSP+FPGA的并行信號處理模塊設計

FPGA的并行多通道激勵信號產生模塊

FPGA的并行多通道激勵信號產生模塊

評論