文章出處:作者Actel公司 Michael Mertz和Venkatesh Narayanan

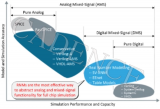

為了因應市場對于較高性能、較小的系統尺寸及降低成本和電源的需求,系統設計者正將較高層級的混合信號功能整合在他們的系統單芯片(SoC)設計中。隨著這些SoC設計上的混合信號組件數量增加了,基本的功能驗證對于硅初期能否成功也愈來愈重要。FPGA在系統整合難題上加入了一個新特點,改善了系統整合面,如整體的系統成本、可靠性、可組態性、上市時間等。在核心上,此新范例-可編程系統單芯片(programmable system chip, PSC)整合FPGA電閘,內嵌快閃和模擬功能在單一的可程序化組件中,提供了具真正程序能力的理想低成本路徑,而且系統設計者可以用來快速地設計和研發復雜的混合信號系統。

關鍵準則

如業界分析師所言,FPGA正成為現代高度整合的SoC系統選擇的工具。原因很明顯。由于硅架構是預先組裝的,因此沒有NRE成本,且任何可能影響產品性能或裝置可靠度的制程變化都應已解決。芯片整體作業中大部分的復雜度(包括寄生RLC對時序的影響等)特性都已完整調整,且規格上的數據已考慮到這些。因此所有的驗證循環都可以致力于設計的適當功能性上。下一個需要的是可以盡量減少特征化和強化設計功能性目標時間的驗證方法。此項減少是透過組合智能型模型(抽出不會影響整體系統行為的較不重要細節)將所產生的模型置入已完全了解的流程中。

復雜度增加

現場可程序化是系統整合全新的一面。此新的整合層級較深入且有以下幾個優點:系統設計者可移除系統的許多組件而將該功能整合在單一PSB中,大幅簡化系統設計;組件大幅減少就會有明顯小許多的尺寸;且微控制器核心的整合會免除主處理器的周邊任務,降低系統處理的工作量要求。

新一代的PSC是第一個如此進入可程序化邏輯市場的代表。它是第一個以FPGA提供的硬件可重組態性的基本好處結合閃存、混合信號功能性以及微控制器技術。日益復雜的內容開啟了更小的整合裝置之許多可能,但FPGA設計者也立即有了額外的挑戰,其中一項就是對付混合信號設計的復雜性。很少FPGA設計者有機會在這些領域中取得深刻的經驗,因此什么是管理這些計劃的復雜度并確保它們第一次就成功的方法呢?

此一跨范圍的專業技術必須包裹在工具流程中。工具必須做得夠聰明來管理重要細節(如接口、組態和初始化需求)以便連結不同的組件并放在同一作業中。理想上此新系統功能性的復雜設計內容匯集基本上和傳統工具流程完全一樣的工具流程。

智能型流程

不僅是ASIC/FPGA設計者對系統/模擬設計的實際經驗很少,大部分的系統設計者也同樣沒有數字邏輯的設計經驗。因此,日益純熟的設計內容需要智能型的工具流程。這意味著工具有智能去組態和啟動不同的系統組件,正確地將它們結合,并將令人卻步的所有跨范圍復雜度驗證任務弄簡單給工程師。在這種情況下,他們就必須產生一個FPGA。從前端(和實作步驟相反)開始,此復雜性就在3個重要區域中被管理:組件模型、設計實例(instantiation)以及驗證流程。

組件模型

當制作以硅為目標的組件模型時,對于細節組件行為對照驗證系統正確作業所需的時間的取舍需謹慎為之。這在PLD架構的模擬組件中尤其重要,依此零件的預先組裝天性即使是已解決的問題還是會被呈現。在最高層級的抽取中,所有的模擬組件都是依據數字組件將嚴格的數字行為規范覆蓋在模擬行為模式上。竅門是抽出組件的完整行為細節,只留下能決定符合特定設計目標系統所需的功能。在PSC流程方面,依據實際硅的特征化數據的規格上具有模擬功能的電子特征,如信號整合度、A/D傳輸功能以及耦合效應等。包括輸入預先縮放、差動增益、遲滯、A/D控制功能及輸出行動等基本的模擬交換行為會被抽出,并放入適合在數字仿真器中特征化系統層級行為的粗略數字行為模式中。

設計實例

此一復雜且純熟系統的設計實例需要有足夠智能讓設計者快速行動的靈活設計產生環境。基本上此,可達目標裝置的邏輯資源所允許的最大值。這些受到自身繪圖組態器支持的非常靈活資源是可以擷取、組態、并例舉在設計中的,全都是非常簡單的pick-and-click動作,不需要直接HDL編碼。同時工具鏈會創造骨架,將想要的資源互連,并自動創造必要的控制機制。

智能的以GUI為基礎的工具是在不需要直接使用者引導的背景下達成這些步驟的。這些工具的焦點都在容易使用,并提供快速的設計發展。當然它并不排除傳統的HDL代碼發展,后者是熟悉HDL的使用者所不可或缺的,他們在計算電閘時需要最大的最佳化設計,或是需要廣泛的設計客制化。

驗證

傳統的混合信號ASIC發展遵循由下而上的方法。它牽涉到兩個不同的小組:一個研發數字部分的寫入RTL代碼,而另一個在晶體管層級實作模擬電路。在驗證方面,設計者一般使用Verilog-AMS或VHDL-AMS的高層級全芯片仿真以驗證系統層級的行為,如功能、性能和遲滯等。這需要和最終電路關系密切的模擬行為模式。然而驗證接口層級議題、時序、信號整合度和電源等晶體管層級的模擬還是需要晶體管層級的模擬。這也可以幫助避免模型和電路之間的不準確性或不當關聯。最近幾年出現了新等級的工具,允許混合信號共同仿真環境在指定的SoC中驗證混合信號組件。

在PSC流程中,混合信號仿真是沒有必要的。對待組件內的模擬功能像開架式分離組件一般。就像組件廠商一樣,數據規格所提供的模擬功能電子特征的許多信息依據實際硅的特征化數據。抽出詳細的模擬行為后所產生的模式在全數字仿真器(如ModelSim等)中,就完全可以達到系統層級的驗證。模擬輸入是以真實或位向量值呈現在仿真測試基準中,一般是以測試基準工具產生的。

有了此層級的抽出,針對混合信號FPGA所提供的基本驗證方法和沿著標準處理的數字FPGA基本上是相同的。

典型的PSC設計者會在設計過程中執行以下步驟:在Libero中產生并整合系統功能區塊;透過Synplify或Synplify PRO合成設計;利用ModelSim驗證設計;利用Libero Designer將設計編輯在Fusion PSC中以利后端實作;在ModelSim中利用后批注(back-annotated)時序再次驗證。

此基本流程讓Fusion使用者可以利用經證實的方法,在設計過程中的任何階段驗證混合信號PSC的系統層級行為,就宛如全數字芯片般簡單。此流程依據客戶設計中整合其余數字系統的某個模擬輸入組合執行仿真系統層級行為必要的工作。

SoC發展概念上需要各式各樣的專業技術,包括模擬設計、數字邏輯設計以及系統/結構定義等。隨著整合層級的上升,此課題迅速地變得異常復雜,且FPGA發展常常牽涉到通常沒有這類專業的一小組邏輯/FPGA設計工程者。■

審核編輯 黃宇

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601840 -

混合信號

+關注

關注

0文章

469瀏覽量

64932 -

soc

+關注

關注

38文章

4122瀏覽量

217937

發布評論請先 登錄

相關推薦

ZGF智能型直流高壓發生器使用技巧說明

HDZG智能型直流高壓發生器的操作方法

安科瑞WHD智能型溫濕度控制器RS485通訊 WHD20R-11

智能型CVT電容互感器現場校驗儀如何使用——每日了解電力知識

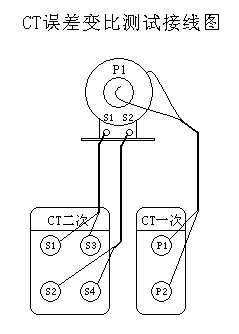

智能型電流互感器校驗儀的使用方法——每日了解電力知識

FPGA的學習筆記---FPGA的開發流程

智能型數據配線架一般用在什么地方

笙泉、呈功攜手推出FOC智能型調機系統,實現高效開發馬達控制產品

什么是FPGA原型驗證?FPGA原型設計的好處是什么?

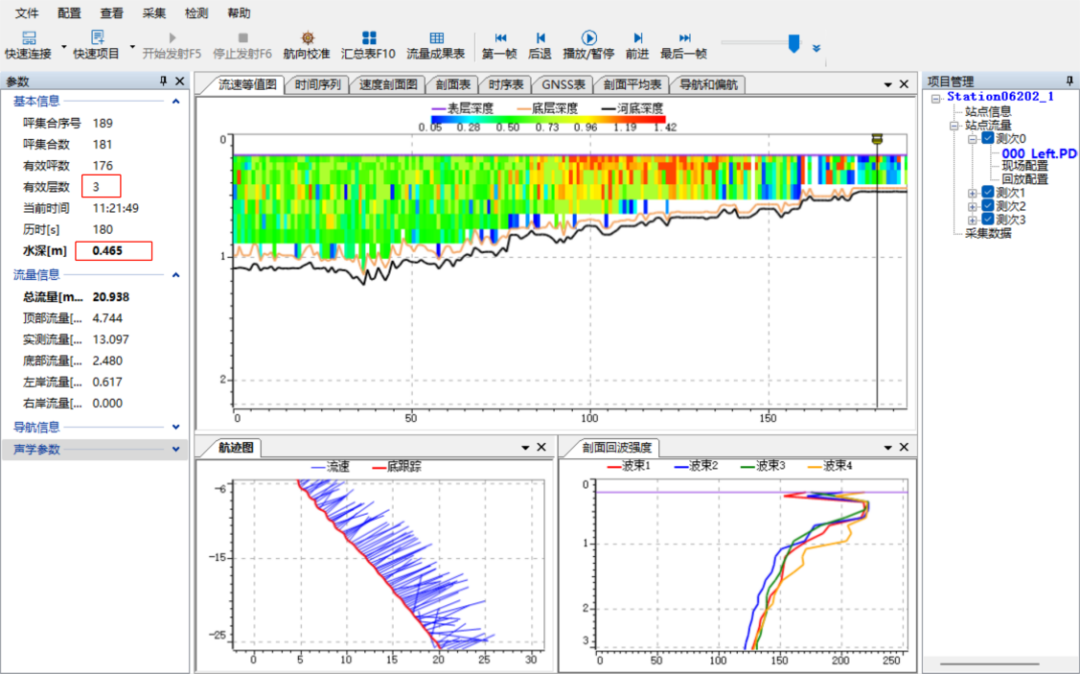

中海達iFlow RP1200智能型ADCP實現各水域環境全覆蓋

混合信號FPGA的智能型驗證流程

混合信號FPGA的智能型驗證流程

評論