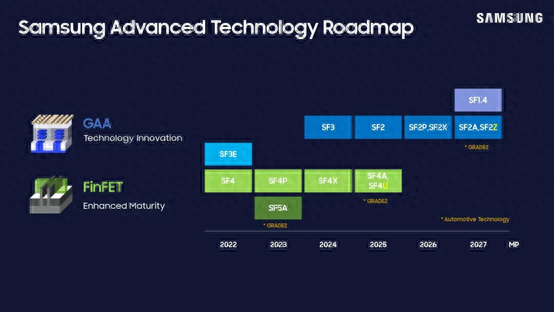

三星電子公布了其在小于 3 納米(1 米的十億分之一)半導(dǎo)體領(lǐng)域獲得競(jìng)爭(zhēng)優(yōu)勢(shì)的技術(shù)路線圖。該公司計(jì)劃成為世界上第一個(gè)實(shí)施3D封裝技術(shù)的公司,垂直堆疊其代工廠生產(chǎn)的Gate-All-Around(GAA)芯片。此舉表明該公司決心提供最先進(jìn)的整體解決方案,從制造生產(chǎn)線到先進(jìn)的后段處理。

7月4日,在首爾三星洞COEX展廳舉辦的三星晶圓代工論壇2023上,三星電子代工業(yè)務(wù)總裁崔時(shí)永作為第一位主講人介紹了這一代工路線圖戰(zhàn)略。

Choi總裁表示:“我們計(jì)劃到2025年將GAA工藝制造的芯片的應(yīng)用擴(kuò)展到3D封裝,”并補(bǔ)充道,“由于精細(xì)加工在降低成本和縮小芯片面積方面存在限制,因此我們正在多樣化我們的先進(jìn)后處理技術(shù)。” 業(yè)界從未嘗試過(guò)將 GAA 工藝與 3D 封裝相結(jié)合,這主要是因?yàn)檫@兩種工藝的復(fù)雜性都很高。

GAA 是一種在制造線上制造超精細(xì)器件的預(yù)處理技術(shù)。它最大化了數(shù)據(jù)傳輸路徑的面積,同時(shí)減小了半導(dǎo)體的尺寸。3D 封裝是一種組合技術(shù),可以使不同的芯片像單個(gè)半導(dǎo)體一樣發(fā)揮作用。由于精細(xì)電路的實(shí)現(xiàn)已達(dá)到極限,英特爾和臺(tái)積電等半導(dǎo)體公司正在激烈競(jìng)爭(zhēng)以增強(qiáng)這項(xiàng)技術(shù)。

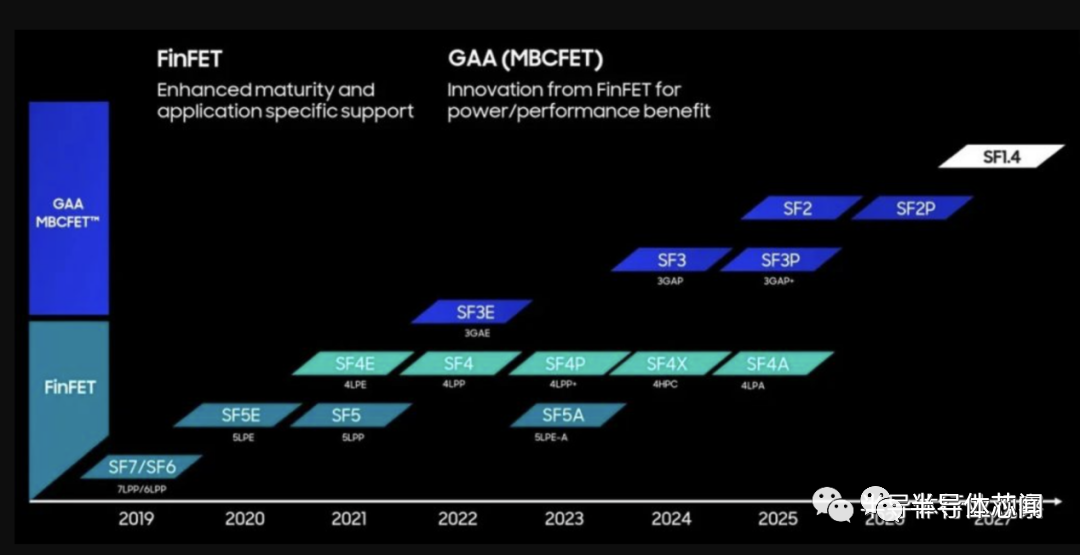

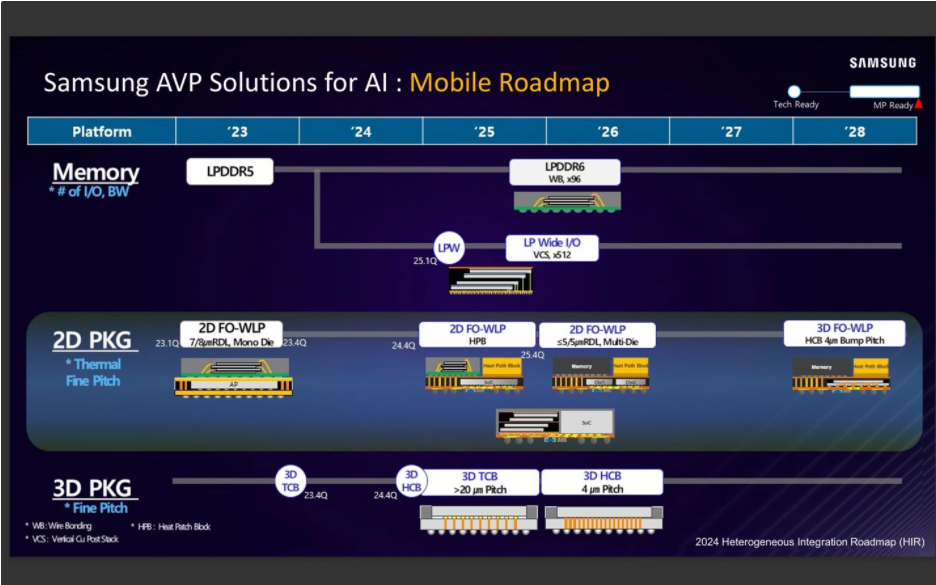

三星電子于2020年首次推出7納米EUV系統(tǒng)半導(dǎo)體的3D堆疊封裝技術(shù)X-Cube,早于業(yè)界第一的臺(tái)積電。2022年,三星還全球率先將3納米GAA工藝引入量產(chǎn)線。該公司在半導(dǎo)體業(yè)務(wù)部門內(nèi)組建了先進(jìn)封裝(AVP)業(yè)務(wù)團(tuán)隊(duì),加速下一代半導(dǎo)體后處理的研發(fā)(R&D)。到2027年,三星計(jì)劃如期量產(chǎn)1.4納米工藝。

今年第一季度,全球晶圓代工市場(chǎng)份額較上一季度略有擴(kuò)大,臺(tái)積電為60.1%,三星電子為12.4%。不過(guò),與臺(tái)積電將FinFET結(jié)構(gòu)應(yīng)用到3納米不同,三星電子從3納米開始就開始應(yīng)用GAA,并有信心在基于GAA的競(jìng)爭(zhēng)中在技術(shù)上領(lǐng)先。

三星電子還公布了加強(qiáng)國(guó)內(nèi)和國(guó)際無(wú)晶圓廠生態(tài)系統(tǒng)的計(jì)劃。三星將與國(guó)內(nèi)無(wú)晶圓廠產(chǎn)業(yè)合作,培育包括AI半導(dǎo)體在內(nèi)的國(guó)內(nèi)半導(dǎo)體生態(tài)系統(tǒng)。三星認(rèn)為,要發(fā)展代工業(yè)務(wù),需要一個(gè)以無(wú)晶圓廠公司為中心的強(qiáng)大半導(dǎo)體生態(tài)系統(tǒng)。

三星電子將首先發(fā)布新的PDK Prime,它提供半導(dǎo)體開發(fā)所需的信息。PDK是指代工公司向無(wú)晶圓廠公司提供的制造工藝信息。使用PDK,無(wú)晶圓廠公司可以設(shè)計(jì)與三星代工制造工藝和設(shè)備相匹配的半導(dǎo)體。

與以前的版本相比,新的 PDK Prime 包含許多可縮短產(chǎn)品設(shè)計(jì)時(shí)間并提高設(shè)計(jì)準(zhǔn)確性的功能。三星計(jì)劃從今年下半年開始向 2 納米和 3 納米工藝無(wú)晶圓廠客戶提供 PDK Prime,并打算此后將該服務(wù)擴(kuò)展到 8 英寸和 12 英寸傳統(tǒng)工藝。

事實(shí)上,韓國(guó)無(wú)晶圓廠和系統(tǒng)半導(dǎo)體的基礎(chǔ)很脆弱。據(jù)韓國(guó)半導(dǎo)體產(chǎn)業(yè)協(xié)會(huì)統(tǒng)計(jì),韓國(guó)系統(tǒng)半導(dǎo)體的全球市場(chǎng)份額僅為3%。無(wú)晶圓廠份額略高于 1%。全球排名前10的無(wú)晶圓廠公司中,有6家是美國(guó)公司,4家來(lái)自全球領(lǐng)先代工公司臺(tái)積電的所在地臺(tái)灣地區(qū)。臺(tái)灣大大小小的無(wú)晶圓廠公司都在與臺(tái)積電一起創(chuàng)建系統(tǒng)半導(dǎo)體生態(tài)系統(tǒng)。

相比之下,據(jù)估計(jì),三星代工廠90%以上的客戶來(lái)自其自己的系統(tǒng)LSI業(yè)務(wù)、這表明三星代工在韓國(guó)的潛在客戶很少能與三星電子一起成長(zhǎng)。

多家無(wú)晶圓廠公司出席了此次活動(dòng),展示了與三星電子的合作案例。韓國(guó)最大的無(wú)晶圓廠公司LX Semicon計(jì)劃加強(qiáng)與三星電子的代工合作,從8英寸工藝開始,擴(kuò)展到12英寸工藝。AI 無(wú)晶圓廠公司 Rebellions 今年將其 AI 半導(dǎo)體 Atom 商業(yè)化,該芯片采用三星代工廠的 5 納米工藝。DEEPX 還使用三星代工的 5、14 和 28 納米工藝開發(fā)了四種高性能、低功耗的人工智能半導(dǎo)體。

三星電子還宣布了加強(qiáng)本土系統(tǒng)半導(dǎo)體研發(fā)生態(tài)系統(tǒng)的計(jì)劃。該公司將于明年擴(kuò)展其多項(xiàng)目晶圓 (MPW) 服務(wù),該服務(wù)是人工智能和高性能計(jì)算的關(guān)鍵推動(dòng)者,采用先進(jìn)的 4 納米工藝。MPW 是一項(xiàng)服務(wù),使沒(méi)有自己的半導(dǎo)體晶圓或晶圓廠的無(wú)晶圓廠公司能夠設(shè)計(jì)半導(dǎo)體原型。三星計(jì)劃今年三度提供4納米MPW支持,并計(jì)劃明年將MPW服務(wù)總數(shù)增加10%以上。

三星2nm計(jì)劃的更多細(xì)節(jié)

這不是三星首次披露其2nm的計(jì)劃,其實(shí)針對(duì)這個(gè)被廣泛看好的“大節(jié)點(diǎn)”,這家韓國(guó)巨頭密謀已久,他們?cè)谶@次代工論壇上也帶來(lái)了更多的消息。

據(jù)semiwiki報(bào)道,與英特爾一樣,三星自己的芯片也是自己的代工客戶,因此他們?cè)?nm上首先生產(chǎn)的是內(nèi)部產(chǎn)品,而不是外部代工客戶。這當(dāng)然是 IDM 代工廠的優(yōu)勢(shì),可以結(jié)合工藝技術(shù)開發(fā)自己的芯片。三星擁有開發(fā)領(lǐng)先內(nèi)存的額外優(yōu)勢(shì)。

報(bào)道指出,三星將于 2025 年開始量產(chǎn)用于移動(dòng)應(yīng)用的 2nm 工藝,然后于 2026 年擴(kuò)展到具有背面供電的 HPC,并于 2027 年擴(kuò)展到汽車領(lǐng)域。與 3nm 工藝 (SF3) 相比,三星的 2nm (SF2) 工藝已顯示出性能提升 12%,功率效率提高提升 25%,面積減少 5%。

按照三星的規(guī)劃,其GAA MBCFET無(wú)疑是2nm工藝的最大競(jìng)爭(zhēng)優(yōu)勢(shì)所在,在上個(gè)月的時(shí)候,他們就公布了公司在3nm GAA MBCFET技術(shù)的最新進(jìn)展,這將給他們的2nm提供參考。

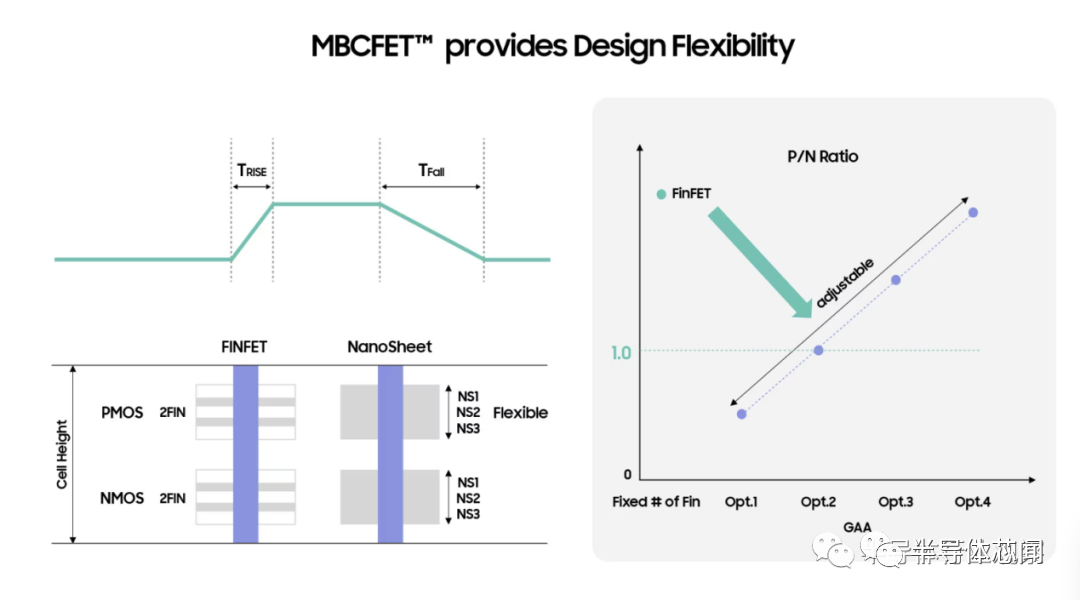

三星表示,與 FinFET 相比,MBCFET 提供了卓越的設(shè)計(jì)靈活性。晶體管被設(shè)計(jì)成有不同量的電流流過(guò)它們。在使用許多晶體管的半導(dǎo)體中,必須調(diào)節(jié)電流量,以便在所需的時(shí)序和控制邏輯下打開和關(guān)閉晶體管,這需要增加或減少溝道的寬度。

而在傳統(tǒng)的FinFET結(jié)構(gòu)中,柵極所包裹的鰭片(Fin)的高度是不可調(diào)節(jié)的,因此為了增加整體溝道寬度,需要水平地增加鰭片的數(shù)量。但這種方法只能調(diào)節(jié)不連續(xù)的溝道寬度,因?yàn)楫?dāng)柵包圍文件的溝道寬度為α?xí)r,也只能減小或增大α的倍數(shù)。這是一個(gè)嚴(yán)重的限制。

另一方面,MBCFET 彼此堆疊在一起,鰭片側(cè)向放置,納米片的寬度可以調(diào)整,以提供比 FinFET 更多的溝道寬度選項(xiàng),這是一個(gè)對(duì)整個(gè)設(shè)計(jì)有用的功能,這在模擬 SRAM 中具有顯著的優(yōu)勢(shì)設(shè)計(jì)。

”MBCFET 具有這些優(yōu)勢(shì),因?yàn)樗鼈兊脑O(shè)計(jì)允許獨(dú)立微調(diào)晶體管的溝道寬度,以便在 P 型金屬氧化物半導(dǎo)體晶體管 (PMOS) 和 N 型金屬氧化物半導(dǎo)體晶體管(NMOS)之間找到最佳平衡”,三星強(qiáng)調(diào)。

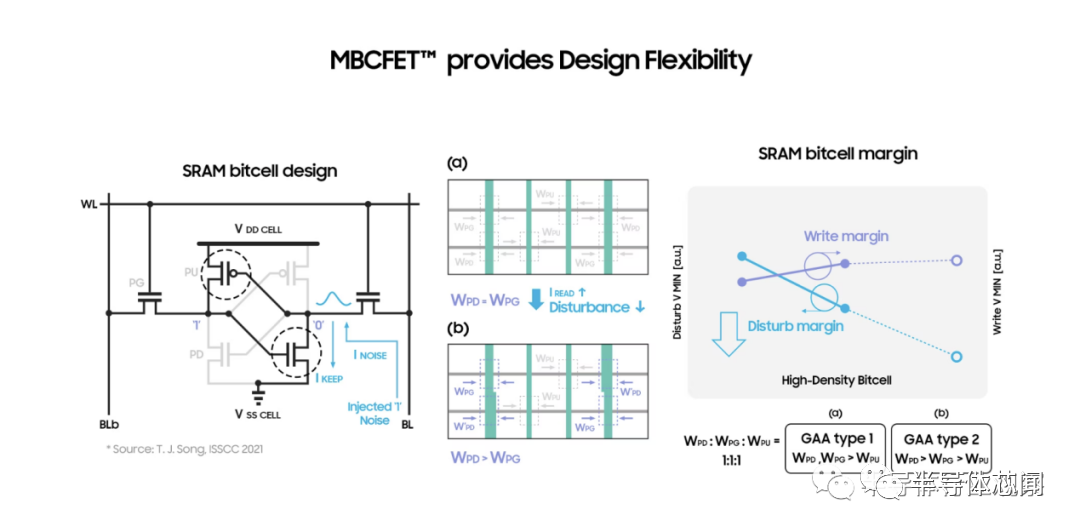

而在MBCFET 通過(guò)調(diào)整納米片寬度,為 SRAM 單元設(shè)計(jì)提供了更大的靈活性。左上圖顯示了具有六個(gè)晶體管的基本 SRAM 位單元。中間圖像顯示了該位單元的圖形設(shè)計(jì)系統(tǒng) (GDS) 視圖。

在圖(a)中,在GAA結(jié)構(gòu)中,NMOS下拉(PD)和傳輸門(PG)具有相同的溝道寬度,而PMOS上拉(PU)具有較小的溝道寬度。(WPD = WPG > WPU ) 在這種情況下,從右圖可以看出,MBCFET 可以比 FinFET 獲得更好的裕度。

在圖(b)中,當(dāng)PD和PG之間的溝道寬度變化時(shí),它們是NMOS(W PD > WPG > WPU ),裕度高于(a)。通過(guò)根據(jù)晶體管的作用和特性調(diào)整溝道寬度,實(shí)現(xiàn)最佳平衡,并確保裕度。由于 GAA SRAM 位單元比 FinFET 需要更少的功率,并且由于每個(gè)晶體管的 GAA 寬度可以獨(dú)立調(diào)整,因此 PPA 和 SRAM 之間的平衡得到改善,從而大大提高了 SRAM 的設(shè)計(jì)穩(wěn)定性。

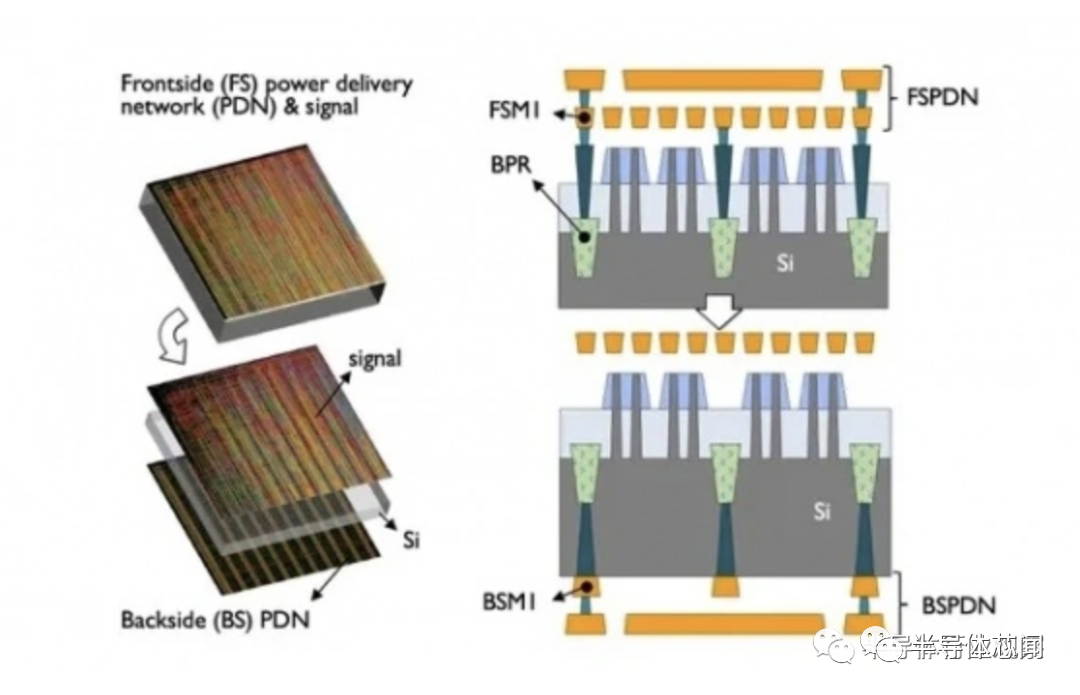

除了晶體管外,背面供電技術(shù)也是三星2nm的一個(gè)殺手锏。

三星研究員Park Byung-jae表示,在代工市場(chǎng),技術(shù)正在從高 k 金屬柵極平面 FET 發(fā)展到 FinFET、MBCFET,以及現(xiàn)在的 BSPDN。

據(jù)介紹,BSPDN與前端供電網(wǎng)絡(luò)不同,它主要使用后端;正面將具有邏輯功能,而背面將用于供電或信號(hào)路由。據(jù)他們?cè)谝黄撐闹信叮瑢⒐╇娋W(wǎng)絡(luò)等功能移至芯片背面,以解決使用2nm工藝造成的布線擁塞問(wèn)題。據(jù)稱,與 FSPDN 相比,BSPDN 的性能提高了 44%,能效提高了 30%。

在公布2nm規(guī)劃的同時(shí),三星強(qiáng)調(diào),公司的1.4nm工藝預(yù)計(jì)于 2027 年實(shí)現(xiàn)量產(chǎn)。與此同時(shí),三星代工廠繼續(xù)致力于投資和建設(shè)產(chǎn)能,在韓國(guó)平澤和德克薩斯州泰勒增設(shè)新生產(chǎn)線。目前的擴(kuò)張計(jì)劃將使公司的潔凈室產(chǎn)能到 2027 年比 2021 年增加 7.3 倍。

3D,重塑晶圓世界

世界不是平的,晶圓代工行業(yè)也是如此。對(duì)性能的需求不斷變化,競(jìng)爭(zhēng)格局也在持續(xù)改變,這是一個(gè)因創(chuàng)新而繁榮的多維市場(chǎng)。盡管晶圓代工行業(yè)經(jīng)歷了天翻地覆的變化,芯片設(shè)計(jì)基本上仍然拘泥于傳統(tǒng)的平面架構(gòu)。

不過(guò),平面架構(gòu)是否真能釋放理想的性能?

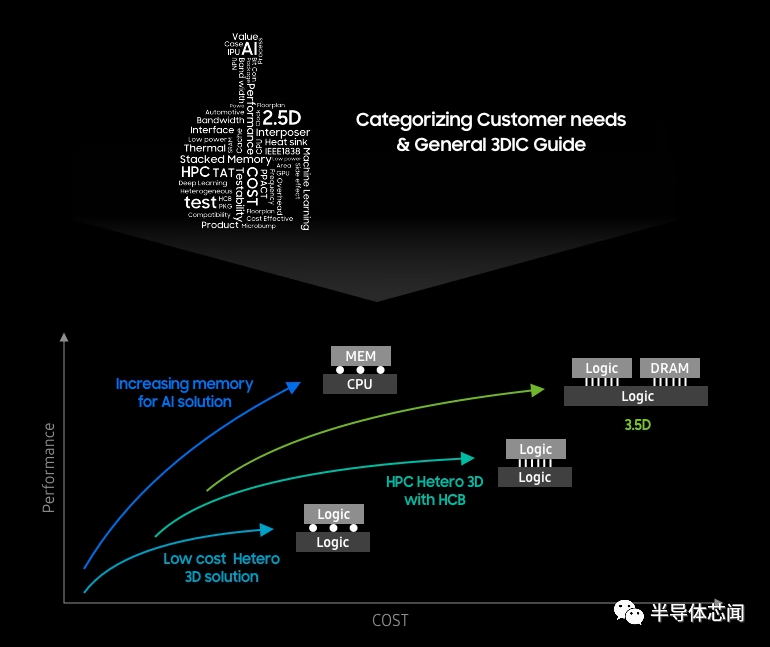

Samsung Foundry 卻并不認(rèn)為這就是終點(diǎn),因此打造出了 3D IC,這種立方體式的解決方案提供更高水平的性能,超越了傳統(tǒng)的性能尺度。3D IC 這種多層基礎(chǔ)架構(gòu)是我們從二維芯片轉(zhuǎn)向三維立體芯片轉(zhuǎn)型的關(guān)鍵,它實(shí)現(xiàn)了存儲(chǔ)和性能的結(jié)合,讓“延續(xù)摩爾定律”的未來(lái)成為現(xiàn)實(shí)。

改變形態(tài),改變未來(lái)

在圣何塞舉行的 2022 年三星SAFE論壇上,當(dāng)Samsung Foundry設(shè)計(jì)技術(shù)團(tuán)隊(duì)負(fù)責(zé)人Sangyun Kim邁上講臺(tái)發(fā)表主題演講時(shí),他向半導(dǎo)體行業(yè)傳遞了一條熟悉的訊息。

他說(shuō):“計(jì)算需求在快速增加。”并且工藝升級(jí)本身不足以趕上需求的增長(zhǎng)步伐。他的團(tuán)隊(duì)需要確保客戶跑贏這些快速的變化,這也是Cube(立體)技術(shù)誕生背后的主要推手。

3D IC Cube技術(shù)將芯片堆疊為一個(gè)立體的結(jié)構(gòu),將多種解決方案的性能集成到一個(gè)統(tǒng)一的單元中。堆疊后芯片之間的通信速度更快,因?yàn)榕c一維平面芯片設(shè)計(jì)相比,交換信息時(shí)信息的傳遞距離更短。節(jié)省空間和成本也是這種方案的優(yōu)點(diǎn)之一。

不過(guò)也許更重要的是,它改進(jìn)了對(duì)所謂“異構(gòu)集成”的應(yīng)用,即在單個(gè)堆棧中綜合多個(gè)互補(bǔ)的芯片,從而綜合利用各自的優(yōu)點(diǎn)。

“例如,頂部裸片可能是用于實(shí)現(xiàn)高性能的3GAA。底部裸片可能是SF4,甚至傳統(tǒng)節(jié)點(diǎn)的芯片,用于節(jié)省成本或進(jìn)行 IP 復(fù)用”,Kim介紹說(shuō)。

通過(guò)在小空間容納更多的功能,3D IC解決方案擴(kuò)展了摩爾定律的翻倍能力,這在平面芯片時(shí)代是不可想象的。

而正如預(yù)期的那樣,在平面芯片中創(chuàng)建立體設(shè)計(jì)帶來(lái)了新的晶圓代工挑戰(zhàn)。

3D設(shè)計(jì)的挑戰(zhàn)

3D IC解決方案只能利用先進(jìn)的晶圓代工工藝來(lái)實(shí)現(xiàn),沒(méi)有硅通孔(TSV)技術(shù),立體解決方案根本無(wú)法實(shí)現(xiàn)。

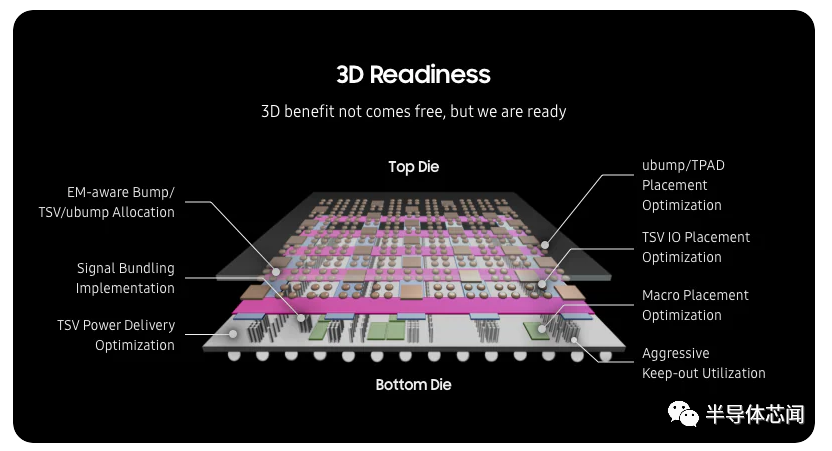

這種技術(shù)讓晶圓之間的連接更快速、更高效。在立體結(jié)構(gòu)中,TSV用于為頂部裸片構(gòu)建PDN,同時(shí)對(duì)于頂部和底部裸片之間的信號(hào)傳輸也至關(guān)重要,從而提供客戶需要的超快連接。使用TSV技術(shù)需要克服多方面的挑戰(zhàn)。除此之外,我們需要提供一個(gè)電量傳輸網(wǎng)絡(luò),以通過(guò)這些TSV和Ubump來(lái)支持3D IC堆棧,同時(shí)還必須滿足IR和電磁輻射(EM)要求。

在同一裸片中支持中間層TSV和最后一層TSV,是我們找到的低電阻電量傳輸解決方案。我們還支持多種類型的TSV捆綁,以進(jìn)一步減少高性能應(yīng)用的IR/EM風(fēng)險(xiǎn)。此外,我們通過(guò)應(yīng)力模擬和硅驗(yàn)證減少了TSV及其排除區(qū)城浪費(fèi),從而可以將某些器件放置到排除區(qū)城中,減少面積浪費(fèi)。最后,我們開發(fā)了一種更傾向宏觀整體的平面擺放指南,以讓我們的設(shè)計(jì)流程具有TSV意識(shí)。

基于Ubump鍵合技術(shù)是3D IC工藝的另一關(guān)鍵技術(shù)。Samsung Foundry的Ubump鍵合技術(shù)經(jīng)過(guò)了各種解決方案的測(cè)試,并已獲準(zhǔn)量產(chǎn),讓3D IC能夠以低成本在各種設(shè)備中實(shí)現(xiàn)。這讓客戶可以利用這些基本的技術(shù)以及 PDK、DK、IP、DM設(shè)計(jì)基礎(chǔ)設(shè)施,輕松開始設(shè)計(jì)3D IC。

一個(gè)設(shè)計(jì)問(wèn)題

不過(guò)在實(shí)施3D IC解決方案時(shí),存在另一個(gè)平面芯片不會(huì)出現(xiàn)的問(wèn)題:功能模組是該放在頂部還是底部?

為幫助客戶解答這一問(wèn)題,我們與 EDA 合作伙伴聯(lián)合開發(fā)了一種分區(qū)方法論,以在早期設(shè)計(jì)階段使用。借助這些方法論,每個(gè)DOE都可以進(jìn)行電壓降(IR)分析,并讓設(shè)計(jì)師可以選擇適合其用途的候選方案。其優(yōu)勢(shì)是多方面的:通過(guò)從適合的候選分區(qū)方案開始3D IC設(shè)計(jì),相較傳統(tǒng)方法,可縮短交付周期。

盡管立體設(shè)計(jì)存在多方面的挑戰(zhàn),我們只需在傳統(tǒng)2D設(shè)計(jì)工作流程的基礎(chǔ)上增加幾個(gè)額外的步驟,即可創(chuàng)建 3D 設(shè)計(jì)。其中大部分額外的步驟都在于TSV的放置,此外頂部和底部裸片之間的 Ubump對(duì)齊也需要單獨(dú)的步驟。

為確保性能達(dá)到并超越標(biāo)準(zhǔn),我們高度重視測(cè)試。我們首先對(duì)頂部和底部裸片進(jìn)行單獨(dú)測(cè)試,然后對(duì)整個(gè)3D結(jié)構(gòu)進(jìn)行IEEE標(biāo)準(zhǔn)1838測(cè)試,以確保理想的裸片堆疊。

“由于這種解決方案為鍵合前和鍵合后測(cè)試提供了基本的3D測(cè)試架構(gòu),它不僅讓我們有機(jī)會(huì)提高堆疊裸片模式的效率,同時(shí)也有利于保證質(zhì)量”,Kim向參加三星SAFE論壇的觀眾解釋道。如果測(cè)試結(jié)果顯示存在預(yù)料之外的缺陷,三星的智能通道修復(fù)解決方案可進(jìn)行必要的修改來(lái)提高良率。

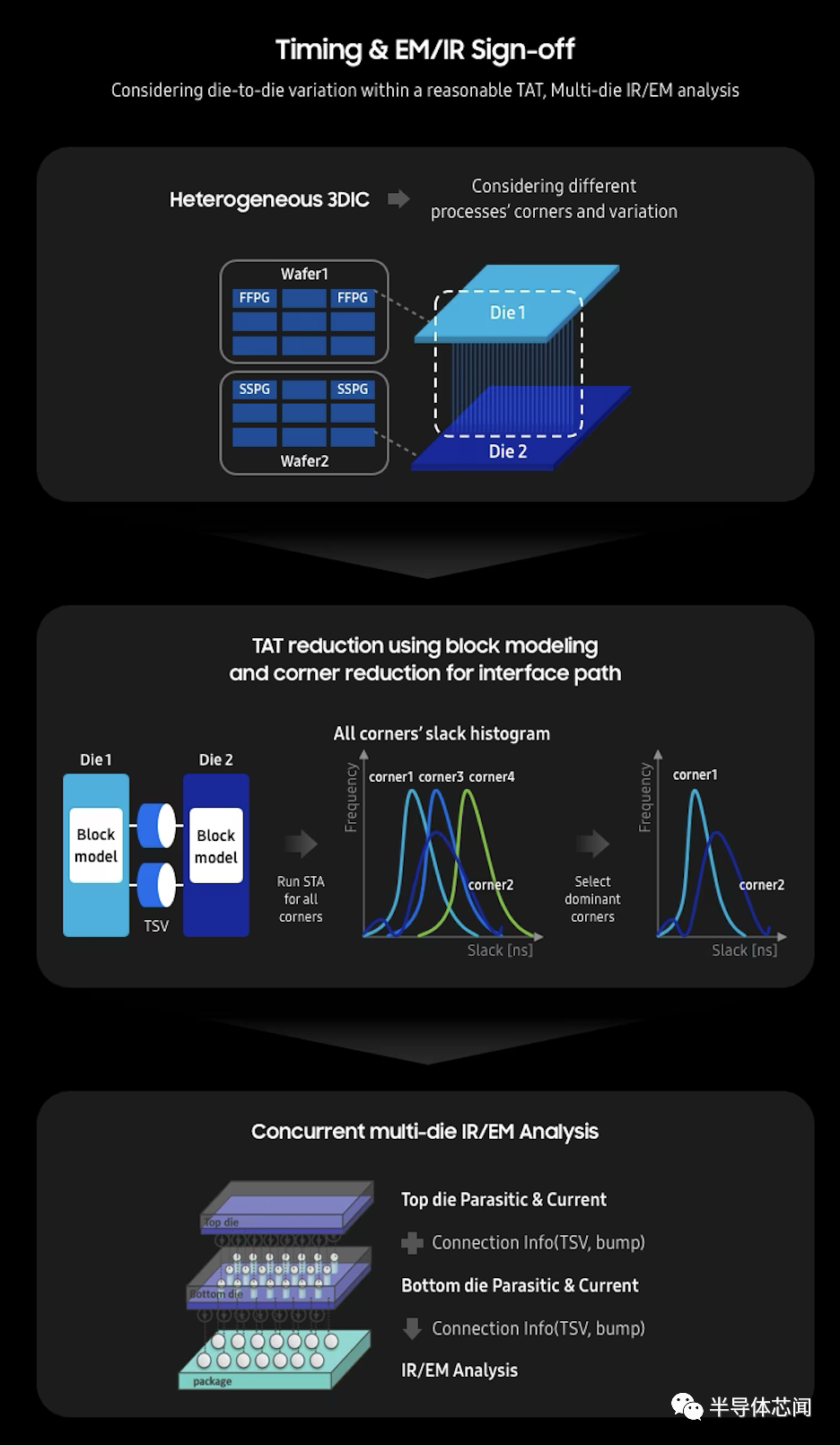

減少關(guān)口以改進(jìn)簽收時(shí)序

簽收挑戰(zhàn)是3D IC架構(gòu)的天然結(jié)果——這是指不同的簽收關(guān)口可能缺乏控制。這是在每個(gè)芯片上使用不同的技術(shù)進(jìn)行制造的副作用。為解決這一問(wèn)題,三星開發(fā)了一種稱為減少關(guān)口的新方法學(xué),這種方法在時(shí)序簽收中使用主導(dǎo)關(guān)口,而不是全部的組合。

而對(duì)于IR/EM簽收,三星面臨了一種完全不同的挑戰(zhàn)。由于裸片通過(guò)TSV供電,后者在現(xiàn)有的 2D 設(shè)計(jì)中是不存在的,每個(gè)裸片的電壓降(IR)/ 電遷移(EM)可能會(huì)相互影響。為解決這一問(wèn)題,我們同時(shí)分析了多芯片的 IR/EM。

攜手重塑性能

緊密合作是半導(dǎo)體創(chuàng)新的重要推動(dòng)力量,許多解決方案都是我們與EDA生態(tài)系統(tǒng)合作伙伴共同努力的直接結(jié)晶。

“當(dāng)然,克服新的技術(shù)挑戰(zhàn)只是我們與EDA合作的內(nèi)容之一”,Kim提醒觀眾。Samsung Foundry與四家主要的EDA攜手,成功開發(fā)了從合成到簽核的3D IC設(shè)計(jì)工作流程,這一成功的實(shí)現(xiàn)與專注于創(chuàng)造更優(yōu)工作流程的SAFE EDA合作伙伴的幫助不可分割。

無(wú)論是哪種技術(shù),變革都來(lái)自于客戶的需求。對(duì)多芯片堆疊技術(shù)的需求與日俱增,催生出2.5D和3D解決方案,打開了新的性能和能效維度。而要滿足這些需求,并沒(méi)有一招鮮吃遍天的方法。這需要我們走出平面思維的局限,在全新的維度中探索。就如人類擺脫地球是平的這一認(rèn)識(shí),Samsung Foundry不斷突破自我,以重塑其產(chǎn)品和行業(yè),努力為客戶提供更高層次的創(chuàng)新。

-

晶圓廠

+關(guān)注

關(guān)注

7文章

618瀏覽量

37813 -

3D封裝

+關(guān)注

關(guān)注

7文章

131瀏覽量

27094 -

三星

+關(guān)注

關(guān)注

1文章

1503瀏覽量

31125

原文標(biāo)題:三星晶圓廠,最新路線圖

文章出處:【微信號(hào):光刻人的世界,微信公眾號(hào):光刻人的世界】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

未來(lái)10年智能傳感器怎么發(fā)展?美國(guó)發(fā)布最新MEMS路線圖

三星加速2nm及1.4nm制程投資

三星暫停兩大晶圓廠建設(shè)計(jì)劃

三星電子計(jì)劃在2026年推出最后一代10nm級(jí)工藝1d nm

2024學(xué)習(xí)生成式AI的最佳路線圖

三星電子公布2024年異構(gòu)集成路線圖,LP Wide I/O移動(dòng)內(nèi)存即將面世

三星展望2027年:1.4nm工藝與先進(jìn)供電技術(shù)登場(chǎng)

三星公布最新工藝路線圖

三星芯片制造技術(shù)路線圖出爐,意強(qiáng)化AI芯片代工市場(chǎng)競(jìng)爭(zhēng)力

英飛凌為AI數(shù)據(jù)中心提供先進(jìn)的高能效電源裝置產(chǎn)品路線圖

事關(guān)衛(wèi)星物聯(lián)網(wǎng)!LoRaWAN 2027 發(fā)展路線圖重磅公布

美國(guó)公布3D半導(dǎo)體路線圖

英特爾晶圓代工業(yè)務(wù)再升級(jí),新路線圖出爐

三星晶圓廠,最新路線圖

三星晶圓廠,最新路線圖

評(píng)論