今天我們介紹的時序分析基本概念是 Virtual Clock ,中文名稱是虛擬時鐘。我們通常說的create_clock, create_generated_clock 都是real clock。而virtual clock則不掛在任何port或者pin上,只是虛擬創(chuàng)建出來的時鐘。如下所示:

#定義虛擬時鐘

create_clock -name VCLK -period 10 -waveform {0 5}

為什么我們要定義virtual clock?

我們通常會把input/output delay掛在virtual clock上,因為input/output delay約束本來就是指片外的時鐘,所以掛在virtual clock上較為合理。

如上圖所示:片外的時鐘CLK2和片內(nèi)的時鐘CLK1頻率不同。這樣的情況下,如何來定義input port {in1}上的約束?

這時,我們就可以給input port {in1}創(chuàng)建一個virtual clock。

create_clock -name VCLK2 -period 10 -waveform {2 8}

create_clock -name CLK1 -period 8 -waveform {0 4} [get_ports clk]

set_input_delay -clock VCLK2 -max 2.7 [get_ports in1]

-

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22551 -

虛擬時鐘

+關(guān)注

關(guān)注

0文章

5瀏覽量

6574 -

虛擬機

+關(guān)注

關(guān)注

1文章

908瀏覽量

28091 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17126 -

時序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5270

發(fā)布評論請先 登錄

相關(guān)推薦

時序分析基本概念介紹<Operating Condition>

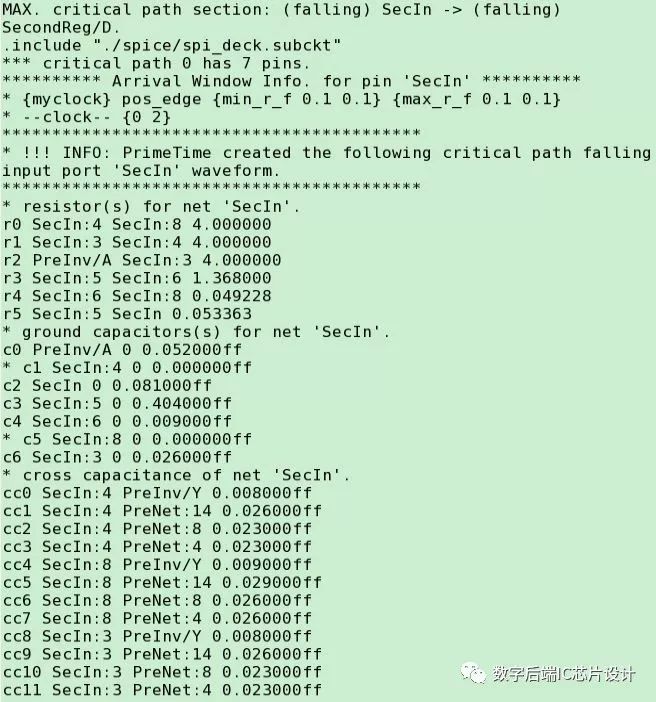

時序分析基本概念介紹&lt;spice deck&gt;

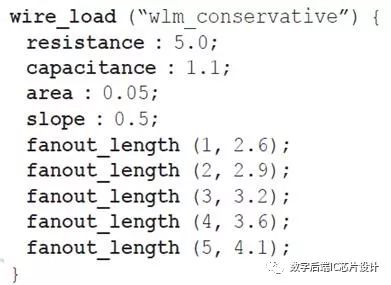

時序分析基本概念介紹&lt;wire load model&gt;

時序分析基本概念介紹&lt;ILM&gt;

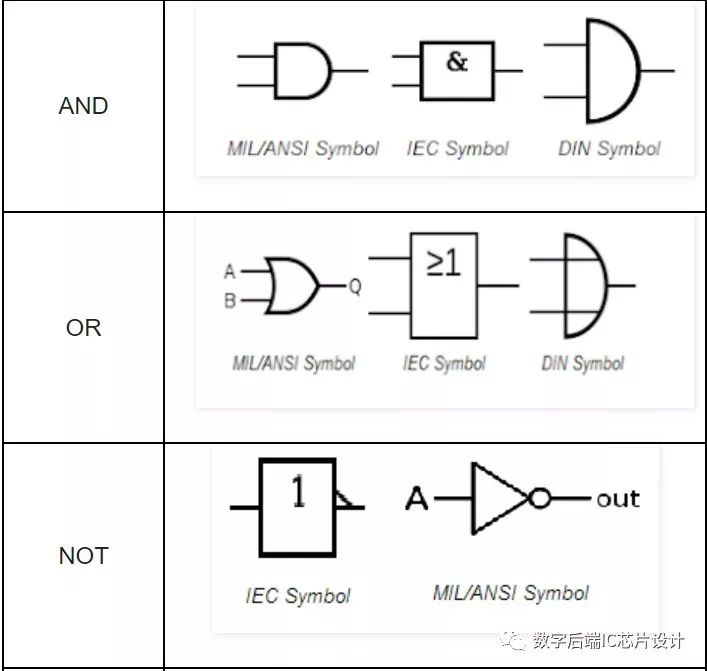

時序分析基本概念介紹&lt;Combinational logic&gt;

時序分析基本概念介紹<Virtual Clock>

時序分析基本概念介紹<Virtual Clock>

評論