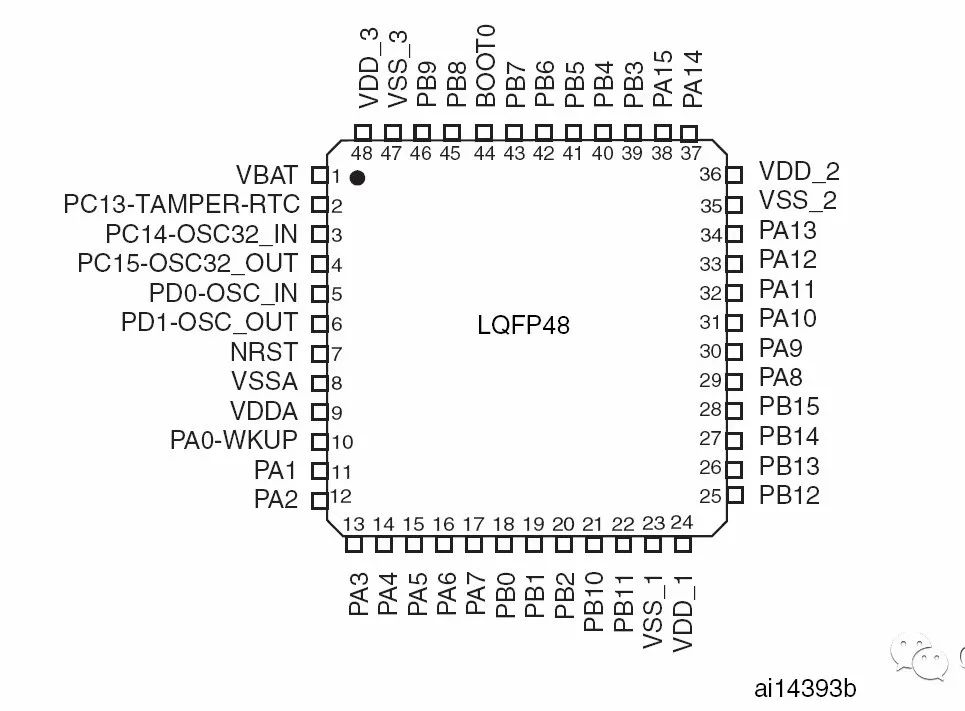

2.1 STM32F103xx增強型LQFP48引腳分布

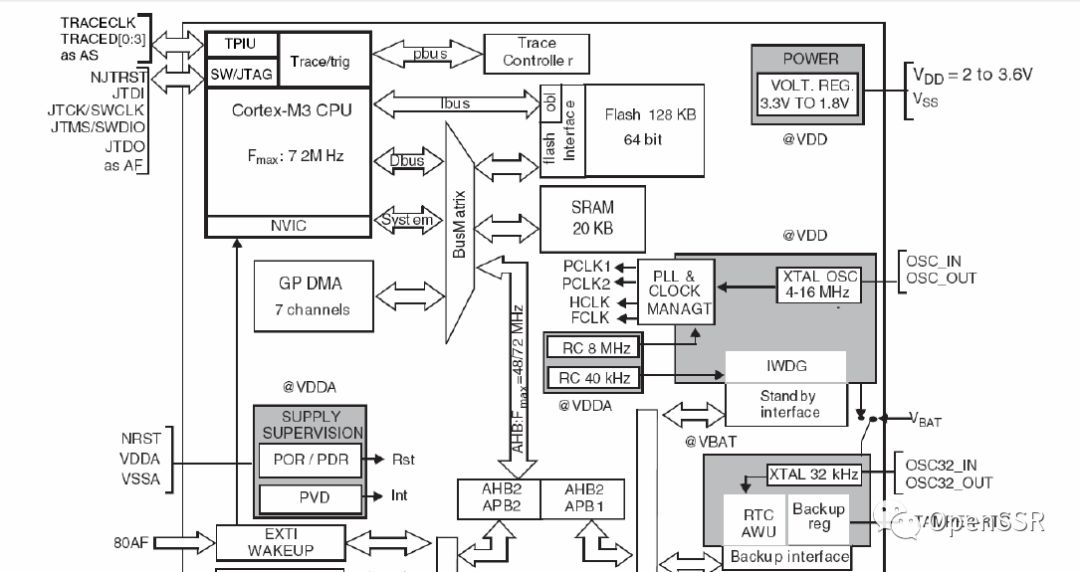

2.2 STM32F103xx概述

2.2.1 ARM?的Cortex?-M3核心并內嵌閃存和SRAM

ARM的Cortex?-M3處理器是最新一代的嵌入式ARM處理器,它為實現MCU的需要提供了低成本的平臺、縮減的引腳數目、降低的系統功耗,同時提供卓越的計算性能和先進的中斷系統響應。

ARM的Cortex?-M3是32位的RISC處理器,提供額外的代碼效率,在通常8和16位系統的存儲空間上發揮了ARM內核的高性能。

2.2.2 內置閃存存儲器

64K或128K字節的內置閃存存儲器,用于存放程序和數據。小R使用的開發板內置閃存存儲器為64K。

2.2.3 CRC(循環冗余校驗)計算單元

CRC(循環冗余校驗)計算單元使用一個固定的多項式發生器,從一個32位的數據字產生一個CRC碼。在眾多的應用中,基于CRC的技術被用于驗證數據傳輸或存儲的一致性。

2.2.4 內置SRAM

20K字節的內置SRAM,CPU能以0等待周期訪問(讀/寫)。

2.2.5 嵌套的向量式中斷控制器(NVIC)

STM32F103xx增強型產品內置嵌套的向量式中斷控制器,能夠處理多達43個可屏蔽中斷通道(不包括16個Cortex?-M3的中斷線)和16個優先級。

● 緊耦合的NVIC能夠達到低延遲的中斷響應處理

● 中斷向量入口地址直接進入內核

● 緊耦合的NVIC接口

● 允許中斷的早期處理

● 處理晚到的較高優先級中斷

● 支持中斷尾部鏈接功能

● 自動保存處理器狀態

● 中斷返回時自動恢復,無需額外指令開銷

該模塊以最小的中斷延遲提供靈活的中斷管理功能。

2.2.6 外部中斷/事件控制器(EXTI)

外部中斷/事件控制器包含19個邊沿檢測器,用于產生中斷/事件請求。每個中斷線都可以獨立地配置它的觸發事件(上升沿或下降沿或雙邊沿),并能夠單獨地被屏蔽;有一個掛起寄存器維持所有中斷請求的狀態。

EXTI可以檢測到脈沖寬度小于內部APB2的時鐘周期。多達80個通用I/O口連接到16個外部中斷線。

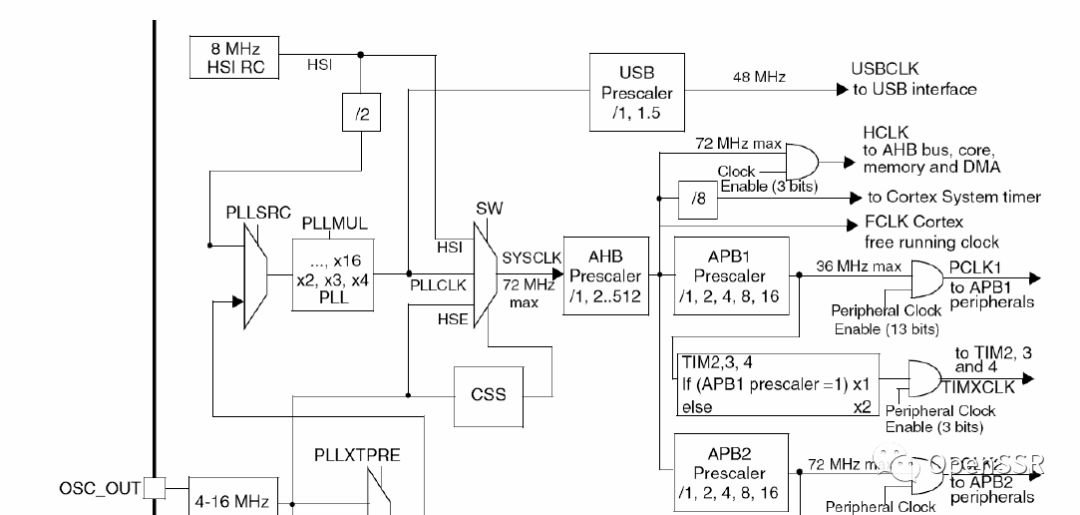

2.2.7 時鐘和啟動

系統時鐘的選擇是在啟動時進行,復位時內部8MHz的RC振蕩器被選為默認的CPU時鐘,隨后可以選擇外部的、具失效監控的4~16MHz時鐘;當檢測到外部時鐘失效時,它將被隔離,系統將自動地切換到內部的RC振蕩器,如果使能了中斷,軟件可以接收到相應的中斷。同樣,在需要時可以采取對PLL時鐘完全的中斷管理(如當一個間接使用的外部振蕩器失效時)。

多個預分頻器用于配置AHB的頻率、高速APB(APB2)和低APB(APB1)區域。AHB和高速APB的最高頻率是72MHz,低速APB的最高頻率為36MHz。

2.2.8 自舉模式

在啟動時,通過自舉引腳可以選擇三種自舉模式中的一種:

● 從程序閃存存儲器自舉

● 從系統存儲器自舉

● 從內部SRAM自舉

自舉加載程序(Bootloader)存放于系統存儲器中,可以通過USART1對閃存重新編程。

2.2.9 供電方案

● VDD = 2.0~3.6V:VDD引腳為I/O引腳和內部調壓器供電。

● VSSA,VDDA = 2.0~3.6V:為ADC、復位模塊、RC振蕩器和PLL的模擬部分提供供電。使用ADC時,VDDA不得小于2.4V。VDDA和VSSA必須分別連接到VDD和VSS。

● VBAT = 1.8~3.6V:當關閉VDD時,(通過內部電源切換器)為RTC、外部32kHz振蕩器和后備寄存器供電。

2.2.10 供電監控器

本產品內部集成了上電復位(POR)/掉電復位(PDR)電路,該電路始終處于工作狀態,保證系統在供電超過2V時工作;當VDD低于設定的閥值(VPOR/PDR)時,置器件于復位狀態,而不必使用外部復位電路。

器件中還有一個可編程電壓監測器(PVD),它監視VDD/VDDA供電并與閥值VPVD比較,當VDD低于或高于閥值VPVD時產生中斷,中斷處理程序可以發出警告信息或將微控制器轉入安全模式。PVD功能需要通過程序開啟。

2.2.11 電壓調壓器

調壓器有三個操作模式:主模式(MR)、低功耗模式(LPR)和關斷模式

● 主模式(MR)用于正常的運行操作

● 低功耗模式(LPR)用于CPU的停機模式

● 關斷模式用于CPU的待機模式:調壓器的輸出為高阻狀態。

2.2.12 低功耗模式

STM32F103xC、STM32F103xD和STM32F103xE增強型產品支持三種低功耗模式,可以在要求低功耗、短啟動時間和多種喚醒事件之間達到最佳的平衡。

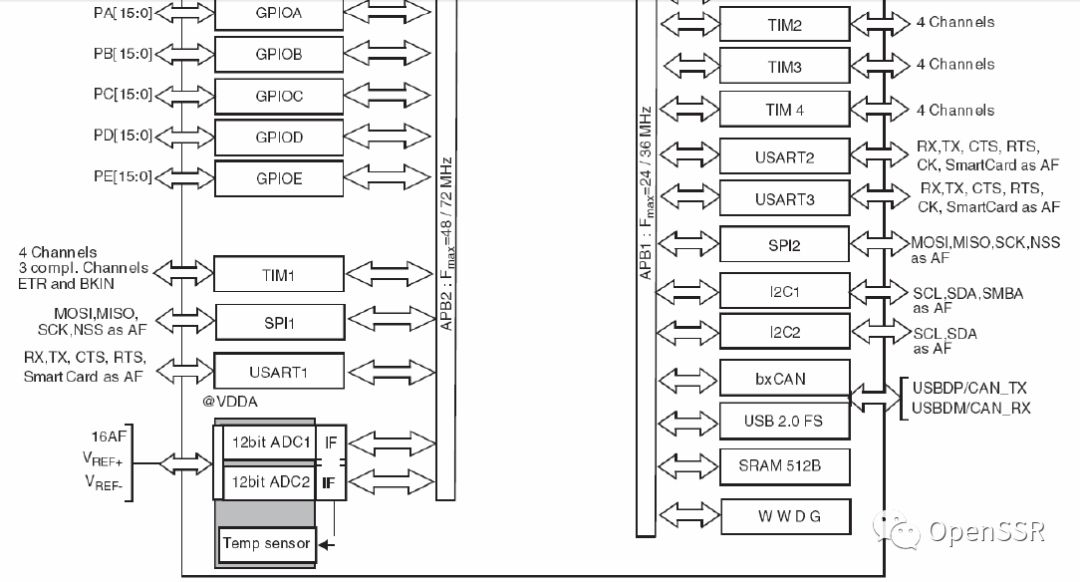

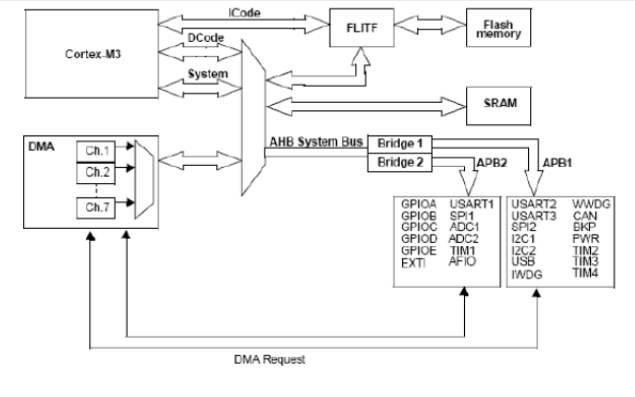

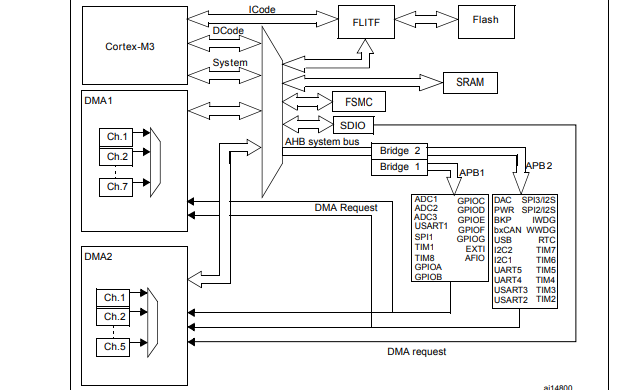

2.2.13 DMA

靈活的7路通用DMA可以管理存儲器到存儲器、設備到存儲器和存儲器到設備的數據傳輸;DMA控制器支持環形緩沖區的管理,避免了控制器傳輸到達緩沖區結尾時所產生的中斷。

每個通道都有專門的硬件DMA請求邏輯,同時可以由軟件觸發每個通道;傳輸的長度、傳輸的源地址和目標地址都可以通過軟件單獨設置。

DMA可以用于主要的外設:SPI、I2C、USART,通用、基本和高級控制定時器TIMx和ADC。

2.2.14 RTC(實時時鐘)和后備寄存器

中等容量的STM32F103xx增強型系列產品包含1個高級控制定時器、3個普通定時器,以及2個看門狗定時器和1個系統嘀嗒定時器。

高級控制定時器(TIM1)可以被看成是分配到6個通道的三相PWM發生器,它具有帶死區插入的互補PWM輸出,還可以被當成完整的通用定時器。四個獨立的通道可以用于:

● 輸入捕獲

● 輸出比較

● 產生PWM(邊緣或中心對齊模式)

● 單脈沖輸出

配置為16位標準定時器時,它與TIMx定時器具有相同的功能。配置為16位PWM發生器時,它具有全調制能力(0~100%)。

通用定時器(TIMx)

STM32F103xx增強型產品中,內置了多達3個可同步運行的標準定時器(TIM2、TIM3和TIM4)。每個定時器都有一個16位的自動加載遞加/遞減計數器、一個16位的預分頻器和4個獨立的通道,每個通道都可用于輸入捕獲、輸出比較、PWM和單脈沖模式輸出,在最大的封裝配置中可提供最多12個輸入捕獲、輸出比較或PWM通道。

它們還能通過定時器鏈接功能與高級控制定時器共同工作,提供同步或事件鏈接功能。在調試模式下,計數器可以被凍結。任一標準定時器都能用于產生PWM輸出。每個定時器都有獨立的DMA請求機制。

這些定時器還能夠處理增量編碼器的信號,也能處理1至3個霍爾傳感器的數字輸出。

2.2.16 IIC總線

多達2個I2C總線接口,能夠工作于多主模式或從模式,支持標準和快速模式。I2C接口支持7位或10位尋址,7位從模式時支持雙從地址尋址。內置了硬件CRC發生器/校驗器。它們可以使用DMA操作并支持SMBus總線2.0版/PMBus總線。

2.2.17 通用同步/異步收發器(USART)

USART1接口通信速率可達4.5兆位/秒,其他接口的通信速率可達2.25兆位/秒。USART接口具有硬件的CTS和RTS信號管理、支持IrDA SIR ENDEC傳輸編解碼、兼容ISO7816的智能卡并提供LIN主/從功能。

所有USART接口都可以使用DMA操作。

2.2.18 串行外設接口(SPI)

多達2個SPI接口,在從或主模式下,全雙工和半雙工的通信速率可達18兆位/秒。3位的預分頻器可產生8種主模式頻率,可配置成每幀8位或16位。硬件的CRC產生/校驗支持基本的SD卡和MMC模式。所有的SPI接口都可以使用DMA操作。

CAN接口兼容規范2.0A和2.0B(主動),位速率高達1兆位/秒。它可以接收和發送11位標識符的標準幀,也可以接收和發送29位標識符的擴展幀。具有3個發送郵箱和2個接收FIFO,3級14個可調節的濾波器。

2.2.20 通用串行總線(USB)

STM32F103xx增強型系列產品,內嵌一個兼容全速USB的設備控制器,遵循全速USB設備(12兆位/秒)標準,端點可由軟件配置,具有待機/喚醒功能。USB專用的48MHz時鐘由內部主PLL直接產生(時鐘源必須是一個HSE晶體振蕩器)。

2.2.21 通用輸入輸出接口(GPIO)

每個GPIO引腳都可以由軟件配置成輸出(推挽或開漏)、輸入(帶或不帶上拉或下拉)或復用的外設功能端口。多數GPIO引腳都與數字或模擬的復用外設共用。

除了具有模擬輸入功能的端口,所有的GPIO引腳都有大電流通過能力。在需要的情況下,I/O引腳的外設功能可以通過一個特定的操作鎖定,以避免意外的寫入I/O寄存器。

在APB2上的I/O腳可達18MHz的翻轉速度。

2.2.22 ADC(模擬/數字轉換器)

STM32F103xx增強型產品內嵌2個12位的模擬/數字轉換器(ADC),每個ADC共用多達16個外部通道,可以實現單次或掃描轉換。在掃描模式下,自動進行在選定的一組模擬輸入上的轉換。

ADC接口上的其它邏輯功能包括:

● 同步的采樣和保持

● 交叉的采樣和保持

● 單次采樣

ADC可以使用DMA操作。

模擬看門狗功能允許非常精準地監視一路、多路或所有選中的通道,當被監視的信號超出預置的閥值時,將產生中斷。由標準定時器(TIMx)和高級控制定時器(TIM1)產生的事件,可以分別內部級聯到ADC的開始觸發和注入觸發,應用程序能使AD轉換與時鐘同步。

2.2.23 溫度傳感器

溫度傳感器產生一個隨溫度線性變化的電壓,轉換范圍在2V < VDDA < 3.6V之間。溫度傳感器在內部被連接到ADC12_IN16的輸入通道上,用于將傳感器的輸出轉換到數字數值。

2.2.24 串行單線JTAG調試口(SWJ-DP)

內嵌ARM的SWJ-DP接口,這是一個結合了JTAG和串行單線調試的接口,可以實現串行單線調試接口或JTAG接口的連接。JTAG的TMS和TCK信號分別與SWDIO和SWCLK共用引腳,TMS腳上的一個特殊的信號序列用于在JTAG-DP和SW-DP間切換。

2.3 STM32F103xx增強型模塊框圖

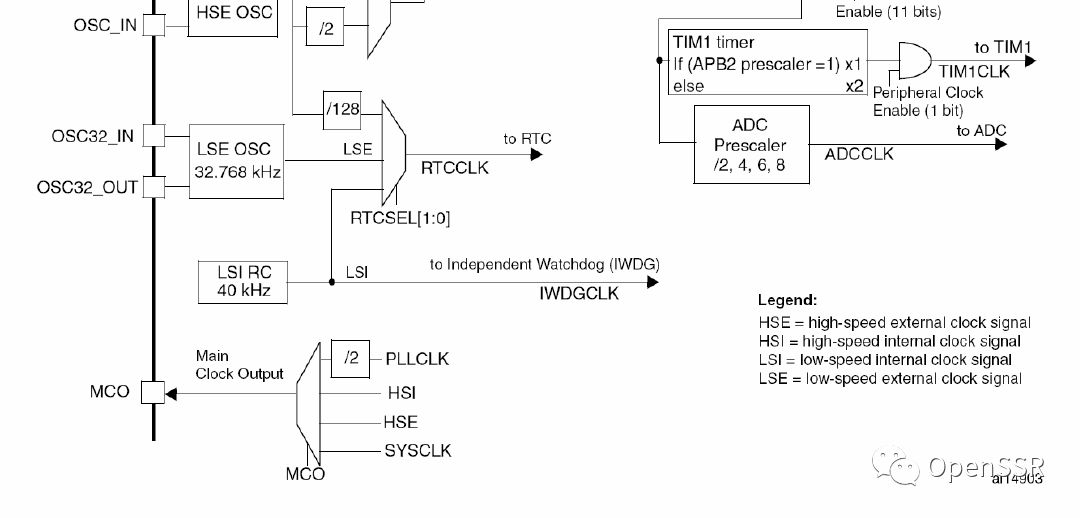

2.4 STM32F103xx時鐘樹

-

嵌入式系統

+關注

關注

41文章

3567瀏覽量

129227 -

ARM處理器

+關注

關注

6文章

360瀏覽量

41663 -

STM32F103

+關注

關注

33文章

476瀏覽量

63478 -

中斷控制器

+關注

關注

0文章

59瀏覽量

9441 -

閃存存儲器

+關注

關注

0文章

21瀏覽量

9124

發布評論請先 登錄

相關推薦

STM32F101xx 和STM32F103xx固件庫(CN)

STM32F101xx和STM32F103xx的固件函數庫詳細整理資料免費下載

STM32F101xx和STM32F103xx微控制器的數據手冊免費下載

基于ARM的32位MCU STM32F101xx和STM32F103xx的參考手冊資料免費下載

STM32F101xx和STM32F103xx ARM高性能微控制器

32位基于ARM微控制器STM32F101xx與STM32F103xx的固件函數庫

AN2604_使用STM32F101xx和STM32F103xx進行RTC校準

STM32F101xx和STM32F103xx微控制器手冊

STM32F101xx和STM32F103xx中文教程及參考手冊

使用STM32F101xx和STM32F103xx的智能卡接口

STM32F103xx內部資源介紹

STM32F103xx內部資源介紹

評論