2023年初,Siemens發布了2022年Functional Verification Study。從中可以看到一些近年的驗證數據,分享幾點個人的愚見。

DE和DV的人數比應該是多少?

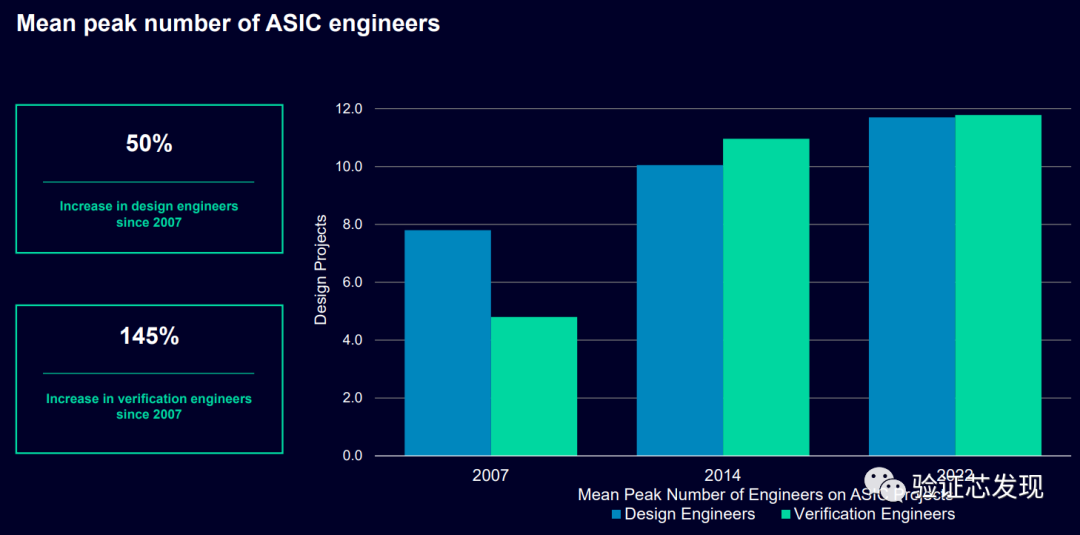

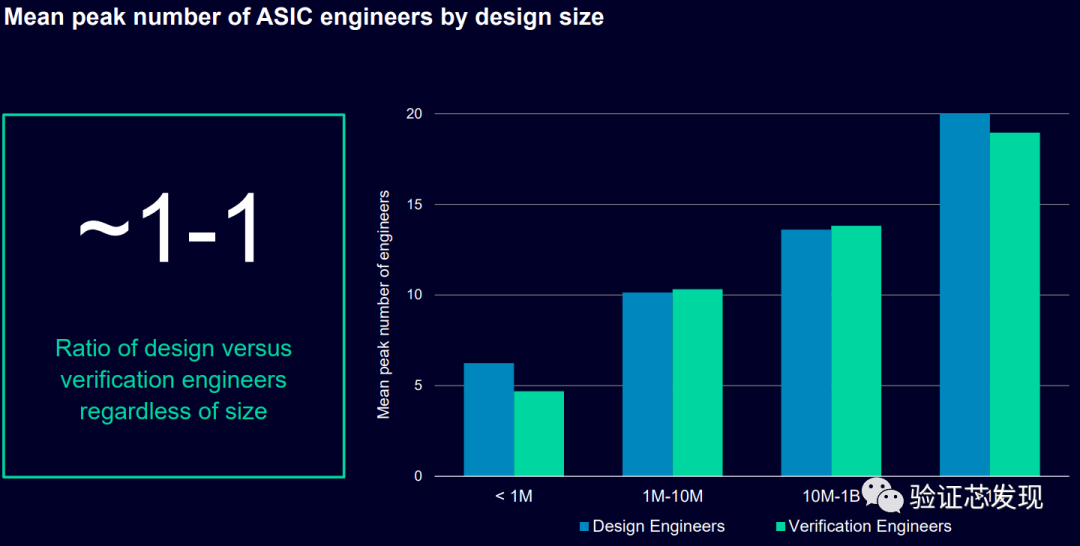

根據調查結果如下圖所示,分別列出了近幾年DE和DV的整體數量比,以及在不同規模領域內的人數比。整體看大部分項目中DE和DV的配比約為1:1。

結果遠沒有達到所謂的1:2,甚至1:3。甚至在超大規模的芯片項目中,DE的數量還會超出DV。1:1的比例還是比較真實的,從作者經歷過的一些項目看,也沒有遇到過DE/DV能達到1:2的公司。

除了數量上沒有達到,還存在一些"奇怪"的現象:DV的"被動"局面。在很多公司或者項目中,DV往往都是一種"被動"的角色。spec的改動或者code修改,DV大多都是處于被通知方,很少有DV能夠參與到architecture或者spec修改的討論中去,有些修改一般也不會征詢DV的意見,甚至有些改動都不會知會DV。這種現象在大公司會有所改善,有著相對規范的流程。在小公司里,則尤為明顯一些。

怎么辦呢?沒有什么好辦法,不要"妄自菲薄",合適的時候發出作為DV的聲音,提升對業務的專業能力。時間在往前走,不要讓自己的認知和技能在原地踏步。如果除了技術因素外,驗證leader的風格有時也會成為重要因素:)

DV的時間都去哪兒了?

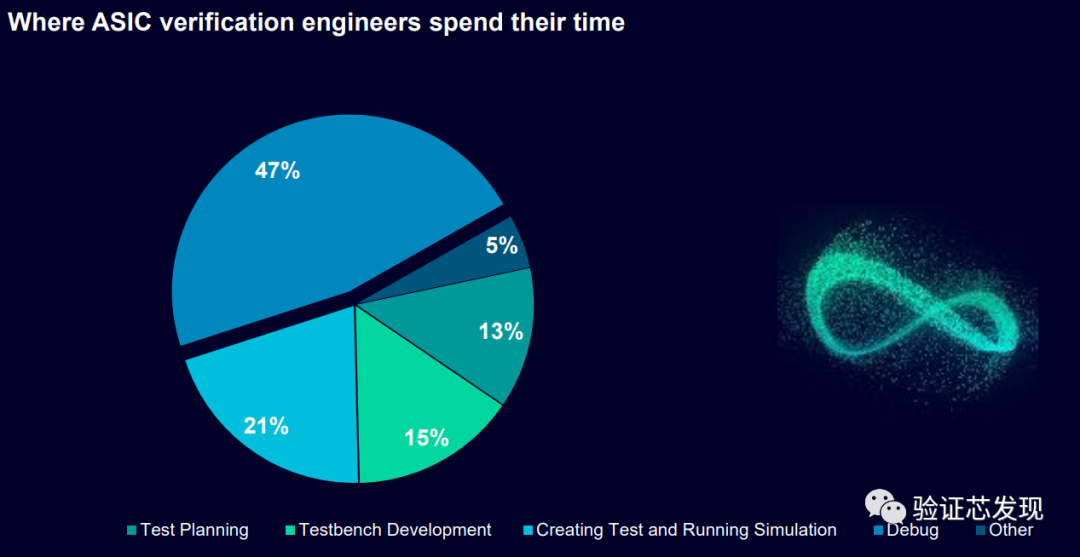

從圖中可以看到,DV的時間的分配:

Test Planning, 13%

Testbench Development, 15%

Creating Test and Running Simulation, 21%

Debug, 47%

Others, 5%

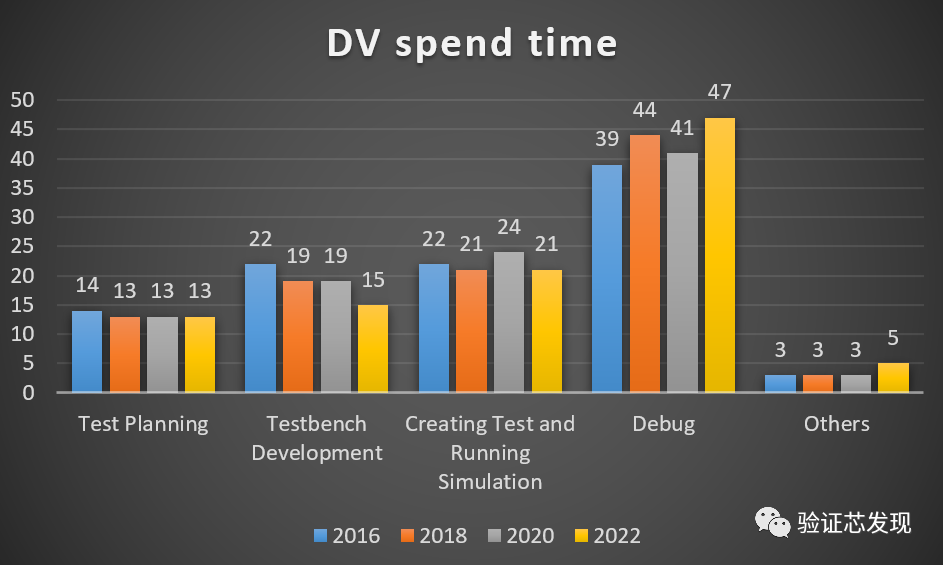

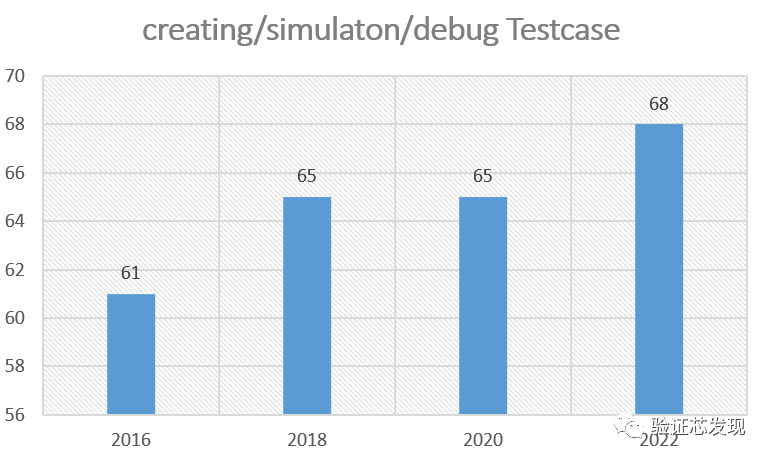

為了對比,作者找來2016,2018年和2020的數據,對比如下:

從上述的對比可以看出,驗證testplan的占比比較穩定,沒有大的變化,占整個驗證周期的13%左右。

Testbench Development的占比則是一直在降低,從2016年的22%下降到15%。腳本和其他的eda自動化構建,包括UVM的廣泛使用,或許是testbench構建效率不斷提升的原因之一。

Case的開發和仿真,2016年以來的數據,有些起伏,但也變化不大,仍占據整個驗證周期的22%左右。而debug過程的占比,一直以來都非常之高,達到40%以上,在2022年的結果中,甚至達到了47%。

如果將creating case和debug統一來看,那么這一過程的趨勢如下:

可以看到,驗證的開發調試過程的占比是處于增長的趨勢,在2020年達到了。隨著諸如AI、自動駕駛等新方向的涌現,也會出現一些較新的領域,如安全驗證等。隨著芯片規模的增長,驗證的復雜度和調式難度也在不斷攀升。驗證周期占整個項目周期的比例也達到50%~60%。

這里還有一個有趣的數據,如果我們把Testbench Development、Creating Test and Running Simulation和Debug看作是testplan的執行過程,那這一過程的占比近年來的數據分別為,2016-83%,2018-84%,2020-84%,2022-83%。看到這個數據,讀者能想到什么呢?

二八定律。

雖然前面的testplan的耗時僅占比13%,但作者相信就是這13%的testplan或者testpoint規劃,就已經確定了80%的驗證完備性。

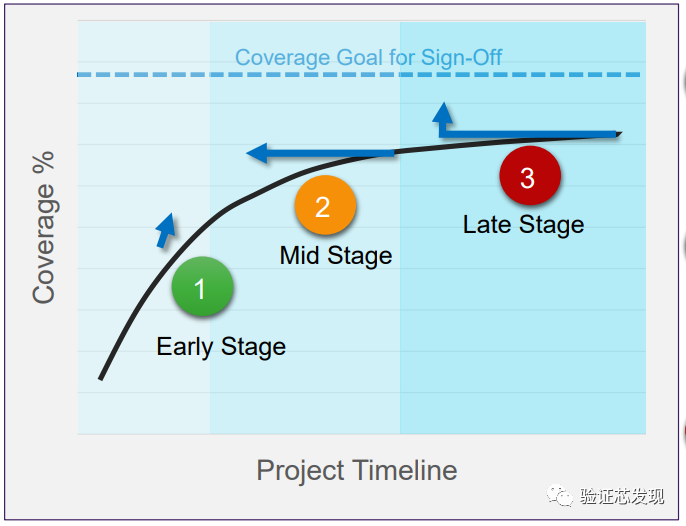

驗證執行中,另一個二八定律是coverage的收集。DV都會有這樣的經歷,當coverage達到80%或者90%以后,就提升很慢了。最后的這10%或者20%的coverage,需要更多的投入,構建各種定向corner case。

[圖片來源:DVCov2023 poster,Accelerating Functional Verification Through Stabilization of Testbench Using AI/ML]

[圖片來源:DVCov2023 poster,Accelerating Functional Verification Through Stabilization of Testbench Using AI/ML]

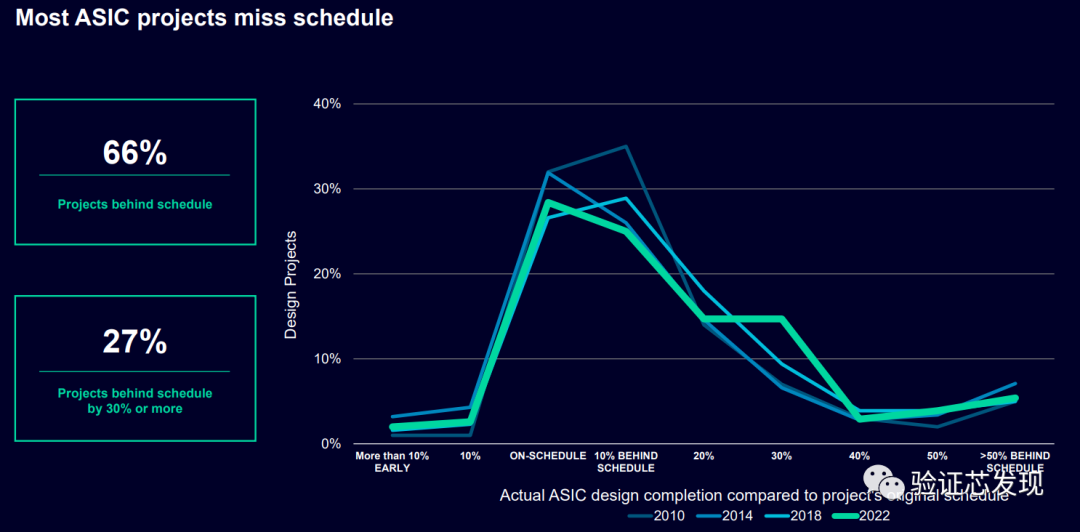

項目進度delay,這正常嗎?

如果某一天,你們的項目進度delay了,不要擔心,并只有你們的項目delay了。根據調查結果顯示,有將近66%的projects會delay。

項目準時交付的原因"千篇一律",計劃制定的好,團隊齊心協力,努力配合。

項目delay的背后也是"豐富多彩",新增需求,計劃不合理,分工不明確,人手不夠,加班來湊:)。

一個芯片項目,打工人,項目經理,QA,老板等人,每個人都從不同的角度審視著,結果導向,質量管理,進度管理,風險管理,溝通管理等等。如果有機會,一定去owner一個項目,能看到不角色對其"利益"的訴求,將會給你帶來非常不一樣的體驗。

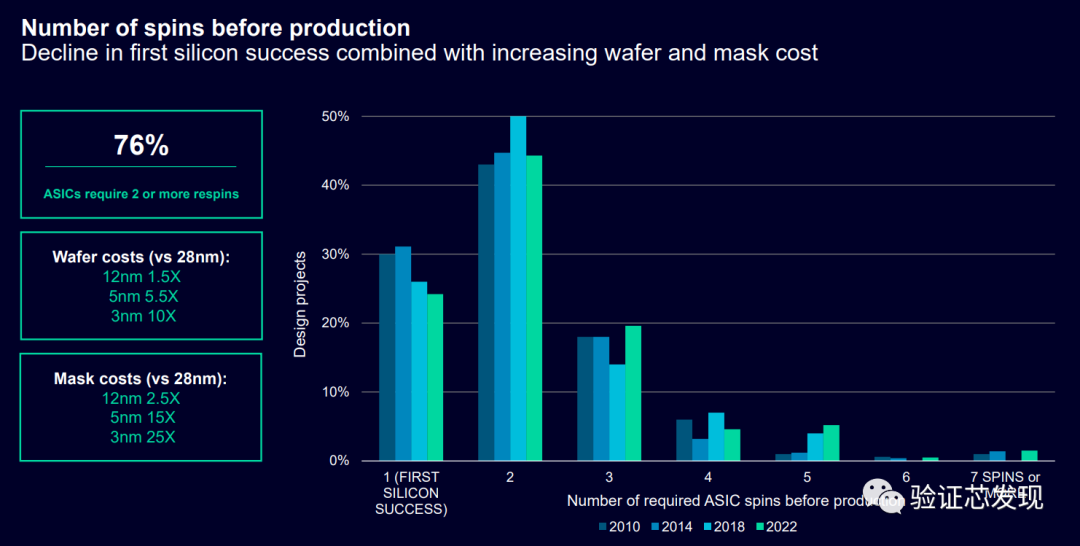

流片,可以一版成功嗎?

雖說成功是偶然,失敗是經常,但每個芯片公司都有一個一版點亮的美好期望,那事實怎么樣呢?

在調查的project中,僅有24%的project可以一版成功!而且隨著隨著工藝節點尺寸的減少,wafer和mask的成本增長非常快。從28nm到3mn,wafer成本增大了10倍,mask成本增大了25倍。

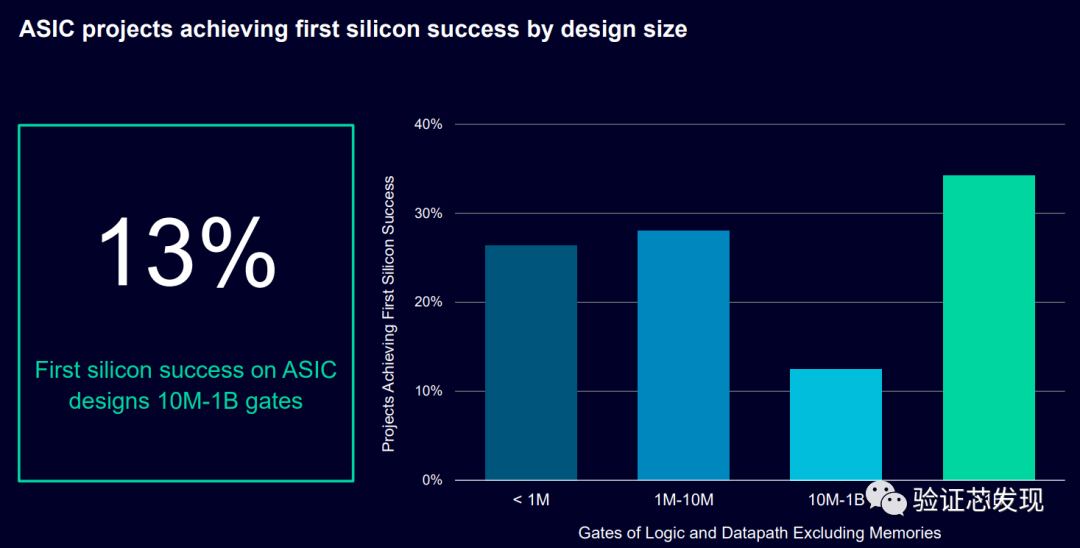

而在可以一版成功的project中,不同芯片規模的成功率也非常有特點。規模處于10M-1B門的芯片,一版成功的比例只有13%。

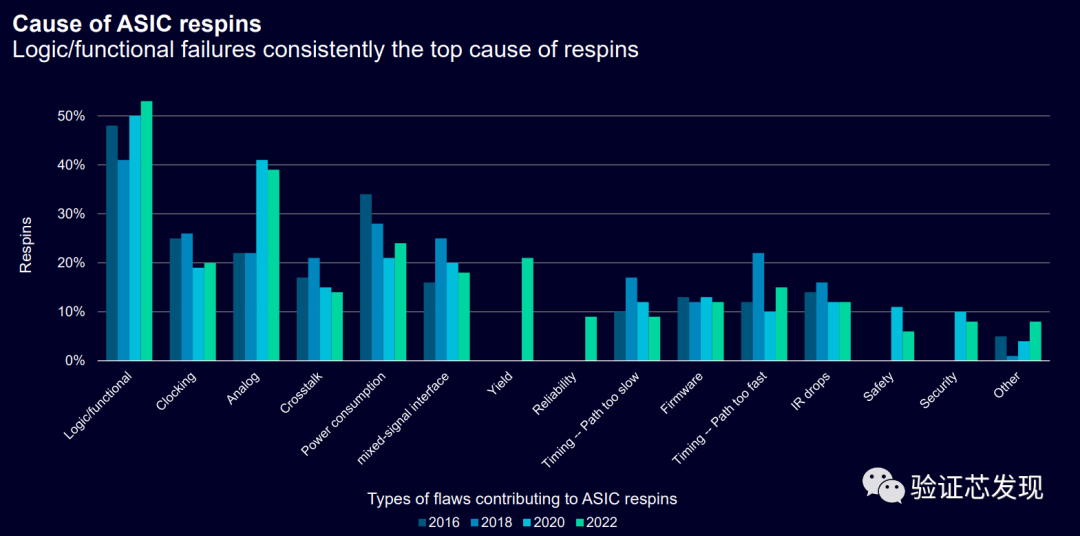

而在各種導致流片失敗的原因中,邏輯和功能錯誤仍是主要原因。

審核編輯:劉清

-

芯片設計

+關注

關注

15文章

1001瀏覽量

54812 -

UVM

+關注

關注

0文章

181瀏覽量

19139 -

SPEC

+關注

關注

0文章

31瀏覽量

15783

原文標題:對驗證現狀的幾點思考

文章出處:【微信號:數字芯片設計工程師,微信公眾號:數字芯片設計工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

阿里智能對話交互實踐及范式思考

關于模擬電子技術實驗教學的思考

編程:思考還是打字

中汽創智科技首席人工智能官丁華杰:AI賦能自動駕駛的幾點思考 精選資料分享

浙江省農田水利投入問題的幾點思考

對國產PLC產業化的幾點思考

關于DC轉換器的幾點思考

對照明產業現狀和趨勢的思考

關于嵌入式軟硬件開發的幾點思考

數字IC驗證之基本的TLM通信

關于新能源汽車電驅系統的幾點思考

對驗證現狀的幾點思考

對驗證現狀的幾點思考

評論