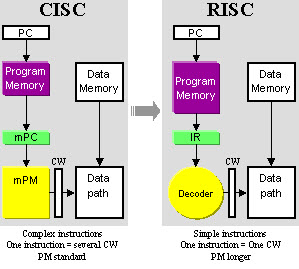

中央處理單元架構(gòu)具有從“指令集架構(gòu)”到其設(shè)計(jì)工作的能力。CPU的架構(gòu)設(shè)計(jì)是RISC(精簡指令集計(jì)算)和CISC(復(fù)雜指令集計(jì)算)。CISC能夠在一個指令集中執(zhí)行尋址模式或多步操作。這是CPU的設(shè)計(jì),其中一條指令執(zhí)行許多底層操作。例如,內(nèi)存存儲、算術(shù)運(yùn)算和從內(nèi)存加載。

RISC是一種CPU設(shè)計(jì)策略,其基于這樣的解釋:簡化指令集與微處理器架構(gòu)結(jié)合后可提供更高的性能,該微處理器架構(gòu)能夠通過每條指令使用一些微處理器周期來執(zhí)行指令。

本文中,單片機(jī)開發(fā)工程師主要介紹了RISC結(jié)構(gòu),及其優(yōu)點(diǎn)和缺點(diǎn)。

一、什么是RISC架構(gòu)?

RISC(精簡指令集計(jì)算機(jī))由于其能效高而用于便攜式設(shè)備。例如,Apple iPod和Nintendo

DS。RISC是一種使用高度優(yōu)化的指令集的微處理器架構(gòu)。RISC則相反,以每個程序的指令數(shù)為代價減少了每個指令的周期。流水線化是RISC的獨(dú)特功能之一。它通過以流水線方式重疊執(zhí)行多個指令來執(zhí)行。與CISC相比,它具有高性能優(yōu)勢。

RISC處理器采用簡單的指令,并在一個時鐘周期內(nèi)執(zhí)行。

二、RISC架構(gòu)的特點(diǎn)

1.RISC架構(gòu)中使用了簡單指令。

2.RISC幫助并支持一些簡單數(shù)據(jù)類型并綜合復(fù)雜數(shù)據(jù)類型。

3.RISC利用簡單的尋址模式和固定長度的指令進(jìn)行流水線處理。

4.RISC允許任何寄存器在任何上下文中使用。

5.單周期執(zhí)行時間。

6.通過分開“LOAD”和“STORE”指令,可以減少計(jì)算機(jī)可以執(zhí)行的工作量。

7.RISC包含大量寄存器,以防止與內(nèi)存進(jìn)行各種交互。

8.在RISC中,流水線操作很容易,因?yàn)樗兄噶畹膱?zhí)行將在統(tǒng)一的時間間隔(即單擊一次)中完成。

9.在RISC中,需要更多RAM來存儲程序集級指令。

10.精簡指令減少了RISC中的晶體管數(shù)量。

11.RISC使用哈佛內(nèi)存模型意味著它是哈佛架構(gòu)。

12.編譯器用于執(zhí)行轉(zhuǎn)換操作,將高級語言語句轉(zhuǎn)換成其形式的代碼。

三、RISC架構(gòu)的優(yōu)勢

1.RISC(精簡指令集計(jì)算)架構(gòu)具有一組指令,因此高級語言編譯器可以生成更有效的代碼。

2.由于其簡單性,它允許自由使用微處理器上的空間。

3.許多RISC處理器使用寄存器來傳遞參數(shù)和保存局部變量。

4.RISC函數(shù)僅使用幾個參數(shù),而RISC處理器無法使用調(diào)用指令,因此,使用易于流水線化的固定長度指令。

5.操作速度可以最大化,執(zhí)行時間可以最小化。

6.所需的指令格式數(shù)量很少,所需的指令數(shù)量和尋址方式也很少。

四、RISC架構(gòu)的缺點(diǎn)

1.通常,RISC處理器的性能取決于程序員或編譯器,因?yàn)樵趯ISC代碼更改為RISC代碼時,編譯器的知識起著至關(guān)重要的作用。

2.在將CISC代碼重新排列為RISC代碼(稱為代碼擴(kuò)展)時,將會增加大小。并且,此代碼擴(kuò)展的質(zhì)量將再次取決于編譯器以及機(jī)器的指令集。

3.RISC處理器的一級緩存也是RISC的缺點(diǎn),其中這些處理器在芯片本身上具有大容量的內(nèi)存緩存。為了提供指令,它們需要非常快速的存儲系統(tǒng)。

-

cpu

+關(guān)注

關(guān)注

68文章

10825瀏覽量

211151 -

RISC

+關(guān)注

關(guān)注

6文章

461瀏覽量

83654

發(fā)布評論請先 登錄

相關(guān)推薦

開關(guān)電源拓?fù)?b class='flag-5'>結(jié)構(gòu)特點(diǎn)和優(yōu)缺點(diǎn)對比

常見開關(guān)電源拓?fù)?b class='flag-5'>結(jié)構(gòu)的特點(diǎn)和優(yōu)缺點(diǎn)對比

RISC-V有哪些優(yōu)缺點(diǎn)?是堅(jiān)持ARM方向還是投入risc-V的懷抱?

接入網(wǎng)四種結(jié)構(gòu)的優(yōu)缺點(diǎn)

貼片機(jī)轉(zhuǎn)塔式結(jié)構(gòu)的優(yōu)缺點(diǎn)是什么?有什么局限性?

LwIP的優(yōu)缺點(diǎn)是什么

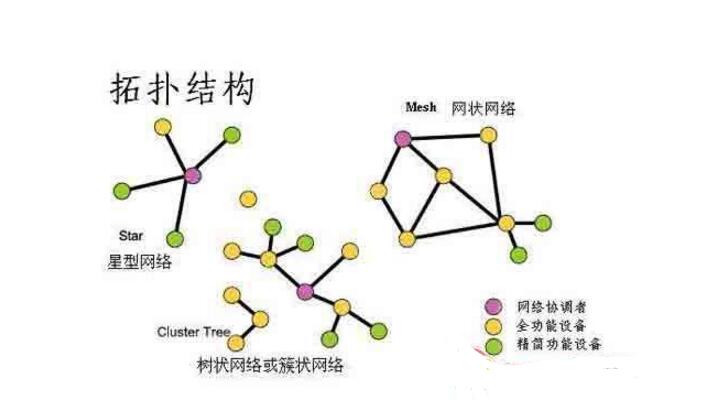

星型結(jié)構(gòu)拓?fù)涞?b class='flag-5'>優(yōu)缺點(diǎn)有哪些?

開關(guān)電源拓?fù)?b class='flag-5'>結(jié)構(gòu)優(yōu)缺點(diǎn)

總線型拓?fù)?b class='flag-5'>結(jié)構(gòu)優(yōu)缺點(diǎn)是什么

RISC結(jié)構(gòu)及優(yōu)缺點(diǎn)

RISC結(jié)構(gòu)及優(yōu)缺點(diǎn)

評論