現代高級雷達系統正在受到多方面的挑戰——頻率分配上的最新變化導致許多雷達系統的工作頻率非常接近通信基礎設施和其他頻譜要求極高的系統。

未來,頻譜擁塞狀況預期會更嚴重問題將惡化到雷達系統需要在運行時進行調整以適應環境和運行要求,這使得雷達系統需要向認知化和數字化發展。

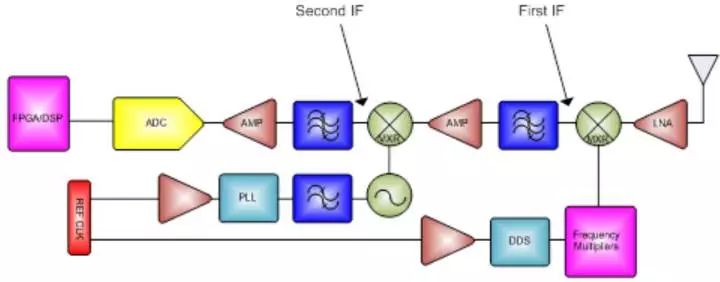

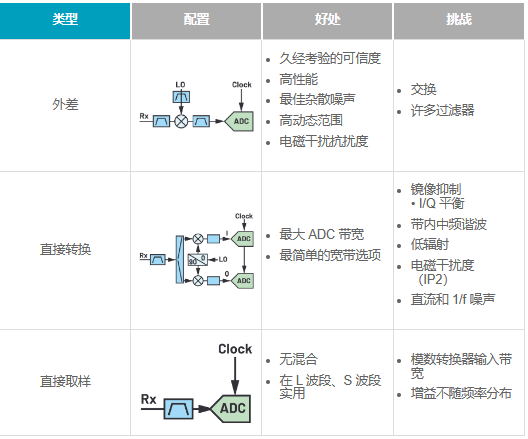

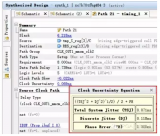

更多數字信號處理的需求推動雷達信號鏈要盡早向數字化過渡,使得ADC更靠近天線,這進而又會帶來若干具挑戰性的系統層面難題。為了更深入地討論這個問題,圖1顯示了目前典型的X波段雷達系統的高層次概略圖。該系統通常使用兩個模擬混頻級。第一級將脈沖式雷達回波混頻至約1 GHz頻率,第二級混頻至100至200 MHz的中頻(IF),以便能夠利用200 MSPS或更低的模數轉換器對信號進行12位或更高分辨率的采樣。

圖1. 使用第一和第二中頻(IF)的雷達接收機架構示例

在該架構中,頻率捷變和脈沖壓縮等功能可在模擬域中實現,這可能需要對信號處理進行一些更改和調整,但大體而言,系統功能受限于數字化速率。應當注意,即使以200 MSPS的數據速率進行采樣,雷達處理也能向前跨進一大步,但我們正在向新的階段突破,步子必須再邁大一點,實現全數字化雷達。

挑戰

近年來,每秒千兆采樣(GSPS) ADC已將系統中的數字化點推進到第一混頻級之后,使得數字化轉變更接近天線。模擬帶寬超過1.5 GHz的GSPS轉換器已然能夠支持第一中頻的數字化,但在許多情況下,當前GSPSADC的性能限制了這種解決方案的接受程度,因為器件的線性度和噪聲頻譜密度不滿足系統要求。

另外,高速ADC與數字信號處理平臺(通常是FPGA)之間的數據移動,直到最近還是以并行低壓差分信號(LVDS)接口為主要途徑。然而,使用LVDS數據總線從轉換器輸出數據會帶來一些技術難題,因為單條LVDS總線所需的工作速率將遠遠超過IEEE標準的最大速率以及FPGA的處理能力。為了解決這個問題,輸出數據需要解復用到兩條或(更一般地)四條LVDS總線,以便降低每條總線的數據速率。

例如,采樣速率超過2 GSPS的10位ADC通常將需要對輸出進行4倍解復用,LVDS總線寬度將達40位。而許多雷達系統,尤其是相控陣,會采用多個GSPS ADC,如此多的通道需要布線和長度匹配,硬件開發很快就會變得無法管理,更不用說互連所需的FPGA引腳數量!

新型GSPS ADC不僅能克服現有挑戰,而且可進一步優化系統。為使數字化更接近天線,此類轉換器提供無與倫比的線性度和3 GHz以上的模擬帶寬,支持L波段和大部分S波段的欠采樣。這樣,在這些波段內就可以直接進行RF采樣,而無需混頻器級,器件數量和系統尺寸得以縮減。更高頻率的系統也能使用更高中頻,從而可以減少混頻級和濾波器的數量,并且由于能夠使用寬范圍的中頻,頻率規劃選項得以增加。

更高的線性度和更低的噪聲頻譜密度使此類新器件能夠用于下一代雷達系統。隨著頻譜密度提高,必須提供更高的動態范圍才能管理雷達回波頻率附近的阻塞或干擾信號。

最新的GSPS ADC能夠提供75 dBc以上的SFDR,比最近十年面市的器件高出近20 dBc。與新近的通信基礎設施頻率分配相競爭時,這一跨越式進步顯得更加重要。

解決方案

模擬帶寬、線性度和噪聲方面的改善可以被看作是器件制造商的下一步邏輯發展。不過,新型GSPS ADC的兩個新增特性可為系統設計師帶來更大的便利,有可能會提高這些器件在未來系統中的接受程度:

JESD204B數據鏈路接口;

轉換器中嵌入的DSP功能,這對系統設計師非常有利,并且可以節省功耗。

JESD204B數據鏈路接口優勢

若干高速ADC最近已引入JESD204B數據鏈路,但它對GSPS轉換器最有好處,因為LVDS接口已很難滿足系統需求。JESD204B是一種高速串行標準,支持利用更少數量的差分互連(FPGA引腳)實現高速ADC與FPGA或其他處理器之間的數據傳輸。它是一種開銷非常低的協議,基于8b10b編碼方案,支持高達12.5 Gbps的波特率。

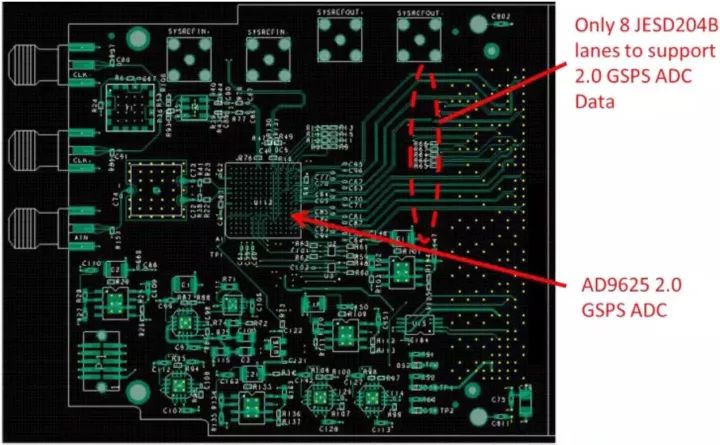

下面以ADI的新型2.0 GSPS、12位轉換器AD9625為例來討論其優勢。該轉換器的輸出數據速率是24 Gbps。假設LVDS數據總線的最高速率是1Gbps,并且忽略數據包裝問題,那么將需要24個LVDS對才能支持此接口,硬件布線時,所有對的PCB走線長度都需要匹配。若采用最大波特率為6.25 Gbps的JESD204B,則只需要6條JESD204B鏈路就能支持此轉換器的輸出。圖2清楚顯示了其優勢,AD9625與FPGA之間僅需布設8條JESD204B通道即可支持全數據速率2.0 GSPS。

圖2. 采用JESD204B的GSPS FPGA夾層卡(FMC) PCB布線

此外,當使用多條JESD204B通道時,PCB走線長度匹配的要求大幅放松,因為標準僅要求通道間對齊精度達到920 ps,各JESD204B通道的路徑延遲允許存在較大的差異。JESD204標準的最新“B”版還支持確定性延遲,可以計算離開高速ADC的數據與到達FPGA的數據之間的延遲。如果該延遲時間可以確定,那么就可以在數字后處理中予以補償,使數據流重新對齊并同步,這是采用GSPS轉換器的相控陣和波束成形系統的關鍵要求。

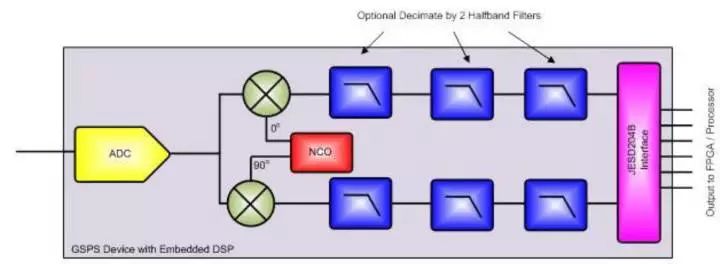

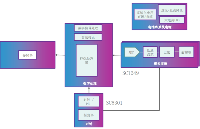

JESD204B對硬件設計師特別有利,但新型高速ADC的最大好處可能是增加了數字信號處理。AD9625等新一代GSPS轉換器基于65 nm或更小幾何尺寸的CMOS工藝,能夠以非常高的數據速率支持各種各樣的數字信號處理。近期而言,高速ADC將嵌入運行時可選的數字降頻轉換器(DDC),如圖3所示。

轉換器中嵌入的DSP功能

雷達波形帶寬因應用不同而有很大差異,例如,某些合成孔徑成像雷達波形需要數百MHz的帶寬,而跟蹤雷達使用的波形帶寬可能只有數十MHz或更少。過去,若GSPSADC更靠近天線,則意味著在某些情況下會有大量不需要的帶寬被傳輸到FPGA或處理器。在現代FPGA和高速ADC中,如果不是大部分,也有相當一部分功耗與器件的接口相關,因此,毫無用處地傳輸大量不需要的帶寬會提高系統功耗。在未來的多模式雷達中,動態使能DDC的能力將是一大優勢,可減輕FPGA的復雜處理負荷。

圖3. 帶嵌入式DSP的新型GSPS ADCMS-2670

DDC集數字數控振蕩器(NCO)和抽取濾波器于一體,能夠在高速ADC的奈奎斯特頻段內選擇信號帶寬和信號位置,僅將需要的適當數據傳輸給信號處理器件。例如,考慮一個在800 MHz的中頻使用30 MHz帶寬波形的雷達。如果用一個ADC以2.0 GSPS的采樣速率進行12位分辨率的采樣,則數據輸出帶寬將是1000 MHz,遠遠超過信號帶寬,轉換器的輸出數據速率將達3.0 GB/s。如果利用DDC以16倍的比率抽取數據,則不僅能進一步降低噪聲,而且輸出數據速率降至625 MB/s以下,這樣只需使用一條JESD204B通道就能傳輸數據。整體系統的功耗需求將因此而大幅降低。由于可根據需要動態配置DDC或予以旁路,新型高速ADC可在不同模式之間切換,以便支持針對功耗和機具進行優化的解決方案,并且幫助實現認知式雷達應用所需的特性集合。

結論

AD9625等新型GSPS ADC為雷達系統架構師提供了多種重要的選項,其模擬帶寬和采樣速率有助于減少器件數量或進行直接RF采樣。JESD204B接口和嵌入式DSP選項使得設計師獲取這些優勢再也不需要付出提高功耗和板復雜度的代價。動態配置高速ADC的能力可實現多功能支持,滿足創建全數字式認知雷達系統的需求。

-

adc

+關注

關注

98文章

6430瀏覽量

544084 -

數字信號處理

+關注

關注

15文章

556瀏覽量

45795 -

數字化

+關注

關注

8文章

8606瀏覽量

61638 -

雷達系統

+關注

關注

6文章

243瀏覽量

28643

原文標題:GSPS ADC擔綱,兩大特性定制雷達系統“瘦身計劃”

文章出處:【微信號:ZGDZGCS,微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DC–DC 轉換器為 GSPS ADC 提供高效輸電網絡

AD9690BCPZ-500 14位 1 GSPS模數轉換器(ADC)

探究寬帶GSPS模數轉換器(ADC)

DC–DC轉換器為GSPS ADC提供高效輸電網絡

GSPS ADC搭配DC-DC轉換器,提高輸電網絡效能

通過輸電網絡合探討GSPS ADC性能

TIDA-00479 GSPS ADC的最理想時鐘源參考設計

ADC12DJ3200AAV 射頻采樣模數轉換器 TI品牌 特性與應用

具備緩沖輸入的12位1GSPS ADC(TI)

考慮射頻系統中的GSPS ADC

ADC12D1x00RF 12位、3.2 GSPS和2 GSPS RF采樣ADC數據表

GSPS ADC擔綱,兩大特性定制雷達系統“瘦身計劃”

GSPS ADC擔綱,兩大特性定制雷達系統“瘦身計劃”

評論