I2C作為常用的通訊外設,廣泛應用在各種通訊場合,而且也衍生各種變體協議,比如SCCB,SMbus,PMbus等等。先楫半導體在I2C這個通訊外設上,每個傳輸的階段都可以獨立自由去控制,這也極大得提高了開發的自由靈活度,而且也可以隨性發揮生成I2C的變體協議,而不需要去進行IO模擬。

首先介紹一下先楫半導體I2C的一些主要特性和功能,方便后續說明,大家也可以到官網參考先楫用戶手冊。

1

I2C 特征

支持標準模式 (100Kb/s),快速模式 (400Kb/s) 和快速模式 +(1Mb/s)

可配置主從模式

支持 7 位和 10 位地址模式

支持廣播呼叫地址 (general call address)

自動時鐘延展 (clock stretching)

可配置的時鐘/數據時序

支持直接內存訪問 (DMA)

4 字節 FIFO

2

I2C 功能

每個傳輸由 4 個階段組成:起始,地址,數據和結束。在起始階段會產生 START 操作,在地址階段發送地址,在數據階段 1 個或多個數據字節被傳送,在結束階段產生 STOP 操作。每個階段都能夠獨立控制是否執行

4個字節FIFO,可不使用DMA的情況下,滿足多字節一次性傳輸。并且軟件沒有準備好下一個字節的收發數據或者FIFO已滿時候,I2C控制器會自動延展I2C總線時鐘來暫停總線傳輸。

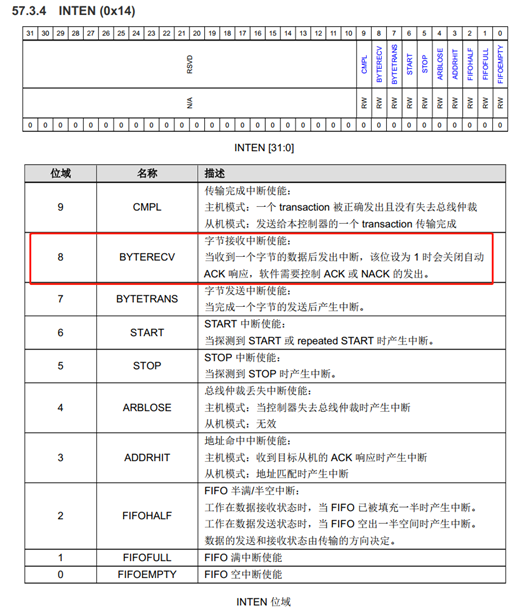

I2C控制器默認使能了自動ACK響應,即是除了最后一個字節外其余字節接收后都會自動發出ACK,軟件可以使能字節接收中斷來禁止自動響應功能,軟件自己接收后決定是否發送ACK。

3

場合需求

在某些場合,當I2C作為主機的時候,一次數據量傳輸當中,可能會有以下的需求方式:

傳輸過程中間變化讀寫方向,比如START操作到第一個數據字節傳輸是寫,后面變為讀。或者讀變成寫。

傳輸過程中分三次傳輸,START,數據,STOP傳輸。比如第一次傳輸需要帶START,但不需要STOP。

傳輸過程中需要restart重新發送start信號。

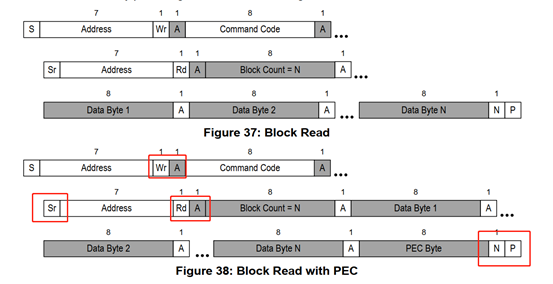

舉例,比如SMBUS,在進行block read傳輸中,就需要傳輸過程中發送restart信號,并且切換讀寫方向。

4

實現方式

先楫半導體的用戶手冊對于 I2C 的寄存器說明一共有好幾個,本文重點介紹以下三個密切相關的寄存器:

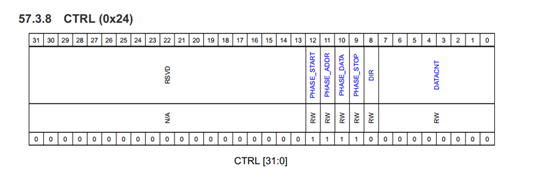

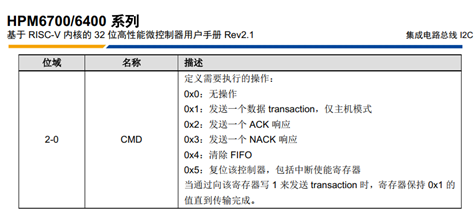

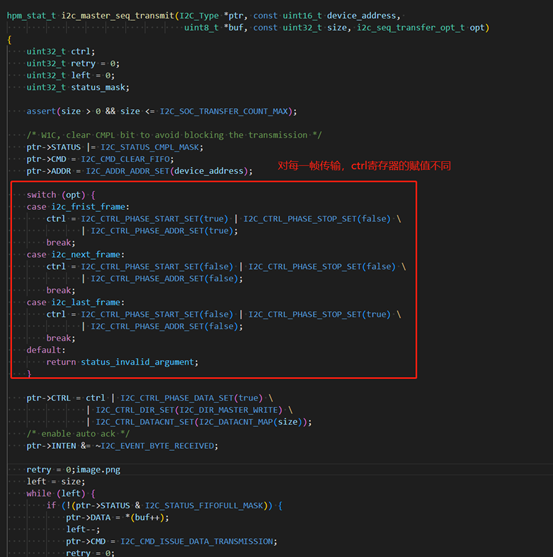

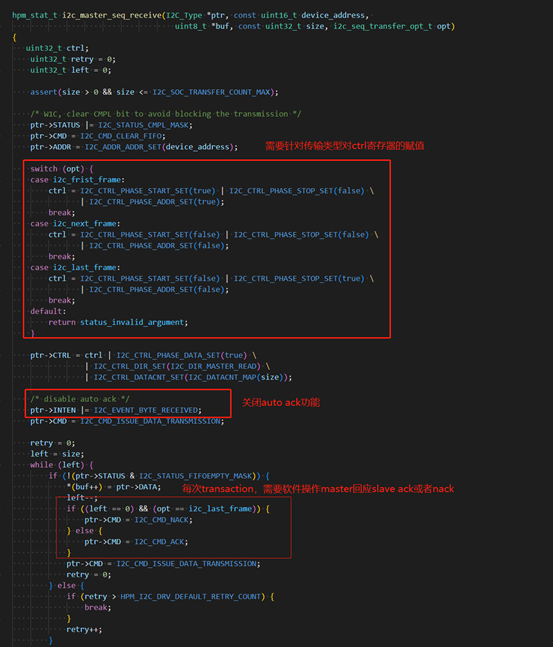

1. CTRL寄存器:該寄存器是用來配置一次傳輸中的每個階段的控制,比如主機模式下,方向是發送,在START開始后,STOP結束前,傳輸的是數據段,可以不發START,地址,STOP。那么可以對其寄存器的對應位進行開啟和關閉。

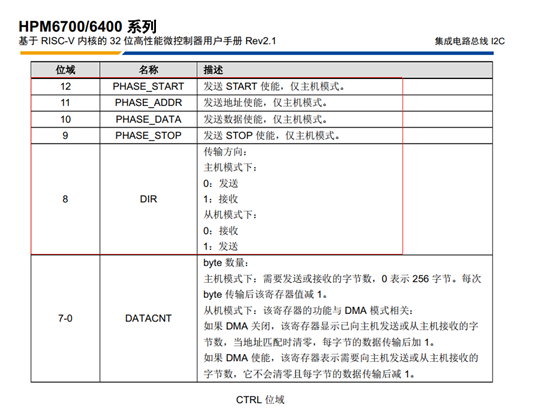

2. INTEN寄存器的BYTERECV位,開啟或關閉自動響應功能。

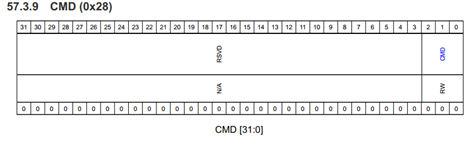

3. CMD寄存器:定義的是對一次transaction的相關操作。比如主機在接收到從機的數據,需要不接受數據了,可以發送一個NACK響應。前提是關閉了自動響應功能。

根據以上的寄存器說明,在新的sdk版本V1.2.0中,我們在SDK的i2c driver中看到有定義一個順序傳輸接口,定義一個枚舉,分別表示第一幀,中間幀,最后一幀。

/**

* @brief I2c sequentialtransfer options

* @arg: i2c_frist_frame: hasstart signal

* @arg: i2c_next_frame:middle transfer

* @arg: i2c_last_frame: hasstop signal

*/

typedef enum i2c_seq_transfer_opt{

i2c_frist_frame = 0,

i2c_next_frame,

i2c_last_frame,

}i2c_seq_transfer_opt_t;

對于發送接口,sdk1.2也提供了i2c_master_seq_transimit 這個 API。

對于接收接口,sdk1.2也提供了i2c_master_seq_receive這個API,從內部API可以看出是關閉自動響應,軟件控制一次傳輸的ACK和NACK,避免STOP未出現時出現數據斷開。

5

驗證功能

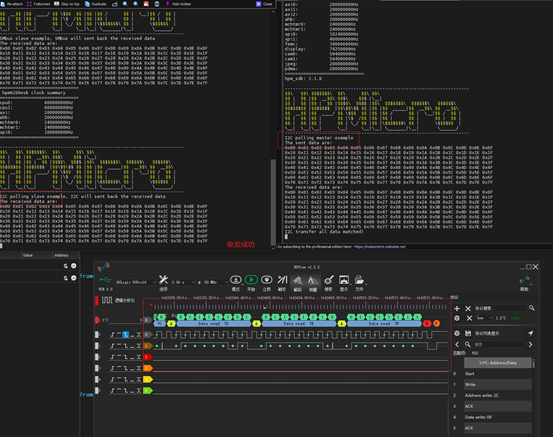

根據以上信息,我們來操作一個實驗,以sdk的poll例子的master和slave兩個開發板進行相互收發,slave不做改動,master的讀寫接口替換以上的接口。

int main(void)

{

hpm_stat_t stat;

i2c_config_t config;

uint32_t freq;

board_init();

init_i2c_pins(TEST_I2C);

config.i2c_mode = i2c_mode_normal;

config.is_10bit_addressing = false;

freq = clock_get_frequency(TEST_I2C_CLOCK_NAME);

stat = i2c_init_master(TEST_I2C, freq, &config);

if (stat != status_success) {

return stat;

}

printf("I2C polling master example\n");

prepare_tx_data();

uint32_t index = 0;

uint32_t inc_len = 30;

if (status_success != i2c_master_seq_transmit(TEST_I2C, TEST_I2C_SLAVE_ADDRESS, &tx_buff[index], inc_len, i2c_frist_frame)) {

printf("Master transfer frist frame failed\n");

while (1) {

}

}

index += inc_len;

if (status_success != i2c_master_seq_transmit(TEST_I2C, TEST_I2C_SLAVE_ADDRESS, &tx_buff[index], inc_len, i2c_next_frame)) {

printf("Master transfer next frame failed\n");

while (1) {

}

}

index += inc_len;

inc_len = (sizeof(tx_buff) - (inc_len * 2));

if (status_success != i2c_master_seq_transmit(TEST_I2C, TEST_I2C_SLAVE_ADDRESS, &tx_buff[index], inc_len, i2c_last_frame)) {

printf("Master transfer last frame failed\n");

while (1) {

}

}

/* wait for slave controller to be ready to send data */

board_delay_ms(100);

index = 0;

inc_len = 30;

if (status_success != i2c_master_seq_receive(TEST_I2C, TEST_I2C_SLAVE_ADDRESS, &rx_buff[index], inc_len, i2c_frist_frame)) {

printf("Master transfer read frist framefailed\n");

while (1) {

}

}

index += inc_len;

if (status_success != i2c_master_seq_receive(TEST_I2C, TEST_I2C_SLAVE_ADDRESS, &rx_buff[index], inc_len, i2c_next_frame)) {

printf("Master transfer read next framefailed\n");

while (1) {

}

}

index += inc_len;

inc_len = (sizeof(tx_buff) - (inc_len * 2));

if (status_success != i2c_master_seq_receive(TEST_I2C, TEST_I2C_SLAVE_ADDRESS, &rx_buff[index], inc_len, i2c_last_frame)) {

printf("Master transfer read last framefailed\n");

while (1) {

}

}

check_transfer_data();

while (1) {

}

return 0;

}

實驗現象

①當把一次完整傳輸拆分三次frame傳輸時候,依舊是沒什么問題的。可見以上的功能使用并沒有什么問題。

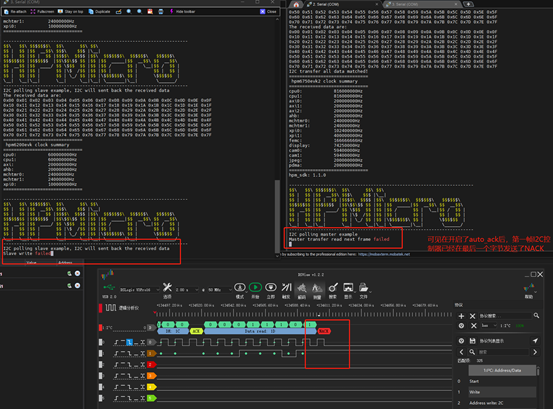

② 可以模擬下一個配置錯誤的現象,開啟auto-ack功能,master接收slave數據的數據,由于開啟了自動響應,在第一包frame接收的時候,I2C控制器認為傳輸到最后一個字節,會自動補充NACK,但我們并不希望補充NACK,因為一次完整的傳輸還沒完成,這時候就需要軟件自己添加ACK或者NACK。

6

小 結

對于I2C,無論是poll方式,還是中斷方式,還是DMA方式,先楫的I2C控制器對于I2C傳輸的每個階段都是可控的,這為開發者的應用需求也極大提高軟件靈活度。

-

總線

+關注

關注

10文章

2869瀏覽量

87995 -

I2C

+關注

關注

28文章

1482瀏覽量

123348

發布評論請先 登錄

相關推薦

I2C總線為什么要接上拉電阻

I2C總線上拉電阻的必要性

簡單認識I2C通信協議

I2C總線協議的工作原理和尋址格式

什么是I2C協議 I2C總線的控制邏輯

什么是I2C接口?什么是I3C接口?I2C與I3C的區別

I2C總線的一種靈活控制方法

I2C總線的一種靈活控制方法

評論