01

FSMC特點

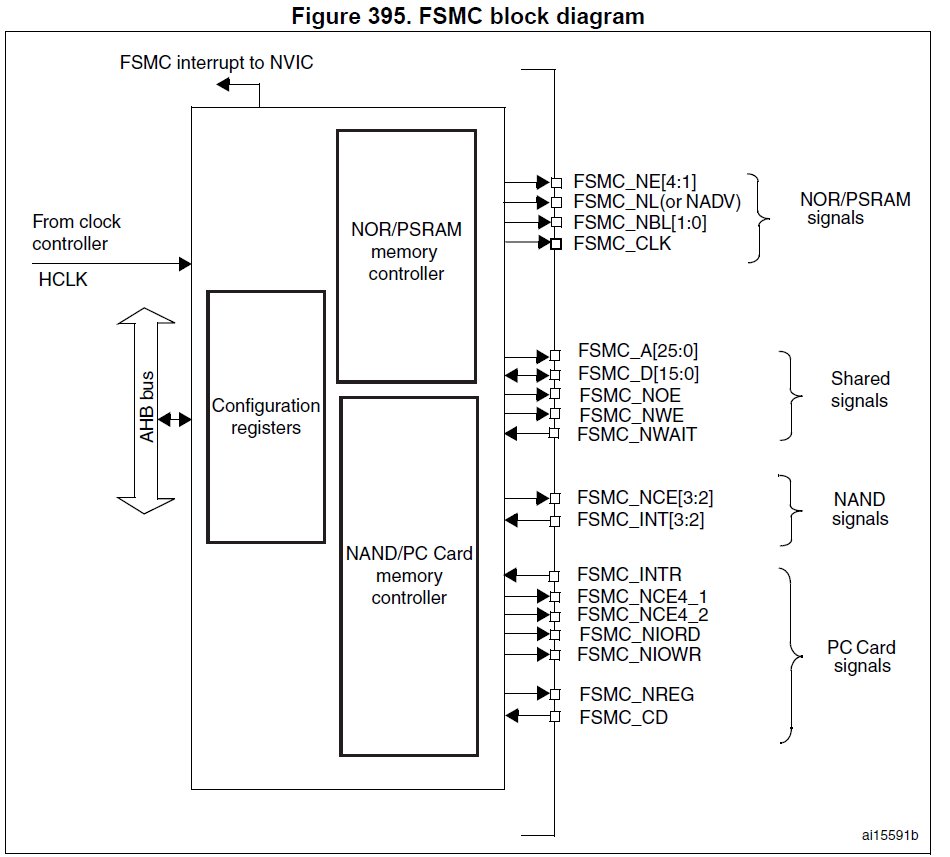

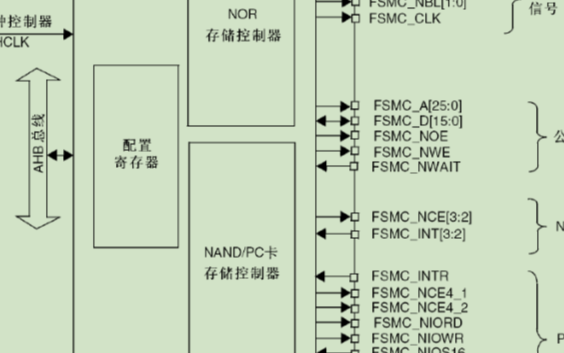

Flexible static memory controller(FSMC)靈活的靜態(tài)存儲控制器。FSMC可以連接異步或同步存儲器或16位PC存儲卡,主要用途有:

- 將 AHB 數(shù)據(jù)通信事務(wù)轉(zhuǎn)換為適當(dāng)?shù)耐獠科骷f(xié)議

- 滿足外部器件的訪問時序要求

所有外部存儲器共享地址、數(shù)據(jù)和控制信號,但有各自的片選信號。FSMC 一次只能訪問一個外部器件。

FSMC,即靈活的靜態(tài)存儲控制器,能夠與同步或異步存儲器和16位PC存儲器卡連接,STM32的FSMC接口支持包括SRAM、NANDFLASH、NORFLASH和PSRAM等存儲器。

△FSMC框圖示意

02

AHB接口

AHB設(shè)備接口可以使內(nèi)部CPU和其他主總線外設(shè)去訪問外部存儲器。AHB事務(wù)可以傳輸外部設(shè)備協(xié)議。特別是當(dāng)外部存儲器被選擇位8位或16位,32位的AHB傳輸傳輸事務(wù)會被劃分為多個連續(xù)的8位或16的傳輸事務(wù)。片選會在每次訪問時切換。

通用事務(wù)規(guī)則要求AHB傳輸數(shù)據(jù)寬度必須是8位、16位或32位。但是訪問外部數(shù)據(jù)必須有個固定的數(shù)據(jù)寬度。這可能導(dǎo)致不一樣的傳輸。

因此必須遵循一些簡單的事務(wù)規(guī)則:

- AHB事務(wù)數(shù)據(jù)寬度必須和存儲器數(shù)據(jù)寬度相同。在這種情況下不會出問題;

- AHB事務(wù)數(shù)據(jù)寬度大于存儲器數(shù)據(jù)寬度,在這種情況下,F(xiàn)SMC會將AHB事務(wù)分為多個連續(xù)的存儲器訪問,這樣符合外部存儲器訪問數(shù)據(jù)寬度;

- AHB事務(wù)數(shù)據(jù)小存儲器寬度,在這種情況下,異步傳輸可能一致,也可能不一致,這取決于外部設(shè)備的類型。

對設(shè)備的異步訪問要具有字節(jié)選擇功能(SRAM,ROM,PSRAM),①FSMC 允許寫入事務(wù)通過其字節(jié)選擇通道 NBL[1:0] 訪問恰當(dāng)?shù)臄?shù)據(jù),②允許讀取事務(wù)。會讀取所有存儲器字節(jié),并將丟棄無用的存儲器字節(jié)。 NBL[1:0]在讀取事務(wù)期間保持為低電平。

對不具有字節(jié)選擇功能的器件( 16 位 NOR 和 NAND Flash)進(jìn)行異步訪問,當(dāng)請求對 16 位寬的 Flash 存儲器進(jìn)行字節(jié)訪問時會發(fā)生此情形。

顯然,不能在字節(jié)模式下訪問此器件(只能針對 Flash 存儲器讀取或?qū)懭?16 位字),因此①不允許寫入事務(wù),②允許讀取事務(wù)。會讀取所有存儲器字節(jié),并將丟棄無用的存儲器字節(jié)。 NBL[1:0]在讀取事務(wù)期間保持低電平。

03

外部設(shè)備地址映射

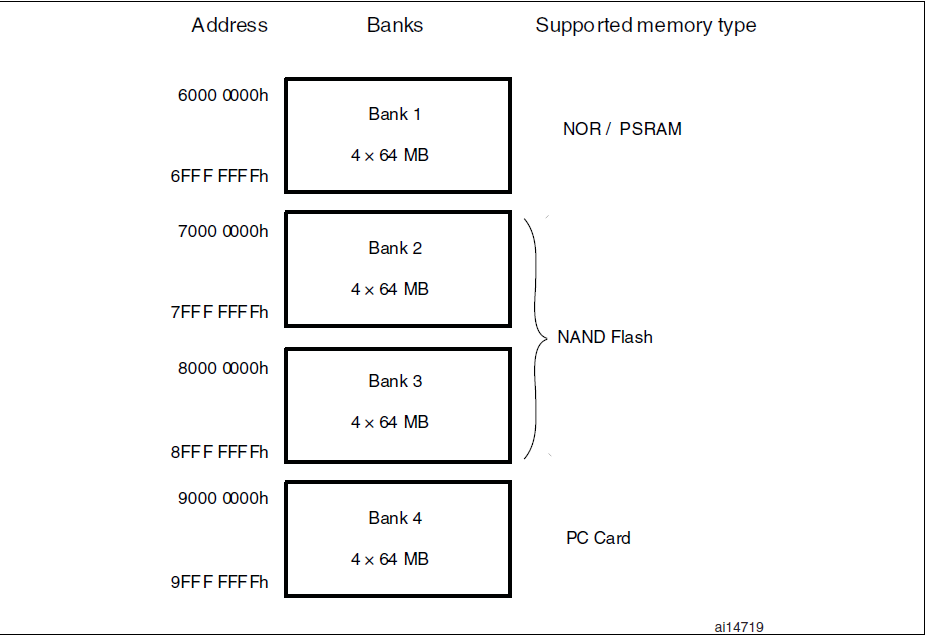

FSMC的外部設(shè)備地址映像,STM32的FSMC將外部存儲器劃分為固定大小為256M字節(jié)的四個存儲塊:

- 塊1被用于4個NORflash或者PSRAM內(nèi)存設(shè)備。塊1被劃分為4塊NORflash/PSRAM帶有獨立的片選信號。

- 塊2和塊3用于連接NANDflash(一個塊驅(qū)動一個設(shè)備)

- 塊4用于連接PC塊設(shè)備

對于每個存儲區(qū)域,所要使用的存儲器類型由用戶在配置寄存器中定義

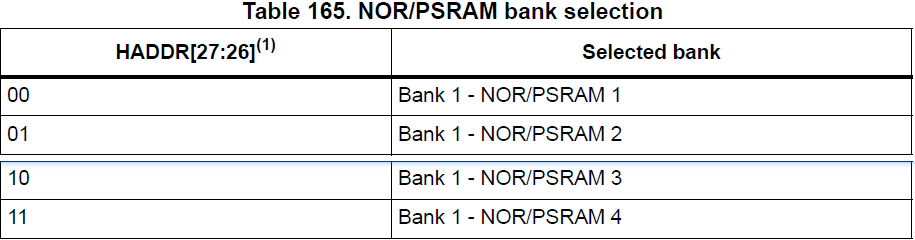

NOR/PSRAM地址映射

Bank1的256M字節(jié)空間由28根地址線(HADDR[27:0])尋址。這里HADDR,是內(nèi)部AHB地址總線,但也會參與對外部存儲器的尋址,其中,HADDR[25:0]來自外部存儲器地址FSMC_A[25:0],而HADDR[26:27]對4個區(qū)進(jìn)行尋址。如下表所示:

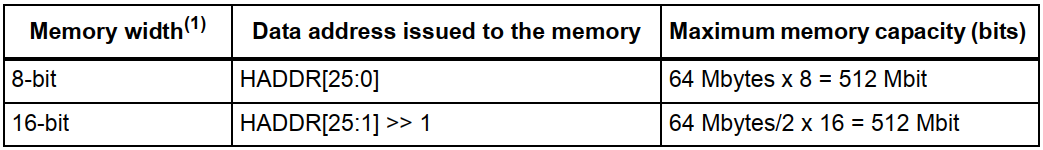

HADDR[25:0] 包含外部存儲器地址。由于HADDR為字節(jié)地址,而存儲器按字尋址,所以根據(jù)存儲器數(shù)據(jù)寬度不同,實際向存儲器發(fā)送的地址也將有所不同,如下表所示:

當(dāng)Bank1接的是16位寬度存儲器的時候:HADDR[25:1]->FSMC_A[24:0];

當(dāng)Bank1接的是8位寬度存儲器的時候:HADDR[25:0]->FSMC_A[25:0];

不論外部接8位/16位寬設(shè)備,F(xiàn)SMC_A[0]永遠(yuǎn)接在外部設(shè)備地址A[0]。

04

NOR/PSRAM控制器

FSMC 會生成適當(dāng)?shù)男盘枙r序,以驅(qū)動以下類型的存儲器

- 異步 SRAM 和 ROM,8位、16位或者32位

- PSRAM,異步模式,突發(fā)模式,復(fù)用或非復(fù)用

- NOR Flash,異步模式或突發(fā)模式,復(fù)用或非復(fù)用

FSMC每個塊輸出獨立的片選信號NE[4:1]。其他信號(讀,數(shù)據(jù)和控制)是共享的;

對于同步訪問,F(xiàn)SMC僅僅在讀寫事務(wù)時給選擇的外部設(shè)備發(fā)出時鐘。HCLK時鐘頻率是該時鐘的整數(shù)倍。每個塊的大小固定64M字節(jié)。

存儲器的可編程參數(shù)包括訪問時序(詳見下圖)和對等待管理的支持(用于在突發(fā)模式下訪問NOR Flash 和PSRAM)。

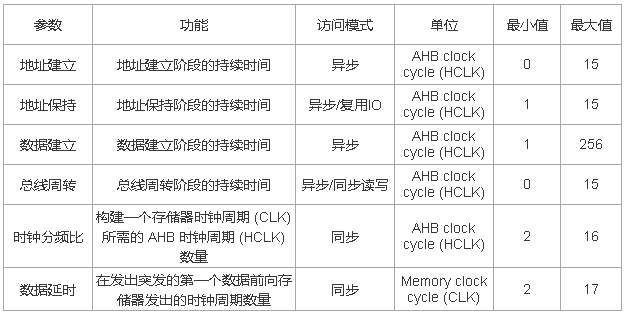

NOR/PSRAM 的可編程訪問參數(shù)

05

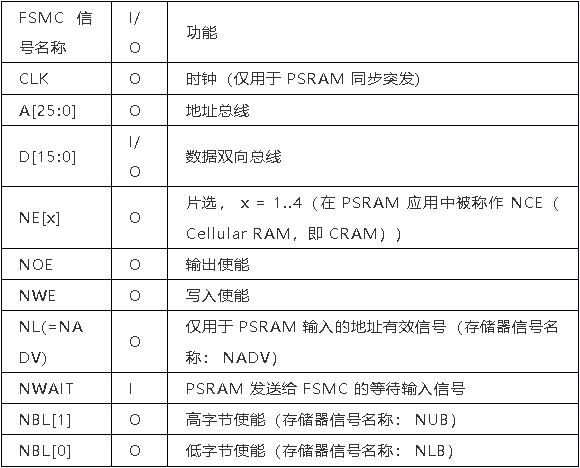

外部存儲器接口信號

非復(fù)用 I/OPSRAM/SRAM

注意:前綴“N”表示相關(guān)的信號為低電平有效

06

NOR/PSRAM控制器異步事務(wù)

異步靜態(tài)存儲器(NOR Flash、PSRAM、SRAM)

- 信號通過內(nèi)部時鐘 HCLK 進(jìn)行同步,不會將此時鐘發(fā)送到存儲器;

- FSMC 總是會先對數(shù)據(jù)進(jìn)行采樣,而后再禁止片選信號 NE。這樣可以確保符合存儲器數(shù)據(jù)保持時序的要求(數(shù)據(jù)轉(zhuǎn)換的芯片使能高電平,通常最低為 0 ns。);

- 如果使能擴展模式(FSMC_BCRx 寄存器中的 EXTMOD 位置 1),則最多可提供四種擴展模式( A、 B、 C 和 D)。可以混合使用 A、 B、 C 和 D 模式來進(jìn)行讀取和寫入操作。例如,可以在模式 A 下執(zhí)行讀取操作,而在模式 B 下執(zhí)行寫入操作;

- 如果禁用擴展模式(FSMC_BCRx 寄存器中的 EXTMOD 位復(fù)位),則 FSMC 可以在模式 1 或模式 2 下運行,如下所述①當(dāng)選擇 SRAM/CRAM 存儲器類型時,模式 1 為默認(rèn)模式( FSMC_BCRx 寄存器中MTYP = 0x0 或 0x01)②當(dāng)選擇 NOR 存儲器類型時,模式 2 為默認(rèn)模式( FSMC_BCRx 寄存器中 MTYP =0x10)

對于這5種模式,總結(jié)如下:

模式1/A:SRAM/PSRAM(CRAM)OE翻轉(zhuǎn),模式A與模式1的區(qū)別是NOE的變化和相互獨立的讀寫時序。

模式2/B:NOR閃存,模式2/B與模式1相比較,不同的是NADV的變化,且在擴展模式下(模式B)讀寫時序相互獨立。(只有當(dāng)設(shè)置了擴展模式時(模式B),F(xiàn)SMC_BWTRx才有效,否則該寄存器的內(nèi)容不起作用。)

模式C :NOR閃存- OE翻轉(zhuǎn),模式C與模式1不同的是,NOE和NADV的翻轉(zhuǎn)變化,以及獨立的讀寫時序;

模式D:帶地址擴展的異步操作,模式D與模式1不同的是NADV的翻轉(zhuǎn)變化,NOE的翻轉(zhuǎn)出現(xiàn)在NADV翻轉(zhuǎn)之后,并且具有獨立的讀寫時序。

07

模式1

模式 1 -SRAM/PSRAM (CRAM)

下圖顯示了所遵循的受支持模式的讀寫事務(wù)通過配置FSMC_BCRx, and FSMC_BTRx/FSMC_BWTRx寄存器

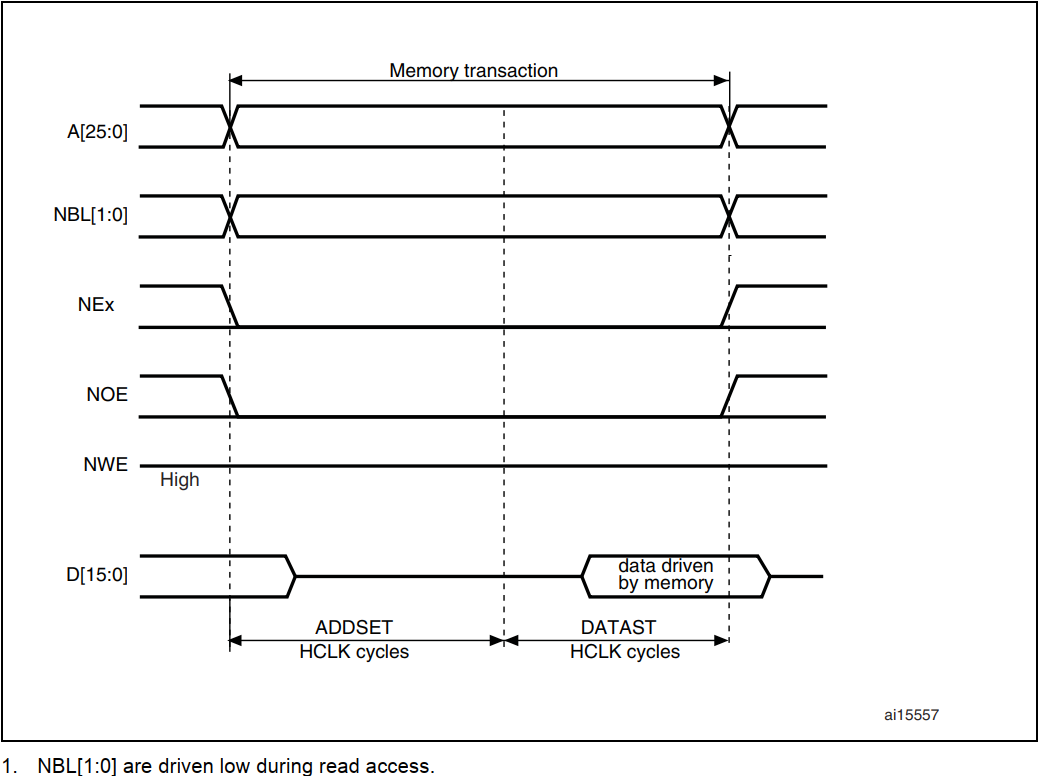

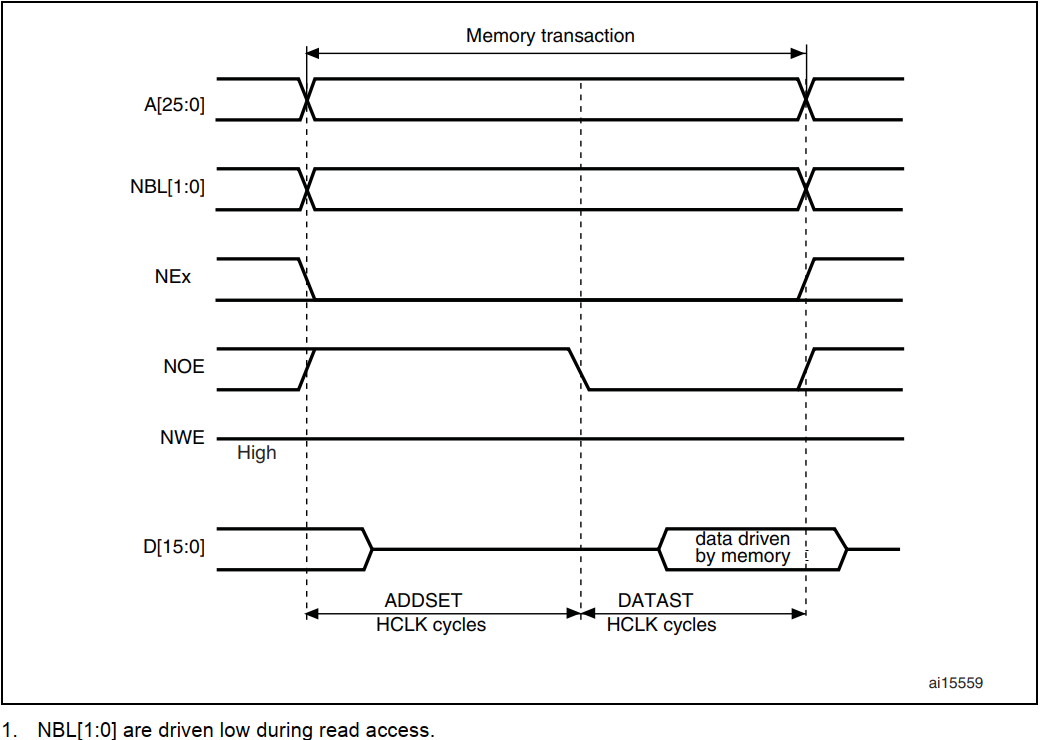

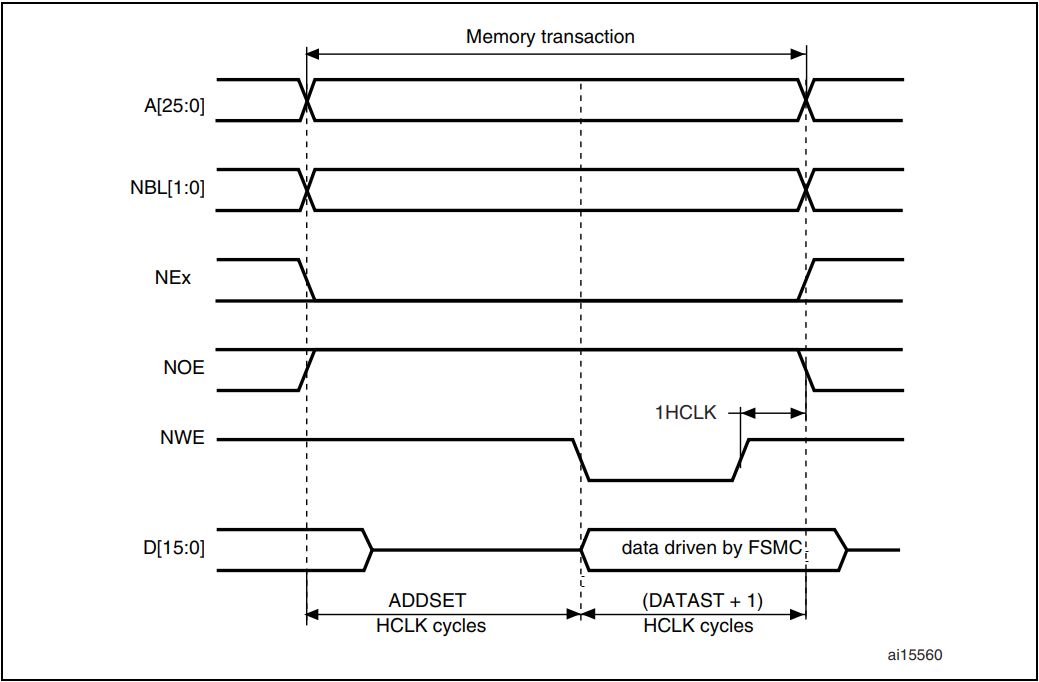

▽模式1讀訪問

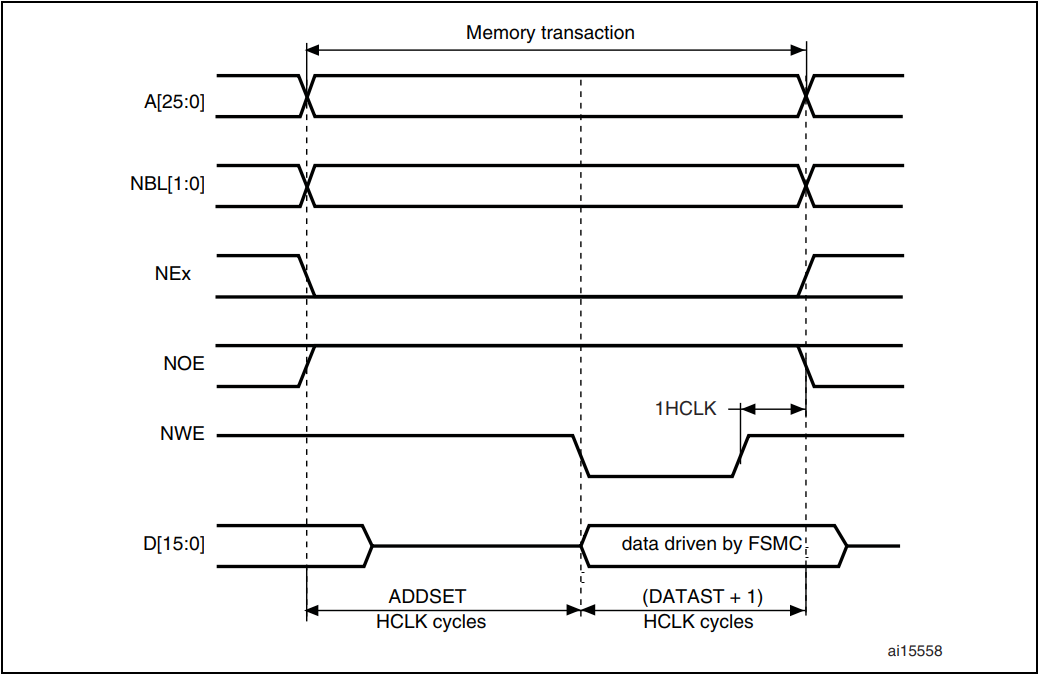

▽模式1寫訪問

位于寫入事務(wù)末尾的一個HCLK 周期有助于確保NWE 上升沿之后的地址和數(shù)據(jù)保持時間。由于存在此HCLK 周期,DATAST 值必須大于零(DATAST > 0)。

08

模式A

模式 A -SRAM/PSRAM (CRAM) OE 切換

▽模式A讀訪問

▽模式A寫訪問

與模式1的不同之處在于NOE 的切換與獨立的讀取和寫入時序

對于模式A,

ADDSET就是NWE的高電平時間,也就是地址建立時間

DATAST就是NWE的低電平時間,也就是數(shù)據(jù)保持時間

09

代碼說明

readWriteTiming.FSMC_AddressSetupTime = 0x02; //地址建立時間(ADDSET)為2個HCLK 2*1/120M=16ns

readWriteTiming.FSMC_AddressHoldTime = 0x02; //地址保持時間(ADDHLD),16ns

readWriteTiming.FSMC_DataSetupTime = 0x06; //數(shù)據(jù)建立時間,50ns

readWriteTiming.FSMC_BusTurnAroundDuration = 0x00;//總線恢復(fù)時間

readWriteTiming.FSMC_CLKDivision = 0x00;// 時鐘分頻因子

readWriteTiming.FSMC_DataLatency = 0x00;//數(shù)據(jù)產(chǎn)生時間

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; //模式A

FSMC_AddressSetupTime: 這些位定義地址的建立時間,適用于SRAM、ROM和異步總線復(fù)用模式的NOR閃存操作。

FSMC_AddressHoldTime : 這些位定義地址的保持時間,適用于SRAM、ROM和異步總線復(fù)用模式的NOR閃存操作。

FSMC_DataSetupTime: 這些位定義數(shù)據(jù)的保持時間,適用于SRAM、ROM和異步總線復(fù)用模式的NOR閃存操作。

F SMC_BusTurnAroundDuration: 這些位用于定義一次讀操作之后在總線上的延遲(僅適用于總線復(fù)用模式的NOR閃存操作),一次讀操作之后控制器需要在數(shù)據(jù)總線上為下次操作送出地址,這個延遲就是為了防止總線沖突。如果擴展的存儲器系統(tǒng)不包含總線復(fù)用模式的存儲器,或最慢的存儲器可以在6個HCLK時鐘周期內(nèi)將數(shù)據(jù)總線恢復(fù)到高阻狀態(tài),可以設(shè)置這個參數(shù)為其最小值。

FSMC_CLKDivision : 定義CLK時鐘輸出信號的周期,以HCLK周期數(shù)表示。

FSMC_DataLatency: 處于同步成組模式的NOR閃存,需要定義在讀取第一個數(shù)據(jù)之前等待的存儲器周期數(shù)目。這個時間參數(shù)不是以HCLK表示,而是以閃存時鐘(CLK)表示。在訪問異步NOR閃存、SRAM或ROM時,這個參數(shù)不起作用。操作CRAM時,這個參數(shù)必須為0

FSMC_AccessMode : 訪問模式

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1;// 這里我們使用NE1 ,也就對應(yīng)BTCR[6],[7]。

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;// 不復(fù)用數(shù)據(jù)地址

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;// FSMC_MemoryType_SRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_8b;//存儲器數(shù)據(jù)寬度為8bit

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;// 存儲器寫使能

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;// 讀寫使用相同的時序

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming;//讀寫時序

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming;//寫時序

FSMC_Bank: nor被分為四塊,其中這個參數(shù)是說明對那個塊編程

FSMC_DataAddressMux: 地址\\數(shù)據(jù)是否復(fù)用

FSMC_MemoryType: 存儲器類型

FSMC_MemoryDataWidth: 數(shù)據(jù)總線寬度8位/16位

FSMC_BurstAccessMode: 是否進(jìn)行成組模式訪問

FS MC_WaitSignalPolarity: 等待信號有效級性

FSMC_WrapMode: 該位決定控制器是否支持把非對齊的AHB成組操作分割成2次線性操作;該位僅在存儲器的成組模式下有效。

FSMC_WaitSignalActive: 當(dāng)閃存存儲器處于成組傳輸模式時,NWAIT信號指示從閃存存儲器出來的數(shù)據(jù)是否有效或是否需要插入等待周期。該位決定存儲器是在等待狀態(tài)之前的一個時鐘周期產(chǎn)生NWAIT信號,還是在等待狀態(tài)期間產(chǎn)生NWAIT信號。

FSMC_WriteOperation: 該位指示FSMC是否允許/禁止對存儲器的寫操作。

FSMC_WaitSignal: 當(dāng)閃存存儲器處于成組傳輸模式時,這一位允許/禁止通過NWAIT信號插入等待狀態(tài)。

FSMC_ExtendedMode:該位允許FSMC使用FSMC_BWTR寄存器,即允許讀和寫使用不同的時序。

FSMC_WriteBurst: 對于處于成組傳輸模式的閃存存儲器,這一位允許/禁止通過NWAIT信號插入等待狀態(tài)。讀操作的同步成組傳輸協(xié)議使能位是FSMC_BCRx寄存器的BURSTEN位。

FSMC_ReadWriteTimingStruct: 讀時序配置指針

FSMC_WriteTimingStruct: 寫時序配置指針

-

NAND

+關(guān)注

關(guān)注

16文章

1653瀏覽量

135731 -

SRAM控制器

+關(guān)注

關(guān)注

0文章

11瀏覽量

5880 -

AHB總線

+關(guān)注

關(guān)注

0文章

18瀏覽量

9441 -

FSMC模塊

+關(guān)注

關(guān)注

0文章

9瀏覽量

1915 -

存儲控制器

+關(guān)注

關(guān)注

0文章

23瀏覽量

9128

發(fā)布評論請先 登錄

相關(guān)推薦

STM32接口中FSMC/FMC難點問題理解

存儲控制器FSMC與觸摸屏介紹

STM32是如何驅(qū)動LCD的

STM32的CAN外設(shè)簡介

STM32的FSMC詳解

如何使用STM32的FSMC接口驅(qū)動LCD屏

最全STM32外設(shè)資料匯總

基于FPGA和STM32的FSMC通信

AN4761_通過STM32L476、486的FSMC外設(shè)驅(qū)動外部存儲器

QVGA TFT-LCD直接驅(qū)動使用STM32F10xx FSMC外設(shè)

TFT LCD與FSMC的硬件連接大容量STM32F10xxx FSMC接口

STM32的FSMC外設(shè)簡介

STM32的FSMC外設(shè)簡介

評論