1.0 概述

本文所用測例RFIC是一款自研射頻收發器芯片,工作于全球通用的ISM 2.400~2.525GHz頻段,126通道,集成了頻率綜合器,功率放大器,調制和解調模塊,還支持完整的數字鏈路層協議引擎,是真正單芯片的無線數據收發器。信道速率最高1Mbps,支持HOSTCPU下載更新內部微碼,實現鏈路層的靈活控制;最大工作電流20mA;發射功率控制范圍達33dBm,控制步長2dBm。芯片采用0.18μm RF CMOS 工藝,其中數字邏輯約2.5萬門。

為了獲取準確的功耗數據,采用了HSIM-VCS進行多模塊數模混合仿真。由于芯片劃分為模擬設計AFE和數字設計DLP兩大模塊,它們之間依靠大量的狀態控制信號和數據信號互聯,首先采用了HSIM-VCS進行全芯片數模混合功能仿真。為了獲得更快的Turn Around Time (TAT), 后引入XA-VCS進行全芯片功能仿真加速。

2.0 數模混合仿真

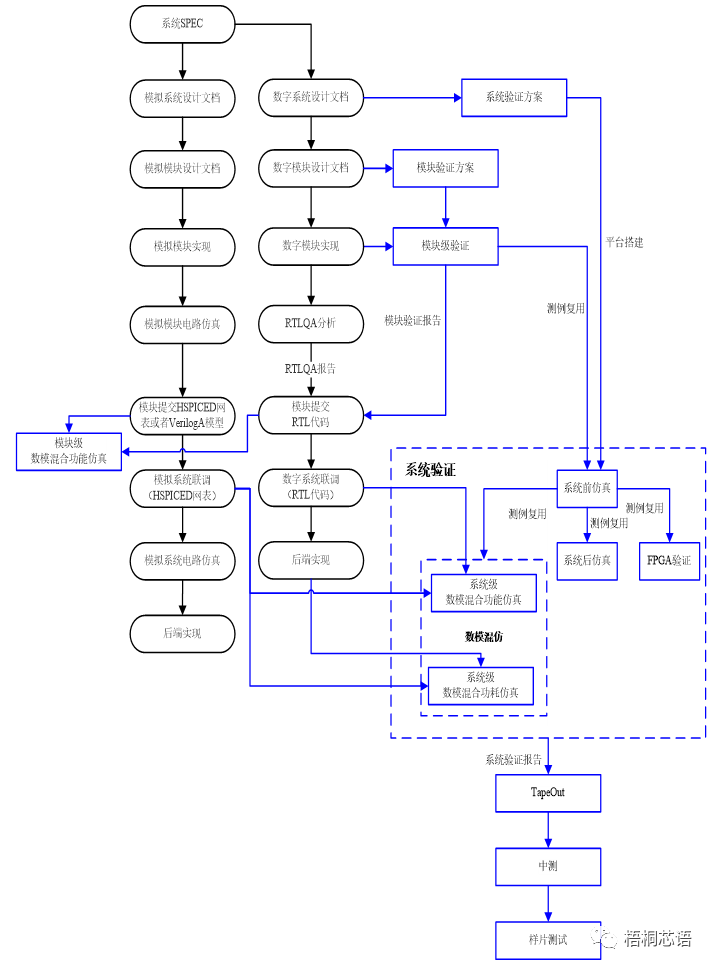

數模混合仿真的驗證對象是數模混合集成電路。數模混合集成電路的設計流程是比較復雜的。如圖1所示,該RFIC芯片不僅包括了單獨的數字和模擬設計流程(分別用于實現數字和模擬的功能模塊),在將數模電路混合時,也有其獨立的設計流程去驗證數模接口信號的正確性、數模混合后能否繼續正常工作,以及進行數模混合電路的物理設計等。

數模混合電路是對數字電路部分和模擬電路部分分別進行不同抽象層次的仿真、集成之后進行數模混合仿真。為了盡早發現設計Bug,有功能交互的模擬模塊和數字模塊在分別獨立驗證完畢之后,進行模塊級整合,分別提取Hspice網表和RTL代碼,進行混數模合仿真。

電路仿真的速度和精度是經典的trade-off,同時取決于仿真環境中使用的仿真器(軟件)和工作站環境(硬件)。為了加速仿真,本項目采用了“超級”Linux工作站:64G內存,584G硬盤,16核2.40GHz/6MB CPU。關于仿真器,將在后續兩章做較為詳細的介紹。

3.0 功耗仿真

數字邏輯電路的功耗分析手段較多。其中Synopsys公司的工具PrimeTime PX,可以通過已有的Liberty格式功耗模型,計算一段時間內電路翻轉發生的總能量,進一步得出該時間段內的平均功耗,但該方法對于分析電流瞬態變化以及上電過程中的動態電流變化有很大的限制。雖然利用HSPICE等高精度Spice仿真器進行仿真可以得到最精確的結果,但對于數字邏輯這種“巨大”規模(百萬門級)的電路來說,幾乎根本無法進行。

Synopsys公司的HSIM工具,是一款廣泛采用的Fast Spice仿真工具,利用該工具可以對大規模的電路做Spice級電路仿真,在精度和速度接受的情況下取得比較接近于實際的動態電流曲線,同時可以仿真出芯片在上電(Power Up)過程中,電源上電順序對數字電路功能以及電流的影響。通過VPI或DKI接口將HSIM和VCS連接起來,更可以直接使用在數字驗證中所使用的激勵(TestBench)形成對HSIM Spice仿真的輸入激勵,實現數字激勵和SPICE級設計的動態數模混合仿真。我們采用了VPI的HSIM-VCS數模混合驗證方法。

圖1項目設計流程圖

3.1 目標

對于該RFIC芯片,使用HSIM-VCS進行數模混合仿真,主要是有以下分析目標:

?在上電過程中(從外部電源上電到數字電路上電復位信號釋放的過程)電流峰值是否滿足設計要求(小于10mA)

?當數字電路的上電復位信號釋放時,系統工作電壓是否能保證數字邏輯處于正常工作狀態

?數字電路工作時,工作電壓是否能夠保證其正常的工作

3.2 環境

3.2.1 EDA工具以及工作站環境

Spice仿真器: HSIM 2008.03 64bit

Verilog仿真器: VCS 2006.06-SP2 64bit

服務器型號: IBM3850M2Server

系統平臺: Linux RHEL v4 64bit

需要注意的是,利用VPI作為接口進行HSIM-VCS的仿真,HSIM和VCS的版本必須一一對應。

3.2.2 Spice級數字電路網表的準備

數字電路網表來自于自動布局布線工具輸出的Verilog格式網表,但該網表是不能夠直接用于Spice級仿真的,因此需要將網表轉換成可以用Spice仿真工具進行仿真的格式。

Verilog轉換成CDL

一般說來,需要將Verilog格式的網表轉換成Spice仿真工具可以識別的CDL網表,HSIM自帶的v2s工具,可以用來完成這個工作。下面描述的是一個將Verilog格式網表abc.cdl轉換成abc.cdl的腳本,直接運行就可以完成轉換:

上面的腳本里,“-bn0”表示如果是Bus信號,則使用方括號[]來描述分離的信號名,如A[0]、A[1]等。“-const 00”表示電路中常數0表示0V,同理“-const11.8”表示常數1為1.8V。“-global_const0”以及“-global_const1”指定了全局變量中電源和地的網絡名,這會使產生的CDL網表中加上“.global vdd vss”命令。“-o”指定輸出的CDL文件。

“-s”指定了電路中某些IP的spice級網表文件,轉換工具會根據IP網表中端口的順序進行轉換。但需要注意,Bus信號順序則不會根據網表內的順序進行轉換,而是根據Verilog格式中定義的順序進行轉換。如下所示,某個IP在Verilog格式網表中的例化方式中,busd是由高到低的:

那么產生的CDL網表中,例化的順序就是由高到低。

XInstanceName netc neta netb bus[2] bus[1] bus[0] ReferenceName

而這與IP的Spice級網表定義的順序不一定一致。這種情況往往發生在RAM、ROM等Bus信號較多的模塊上,因此在轉換完成后,建議對于IP的接口進行進一步的檢查以及修正,特別是存儲單元的接口。

一般說來,標準單元庫的電路模型,電源是不會連接出來的,但名稱都保持一致,如VDD、VSS等,只需要在Spice仿真時,設置成全局變量,就可以將他們連接在一起了。

3.2.3 添加綁定模型

集成電路的電源通常會綁定出來,由外部供電,而綁定時就會在電源連接線上產生寄生電感、電阻以及電容,如圖2所示:

圖 2綁定模型

圖2中PadInside指芯片內的連接信號,PadOutSide指通過綁定到芯片外面后的接觸點。由于這些寄生電感、電容、電阻,會使電源信號發生一定的抖動,在電源信號以及地上添加模型進行仿真,可以更加真實的反映電路的運行狀態。

3.2.4 Spice網表總體框圖

圖3所示為Spice網表總體的框圖:

圖 3 Spice網表總體框圖

如圖所示,VDD是外部供電電源,工作范圍在2.7V~3.6V,Voltage_Regulator(VR)用于產生提供給數字電路供電的電源,電壓在1.8V左右。

CguAfeREF_ENB信號由數字邏輯送給VR,對其進行控制,如果該信號為數字高電平DVDD,則VR處于正常工作模式下,可以提供足夠的電量給整個數字電路。當該信號為VSS時,VR工作在低功耗模式,只能提供較小的電量給數字電路。這里DCP是Digital Control Part的簡稱,也是整個數字邏輯電路所在,文中主要以Dlp作為其top名。powerstart信號是VR輸出給Dlp的上電復位信號,為低電平時,數字邏輯電路處于復位狀態,為高電平時,數字邏輯電路復位狀態釋放。

SPI BUS和CE信號是由Verilog格式描述的激勵。

3.2.5 數模接口描述

Spice仿真的激勵都是從Verilog激勵輸入進來的,數模接口如圖4所示:

圖 4 數模接口信號示意圖

數模接口的信號電平等信息可以在一個配置文件cosim.cfg中描述:

這里PadMiso是SPI接口的信號線之一,由模擬電路top.cdl輸出給Verilog格式仿真測例SimTop.v做邏輯判斷,當電壓超過2.6V后,仿真測例認為是邏輯1,當電壓低于0.5V時,仿真測例認為是邏輯0。這樣的信號稱為a2d(analog to digital)信號。

PadSpiClk, PadCsn, PadCE以及PadMosi是SimTop.v輸出給top.cdl的數字轉模擬的信號,稱為d2a(digital to analog)信號。當輸出為邏輯1時,top.cdl接收到3.3V,而輸出為邏輯0時,top.cdl接收到0V。

因此只需要編寫一個配置文件,就可以將數模接口信號連接起來,使HSIM和VCS進行數模聯合仿真了。

3.2.6 仿真環境的配置

啟動HSIM-VCS的仿真非常容易,只需要編寫一個執行文件腳本(如run_vcs)就可以直接運行了,整個運行的文件調用流程如圖5所示:

圖5 HSIM-VCS仿真腳本調用示意圖

在“run_vcs”中調用了2個文件,“cosim.cfg”以及“FileList.v”。“FileList.v”是一個將所有verilog格式文件包含進來的文件,其中包括了仿真激勵文件“SimTop.v”,以及只包含輸入輸出信息的頂層黑盒子申明文件“top.v”。“top.v”主要是提供VPI一個接口信息。“cosim.cfg”是HSIM-VCS數模混合仿真的配置文件。“set_args”申明了Spice仿真環境的頂層文件,叫做“test.spi”。“analog_cell”指定了Spice仿真的頂層模塊名,即top,VPI會在top的Verilog黑盒子文件“top.v”中找到所有a2d和d2a的信號,并根據“cosim.cfg”中的設置進行數模信號連接。“cosim.cfg”包含的“test.spi”是Spice仿真環境的頂層,在該文件里會做HSIM相關的配置信息。

首先,HSPICE網表第一行是用來寫注釋的,工具不讀取:

|* test.spi

HSIM的變量定義,可以是全局變量(.param),也可以是針對某個Sub-circuit的局部變量(.hsimparam subckt=xxx),如:

HSIM的 “.force”命令可以強制在某個時刻,將某個net強制設置成某一個固定的電平。

如有需要,可以為電路中所有的節點賦初值(DC Initial)。仿真到某個時刻,可以將該時刻所有節點的電壓(Operating Point)記錄下來,如:

.op 100u

上述命令會在100us的時候記錄下所有節點的電壓,并以“.ic v(…)=”的格式記錄下來,輸出文件名為hsim_.ic,如果下次仿真希望從這個時刻開始,則可以用“.inc hsim_.ic”命令使所有節點的值按照上次輸出的電壓值進行初始化,然后仿真。

3.3 仿真結果

根據3.1的仿真目標,進行了3個不同的仿真激勵。

第一個是100ns外部電源上電,這樣的上電過程速度很快,而VR為了達到預期的輸出,會對負載進行充電,設計時對充電電流進行了限流,不希望超過10mA。這里需要注意的是,Spice仿真需要一個初始值,而電路的初始值不同,其表現也可能不同,因此在該仿真過程中,將初始節點電壓都設為0V,所有電容初始狀態都沒有電荷,充電過程應該是一個最惡劣的情況,如果在該情況下都沒有超過10mA的電流,則認為VR設計正確。

第二個是5ms慢速上電,VR輸入電壓不高,但卻要給負載充電,則電流很小,如果100ns時都滿足要求,則此處可以不用考慮電流問題,但由于充電電流相當緩慢,因此該仿真的目的在于powerreset釋放時數字電路能夠正常工作。

第三個是正常功能仿真,VR能夠滿足數字邏輯的工作需求。

3.3.1 100ns電源上電

100ns電源上電仿真波形如圖6所示:

圖 6 100ns電源上電仿真結果

圖中I(rvdd1)是外部電源給VDD電源網絡供電的電流,也就是整個芯片的電流需求。I(cdvddload)是數字系統電源外部33nf濾波電容上的電流。I(sunyq)是給數字電源系統DVDD供電的電流。從圖中可以看出,powerreset釋放時,DVDD已經達到1.75V,數字電路可以正常復位。同時VDD上電速度很快,但整個芯片的電流需求不大,I(rvdd1)在上電過程中比較平緩,只有在剛上電時有一點波動,因此放大一些來看:

圖 7 100ns上電初期波形圖

從圖中可以看出, I(rvdd1)在上電初期有一個對電流需求很大的時間,是為了對33nf電容充電而產生的,但最大不超過6mA。VR滿足了我們的需求。

3.3.2 5ms電源上電

下圖所示是5ms電源上電的波形圖:

圖8 5ms電源上電波形圖

由上圖可知,I(rvdd1)在上電過程中非常平緩,沒有超過10mA,但powerreset釋放時,數字電路的供電只有1.25V左右。由于電路設計的特殊性,電路復位釋放后并不會立刻工作,而是要等很久(超過百ms級)才會開始工作,而從圖上看出DVDD電壓仍然在上升,且1.25V,已經可以保證電路正確復位。因此這里認為,VR設計滿足要求。

3.3.3 正常功能仿真

圖9所示是正常功能仿真的波形圖:

圖9正常功能仿真波形圖

從整個仿真過程看,VDD在2us時間上電,DVDD也在50us左右達到較高電壓(約1.6V)。powerstart在約55us時釋放,SPI在約110us時置起spicgupwrup使Dlp從PowerDown模式進入了StandBy模式,然后在StandBy模式下,SPI置起bootload信號,進入DataLoad模式并下載程序,接著退回StandBy模式。拉高CE后,系統進入發送模式,發送數據,發送進行過程中,CPU寫apreg啟動低功耗的AP模式,經過約100us后,SPI強制退出AP模式回到發送模式。

整個過程看來都比較正常,電流I(rvdd1)在發送模式時最大,有2mA左右(圖中沒有)。

可以看出整個設計滿足功能需求。

3.3.4 測試結果

樣片測試時,負載電容為100nF,是仿真時(33nF)的3倍,上電時間選擇了9.7us,獲得最大電流尖峰為8.24mA,上電充電時間約10us,DVDD達到約1.0V,如下圖所示:

圖10 樣片測試上電波形圖

用實測結果與100ns上電仿真的結果對比可以看出,DVDD上升時間從0V到1V都用了約10us,這也是對電容充電的過程。同時測試過程中的電流比100ns上電仿真的電流略大,原因是負載電容較大,需要用更大的電流進行充電。

需要注意的是對負載電容充電的電流來自于VR的1.8V DVDD輸出,因此當電源(3.3V)上電速度較快的情況下,負載電容充電與上電時間沒有特別大的關系。(由100ns上電仿真結果和測試結果看出,充電過程主要是在DVDD上升時開始的)

因此通過上電測試結果可以看出,VR的設計滿足設計需求,上電過程中沒有出現過大的電流,同時上電的特性曲線與HSIM-VCS仿真結果相近。

另外通過芯片的應用開發,也證明數字部分的設計滿足需求,芯片可以正確工作。

3.4 仿真時間

整個電路有約23萬個器件和10萬個節點。下表所示是各測例平臺運行時間以及仿真時間:

可以看出仿真時間在3天以內,且精度基本滿足要求,可對分析全芯片的功耗和電流曲線提供有效幫助。

4.0 全芯片數模混合功能仿真

4.1 目標

需要進行全芯片數模混合功能仿真的功能點有:

?接收解調頻偏調整機制

?數據發送通路功能

?RFIC數據通路收發通信

?全芯片的寄存器功能掃描

?RFIC全芯片的收發通信

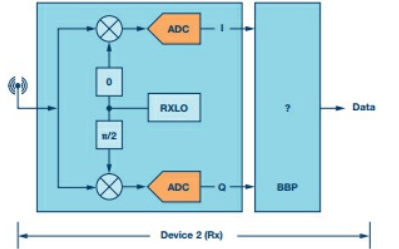

限于篇幅,筆者將重點介紹對接收解調頻偏調整機制的仿真。在射頻通訊系統中晶振很小的頻率漂移可能會導致接收中頻偏差較大,特別是在低中頻方案中,當中頻偏差與調頻系統中的數據頻偏可比擬時,數據就可能被淹沒。為了解決這個問題,需要制定一種頻率調整方案,這個方案可以根據接收中頻的頻率自動校正解調時鐘,讓解調時鐘跟蹤接收中頻的偏差。接收解調頻偏調整機制仿真目標如下:

?確認數模接口連接正確性

?確認頻偏調整機制正確性

?各種特征數據的沖擊

4.2 工具環境

評估初期,采用HSIM-VCS搭建混仿環境。由于設計規模較大,為了加速仿真,采用了XA-VCS搭建混仿環境,采用如下表所示的EDA工具和工作站環境。XA是Synopsys的新一代SPICE仿真工具,可以在實現仿真加速的同時得到好的仿真精度。XA可以通過DKI的方式實現與VCS的數模混合仿真驗證。

4.3 仿真對象

Demodulator模塊設計完成之后,與整個數字鏈路層整合,進行模塊級數模混合仿真:

?DLP,數字鏈路層,RTL代碼

?Demofdiv,分頻數字模塊,RTL代碼

?Demodulator,解調模擬模塊,HSPICE網表

?其它模擬模塊(Fm_Modulator、Limiter、Shifter),Verilog-A模型

4.4 仿真腳本

參照Synopsys技術支持團隊提供的XA-VCS混仿范例中的以Verilog為頂層的例子,仿真腳本編寫如圖10。

圖10仿真腳本

4.5 仿真激勵

(A)Fm_Modulator的壓控信號VIN輸入激勵:前面一段紋波較大,仿真PLL還沒有完全鎖定時的情形,中間一段為帶+/-30KHz紋波的中頻,僅接著后面為前導,然后是數據:1010001000111011100011100010101110100010。該組數據考慮了各種數據的組合。

(B)為模擬內部信號對VREF的干擾帶來的影響,VREF端口激勵采用下圖方式:

圖 11 VREF端口激勵

(C)為模擬電源上紋波的影響,在電源上添加50mVp的2MHz信號和50mVp的32MHz信號。

(D)demodulator的電源AVDD、DVDD、AVSS、DVSS均添加了5nH的bonding wire 電感。

針對以上激勵,做了如下內容的仿真:

(a)輸入信號激勵采用A中所述激勵,其它如VREF、電源、地都采用理想激勵,中頻載波頻率從從1.6M~2.4MHz,step為10KHz,共81個測例。

(b)以上A、B、C、D均采用,輸入中頻分別為1.6M、1.65M、1.69M、1.7M、1.71M、1.8M、1.9M、2M、2.1M、2.2M、2.29M、2.3M、2.31M、2.35M、2.4M共15個激勵。工藝模型和溫度劃分為四種情況:TT,27℃;TT,-40℃;SS,85℃;FF,-40℃。

4.6 仿真結果

(1)仿真內容(a)的81個測例均正常。

圖12仿真內容(a)結果波形

(2)仿真內容(b)的結果:60個測例中,有7個測例出現前導判決不出來的錯誤,即前導兩個bit的寬度差異性較大,已超出了設計允許范圍,不支持;其它測例結果正確。與實測結果一致。

圖13仿真內容(b)結果波形

4.7 仿真時間

仿真時間記錄如下:

4.8 小結

通過接收解調頻偏調整機制數模混合仿真時間量化表,可以發現在同樣可接受的精度情況下,XA-VCS的仿真速度是HSIM-VCS的10倍以上;所以在該RFIC全芯片的收發通信數模混合仿真中,節省的時間量級為8.5 * (10-1)days = 76.5 days = 2.55 months。

5.0 總結

在該RFIC測例中,利用HSIM-VCS和XA-VCS進行數模混合仿真,發現了設計Bug 8處,并可以節省大量的驗證時間。

從該芯片的物理測試結果來看,利用該方法確實可以較為準確的獲取到芯片的功耗信息,確保數模接口功能,為投片成功保駕護航。

-

功率放大器

+關注

關注

102文章

3518瀏覽量

131658 -

EDA工具

+關注

關注

4文章

264瀏覽量

31715 -

仿真器

+關注

關注

14文章

1016瀏覽量

83644 -

射頻收發器

+關注

關注

4文章

256瀏覽量

25387 -

寄生電感

+關注

關注

1文章

155瀏覽量

14586

發布評論請先 登錄

相關推薦

高性能PHS—RF收發器芯片設計方案

RadioVerse生態系統中的寬帶收發器

如何采用超低功率RF收發器芯片實現體內通信系統的設計討論

RadioVerse生態系統中的寬帶收發器分享!

什么是用于RF收發器的簡單基帶處理器?

如何采用RF收發器實現體內通信系統的設計?

優化信號鏈的電源系統 — RF收發器

優化信號鏈的電源系統 — RF收發器

系統級RF收發芯片nRF24E1及其在無線鍵盤中的應用

通過采用超低功率RF收發器芯片設計植入式醫療設備的通信系統

如何使用RF收發器實現簡單的基帶處理器

HSIM, XA及其與VCS的混合驗證方案在RF收發器芯片中的應用

HSIM, XA及其與VCS的混合驗證方案在RF收發器芯片中的應用

評論