大家在構建測試激勵時,經常會遇到需要使某個信號強制變成某個值,此時我們經常會用到Verilog和SystemVerilog中的force實現這樣的功能。但是有時候在對多位寬的信號進行force時有時會出現編譯錯誤,這是為什么呢?本文將對此類情況進行示例說明。

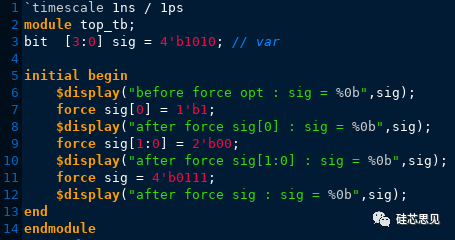

【示例】

【仿真結果】

示例中,通過三種方式對sig中的部分位選進行了force。通過force將sig中的第0位force為了1,從顯示信息可以看到sig[0]已經被修改;通過force將sig中的第0位和第1位force為了00,從顯示信息可以看到sig[1:0]已經被修改;通過force將sig整體force為了0111,從顯示信息可以看到sig[1:0]已經被修改;

可以看到,我們可以通過force對于變量、變量中的某一位或者某一個片段進行改變,那么可能有些人覺得這么一位一位的進行force太麻煩了,是否可以使用for循環對sig中所有位遍歷進行force呢?請看下例。

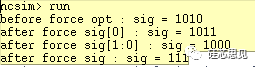

【示例】

【仿真結果】

編譯錯誤!這是為什么呢?對比該示例和上一示例,可以發現當信號的索引為常值時,可以進行force,但是當索引為變量時,此時編譯不通過。

也就是說在對信號進行force的時候,如果要對其中的某一位或者一個片段進行force時,其中的索引只能是常數不能是變量,否則將會導致便以失敗。

那么如果想實現通過變量實現對于多位寬信號中每一位進行force還有什么辦法嗎?下面我們通過示例介紹幾種。

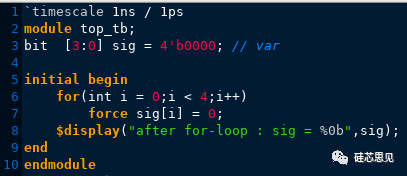

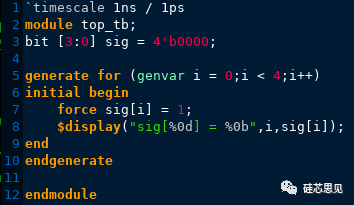

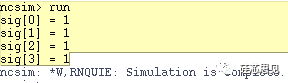

【示例】使用generate結構

【仿真結果】

示例中,使用generate結構實現了對于sig中每一位的遍歷。這其實借助了generate是在仿真前的析構(elaboration)階段完成的特性,即在仿真開始之前,相當于已經將sig被force的每一位的initial結構都已經生成好了,這樣在仿真開始執行時(生成好的initial塊開始被執行時),其中“force sig[i]”中的i都已經是確定的值了,因此就可以避免force信號中某一位時,索引為變量的情況。

除了這種在析構(elaboration)階段就生成好語句結構的方式外,還可以想如下方式操作。

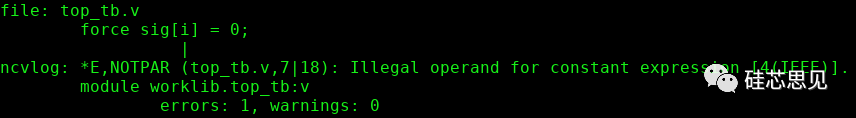

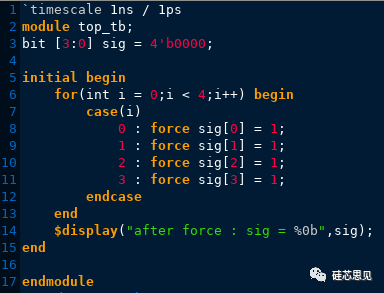

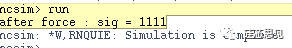

【示例】

【仿真結果】

示例中,實際上是將要force的信號每一位都單獨寫了出來,即保證了被force信號的索引都是常量,缺點是,如果這個信號比較寬,那么寫起來比較枯燥,沒有上一種使用generate結構方便。但是實際上兩者之所有都沒有問題,其實都是保證了被force信號的索引是個常值。

所以,如果在實際使用時,需要對多位寬信號的每一位或者某一個片段進行force,那么需要保證被force的那一位或者那一個片段的索引值在仿真運行開始時是常值。

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1016瀏覽量

83644 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8214

原文標題:如何遍歷force多位寬信號的每一比特

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

同步從一個時鐘域到另一個時鐘域的多位信號怎么實現?

I-Force410無鐵芯直線電機

LS1046 SDRAM多位錯誤注入怎么處理?

Design of Crimp force Monitor

存儲百倍提升! IBM納米技術1比特12原子

二叉樹的前序遍歷、中序遍歷、后續遍歷的非遞歸實現

螺旋遍歷二維數組漫畫講解

總結一下OpenCV遍歷圖像的幾種方法

HashMap遍歷操作為什么不能一邊遍歷一遍刪除呢?

跨時鐘域電路設計:多位寬數據通過FIFO跨時鐘域

如何遍歷force多位寬信號的每一比特?

如何遍歷force多位寬信號的每一比特?

評論