MOSIS:ORBIT 2.0u SCNA規則

v1 Vdd Gnd 5.0

v2 Clk Gnd pulse(0.0 5.0 0 10n 10n 100n 200n)

v4 ClB Gnd pulse(0.0 5.0 0 10n 10n 1000n 1000n)

v3 Data Gnd pulse(0.0 5.0 0 10n 10n 80n 150n)

########################################

邏輯綜合完成之后,通過引入器件制造公司提供的工藝信息,前面完成的設計將進入布圖規劃、布局、布線階段,工程人員需要根據延遲、功耗、面積等方面的約束信息,合理設置物理設計工具的參數,不斷調試,以獲取最佳的配置,從而決定組件在晶圓上的物理位置。如果是全定制設計,工程師還需要精心繪制單元的集成電路版圖,調整晶體管尺寸,從而降低功耗、延時。

隨著現代集成電路的特征尺寸不斷下降,超大規模集成電路已經進入深亞微米級階段,互連線延遲對電路性能的影響已經達到甚至超過邏輯門延遲的影響。這時,需要考慮的因素包括線網的電容效應和線網電感效應,芯片內部電源線上大電流在線網電阻上造成的電壓降也會影響集成電路的穩定性。為了解決這些問題,同時緩解時鐘偏移、時鐘樹寄生參數的負面影響,合理的布局布線和邏輯設計、功能驗證等過程同等重要。隨著移動設備的發展,低功耗設計在集成電路設計中的地位愈加顯著。在物理設計階段,設計可以轉化成幾何圖形的表示方法,工業界有若干標準化的文件格式(如GDSII)予以規范。

-

電容器

+關注

關注

64文章

6202瀏覽量

99317 -

電感器

+關注

關注

20文章

2321瀏覽量

70411 -

仿真器

+關注

關注

14文章

1016瀏覽量

83643 -

晶體管

+關注

關注

77文章

9634瀏覽量

137850 -

D觸發器

+關注

關注

3文章

164瀏覽量

47863

發布評論請先 登錄

相關推薦

D觸發器,CLK突變時,輸入D也突變,觸發器的輸出應該如何判定?

jk觸發器是什么原理_jk觸發器特性表和狀態轉換圖

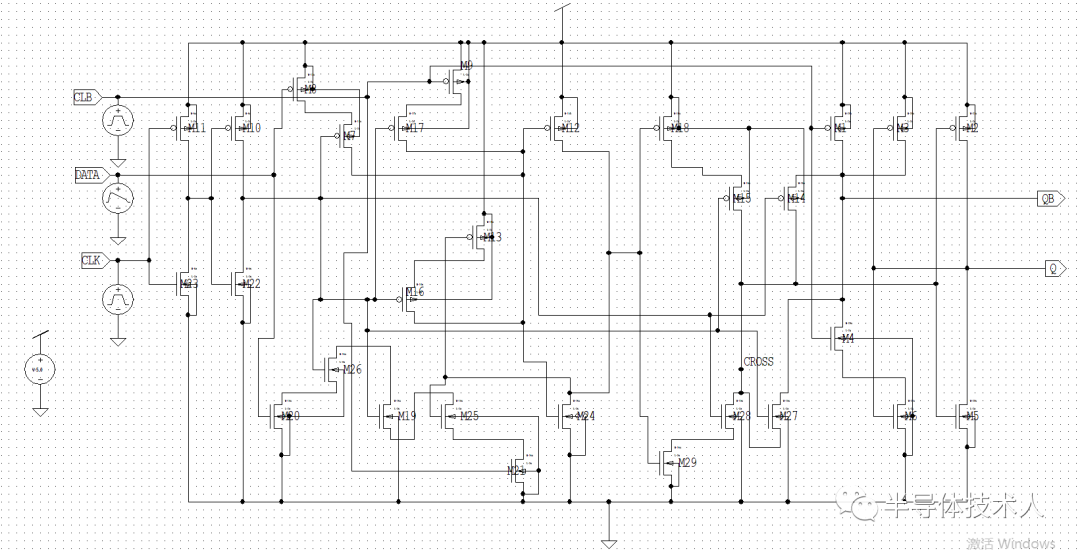

D觸發器版圖電路瞬態特性仿真

D觸發器版圖電路瞬態特性仿真

評論