1. 前言

本文講一下SystemVerilog的time slot里的regions以及events的調度。SystemVerilog語言是根據離散事件執行模型定義的,由events驅動。SystemVerilog描述是由連接的執行thread或processes組成。Process是可衡量的,也具有狀態,并且可以響應輸入的變化以產生輸出。Process是并發調度的元素,例如initial,process其實還包括了always, always_comb, always_latch, always_ff, contiguous assignment, asynchronous tasks和procedural assignment statement。

SystemVerilog是一種并行編程語言,我們需要重點了解哪些執行順序對用戶是有保證的,哪些執行順序是不確定的。這塊內容比較晦澀難懂,但要是理解了regions和events的調度,對我們寫代碼和調試會有極大的幫助,而且也更了解EDA工具的執行機制。

2. Event的定義

在仿真系統中net或variable的狀態的任何更改,都被視為更新事件(update event)。Processes對upate event是敏感的。當一個update event發生時,所有對該event敏感的processes都會被當作以任意順序進行評估。Process的評估也是一個event,稱作評估事件(evaluation event)。Evaluation events包括PLI callbacks,這些callbacks是執行模型中的節點,PLI應用程序可以從仿真內核調用。所以,這些events會在不同的regions中發生。

3. Region的定義

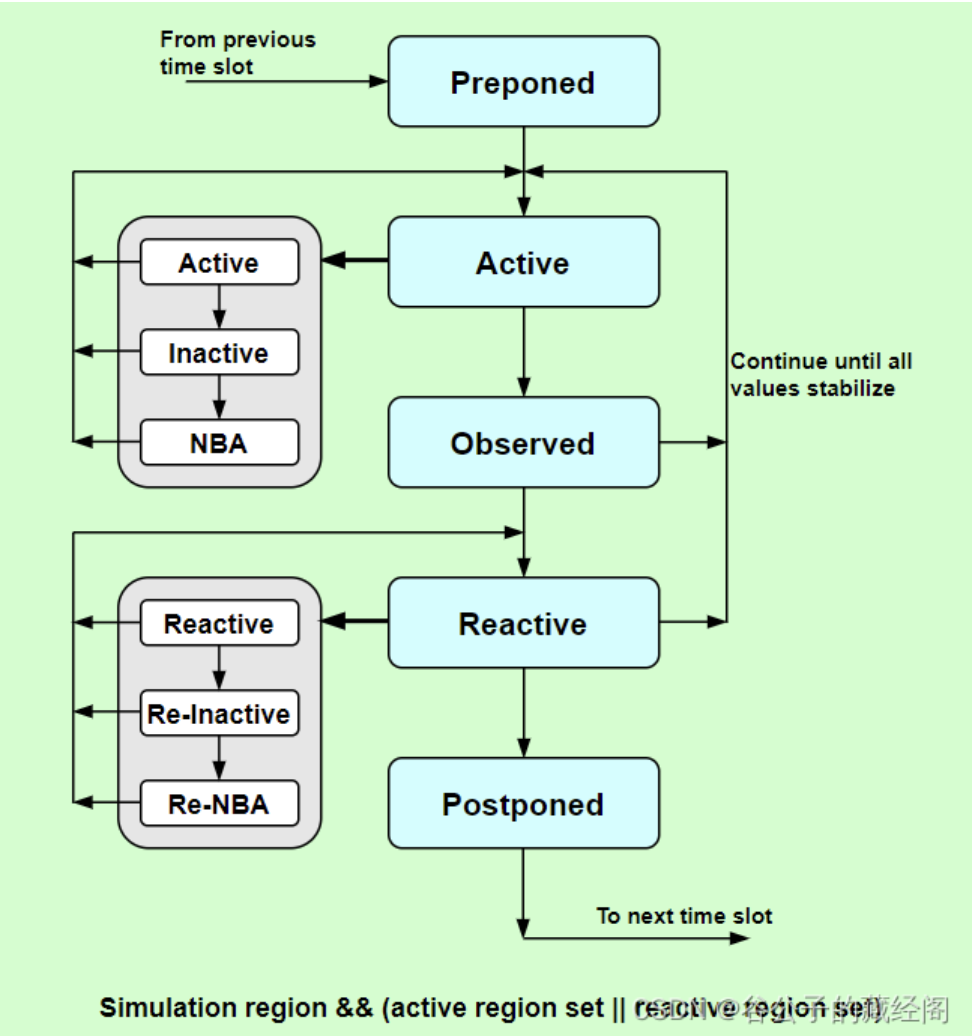

為了支持清晰和可預測的交互,將單個time slot劃分為多個region,events就被以確定的執行順序安排到這些regions中,這就允許DUT代碼和驗證代碼之間可預測的交互。在特定時間的所有scheduled events定義了1個time slot。在移動到下一個time slot之前,仿真按照時間順序進行并刪除掉當前仿真時間slot中的所有events,從而使得仿真前進。這個過程保證了仿真器不會在時間上倒退。一個time slot可以被劃分為一組有序的regions,有:Preponed,Pre-Active,Active,Inactive,Pre-NBA,NBA,Post-NBA,Pre-Observed,Observed,Post-Observed,Reactive,Re-Inactive,Pre-Re-NBA,Re-NBA,Post-Re-NBA,Pre-Postponed,Postponed。如圖1。

圖1 time slot執行流程圖

其中Active, Inactive, Pre-NBA, NBA和Post-NBA regions中scheduled events稱為active region set events。Reactive, Re-Inactive, Pre- Re-NBA, Re-NBA和Post-Re-NBA regions中scheduled events稱為reactive region set events。

Active, Inactive, Pre-NBA, NBA, Post-NBA, Pre-Observed, Observed, Post- Observed, Reactive, Re-Inactive, Pre-Re-NBA, Re-NBA, Post-Re-NBA和Pre-Postponed regions被稱為iterative regions。

除了active region set和reactive region set,每個time slot的event regions可以分為simulation regions和PLI regions。圖1中,圓角長方形的屬于simulation regions。橢圓形的屬于PLI regions。

4. Events調度參考算法

當仿真開始時,先初始化所有nets和variables的初始值,并在0 time slot上開始調度初始化events。

當發現有非空的time slot時,也就是time slot里有scheduled event。它會去執行第一個非空的time slot,就開始按照圖1的流程圖順序執行各個region。當進入1個region內時,找到當前region內的scheduled event,判斷event類型,如果是update event類型,更新這個event對象,且為對該event對象敏感的任何process安排evaluation event;如果是evaluation event類型,評估與這event相關的process,并可能安排進一步執行的events。

Time slot里的這些region中,Prepone、Pre-Active和Postponed只會執行一次。其它的region,具體要看event的情況,可能會執行多次。不過總體遵循這個流程:

- 順序處理Prepone和Pre-Active region。

- 處理從Active到Post-Observed的region,會從里面找到第一個有非空event的region處理,直至全部event處理完且刪掉。需要注意的是,如果在NBA region的觸發了一個需要在Active region處理的event,那么會從NBA跳回Active region去處理,然后按順序繼續尋找第一個有非空event的region。

- 當步驟2的regions全部處理好之后,會開始處理從Reactive到Post_Re-NBA region,也是類似的,會從里面找到第一個有非空event的region處理,直至全部處理完畢。

- 當步驟3的region也全部處理完之后,會再重新判斷下從Active到Post Re-NBA region是否還有未處理的,如果有就又要從第一個非空event的region處理,如果沒有就執行Pre-Postponed region。5. 當步驟2-4里的都沒有非空event的region后,處理Postponed region。6. 步驟5處理完之后,就進入到下一個time slot了。

5. Regions調度的events類別

Time slot的simulation regions包含了Preponed, Active, Inactive, NBA, Observed, Reactive, Re-Inactive, Re-NBA和Postponed regions。再根據active region set和reactive region set的劃分,我們可以將一個time slot的simulation regions分為五個主要region:Preponed、Active、Observed、Reactive和Postponed。Active和Reactive可以進一步細分為小的regions。如圖2所示。

圖2 Simulation regions

這五大regions里調度的events有:

Prepone: 在一個time slot內,Prepone region只會執行一次,當仿真時間進入當前time slot時,它是第一個被執行的region。驗證環境采樣DUT的信號就發生在這個region。我們平時在采樣DUT信號時,會指定#1step采樣延遲,#1step采樣延遲提供了在進入當前time slot之前立即采樣信號的能力。#1step采樣相當于在當前time slot的Prepone中采樣信號。所以在Preponed region的采樣相當于前一個time slot Postponed region的采樣。Preponed region PLI events也在這里調度。

Active: Active包含了幾個小的regions:active,inactive和NBA(nonblocking assignment update) regions。

- Active region進行當前active region set events的評估求值,并且這些events會被任意處理。RTL代碼和行為代碼(behavioral code)被安排在active region。所有blocking assignments語句在Active region執行。對于nonblocking assignments,RHS的評估求值發生在Active region,而賦值發生在NBA region。如果有任何#0延遲的assignment,那么這些assignment發生在Inactive region。(注意:#0延遲的RHS是在inactive region是算的)

- Inactive region進行處理完所有active events后要評估的events。顯式的#0延遲控制要求將這個event安排到當前time slot的inactive region進行,以便在下一個inactive到active迭代中恢復process。

- NBA region進行處理完所有inactive events后要評估的events。Nonblocking assignment會在當前或以后仿真時間的NBA region中創建events。

Observed: Observed用于觸發property expressions(用于concurrent assertions)時對其求值。在property求值后,pass/fail的信息將在當前time slot的Reactive region報告出來。

Reactive: Reactive包含了Re-active,Re-inactive和Re-NBA regions。

Re-active進行當前reactive region set的評估求值,并且可以以任何順序進行處理。Program blocks的blocking assignments、#0 blocking assignments的RHS求值和nonblocking assignment的RHS求值發生在re-active region。另外,concurrent assertions的action blocks的代碼也是在re-active region調度的。Re-active region和active region其實是對偶關系的。只不過active處理design,re-active處理program。

Re-inactive進行處理完所有re-active events后要評估的events。Program里顯示的#0延遲控制要求將這個event安排到當前time slot的re-inactive region進行,以便在下一個inactive到active迭代中恢復process。同樣的,它也是inactive region的對偶關系。

Re-NBA進行處理完所有re-inactive events后要評估的events。Program里nonblocking assignment會在當前或以后仿真時間的re-NBA region中創建events。

Postponed: postponed是當前time slot的最后1個region。**monitor, **strobe和其它相似的events會安排在這個region執行 (注意$display event是在active region和reactive region(如果在program里調用)執行的)。一旦到達postponed region,就不允許在當前time slot中發生新的值更改。在此region內,向任何net或variable進行寫入值或在當前region調度任何先前region的event都是非法的。Postponed region PLI events也在這里調度。

在一個time slot里,除了上述介紹的simulation regions,還有PLI regions,在PLI regions里會去調度PLI callback。PLI regions有Preponed, Pre-Active, Pre-NBA, Post-NBA, Pre-Observed, Post-Observed, Pre-Re-NBA, Post-Re-NBA 和Pre-Postponed regions。它是圖1中的橢圓型部分。本文重點講述simulation regions,這里就不介紹PLI regions了。

6. SystemVerilog里的確定和不確定調度順序

以下場景必須有確定的調度順序:

begin-end塊中的語句應該按照它們在該begin-end塊中出現的順序執行。可以暫停特定begin-end塊中語句的執行,以利于模型中的其它進程;但是在任何情況下,begin-end塊中的語句都不得以它們在源代碼中出現的順序以外的任何順序執行。

NBAs語句應按照語句執行的順序執行。

舉個例子:

module test;

logic a;

initial begin

a <= 0;

a <= 1;

end

endmodule

當執行initial塊時,將會有兩個event被添加到NBA region。前面的規則要求它們按照執行順序進入event region,在連續的begin-end塊中,這是初始順序。該規則要求它們去NBA region也按照這個順序執行。因此,在仿真時間0結束時,變量a將被賦值為0,然后賦值為1。

在以下場景時,執行的順序是不確定的:

Active events可以從active或re-active event region中取出,并以任何順序進行處理。

過程塊(procedural block)中沒有時間控制結構的語句不必作為一個event執行。時間控制語句是指#expression和@expression結構。在評估過程語句時的任何時候,仿真器都可以暫停執行并將部分完成的事件作為待處理事件放置在event region中。 這樣做的效果是允許進程執行的交錯,盡管交錯執行的順序是不確定的并且不受用戶控制。

-

EDA工具

+關注

關注

4文章

264瀏覽量

31714 -

仿真器

+關注

關注

14文章

1016瀏覽量

83633 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8213 -

DUT

+關注

關注

0文章

189瀏覽量

12338 -

調度器

+關注

關注

0文章

98瀏覽量

5238

發布評論請先 登錄

相關推薦

[啟芯公開課] SystemVerilog for Verification

round robin 的 systemverilog 代碼

做FPGA工程師需要掌握SystemVerilog嗎?

如何解決no space in execution regions問題?

在BLE broadcaster基礎上測試TMOS調度,無法正常調度是為什么?

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊

Meter Design for Power Failure Events

基于SystemVerilog語言的驗證方法學介紹

SystemVerilog里的regions以及events的調度

SystemVerilog里的regions以及events的調度

評論