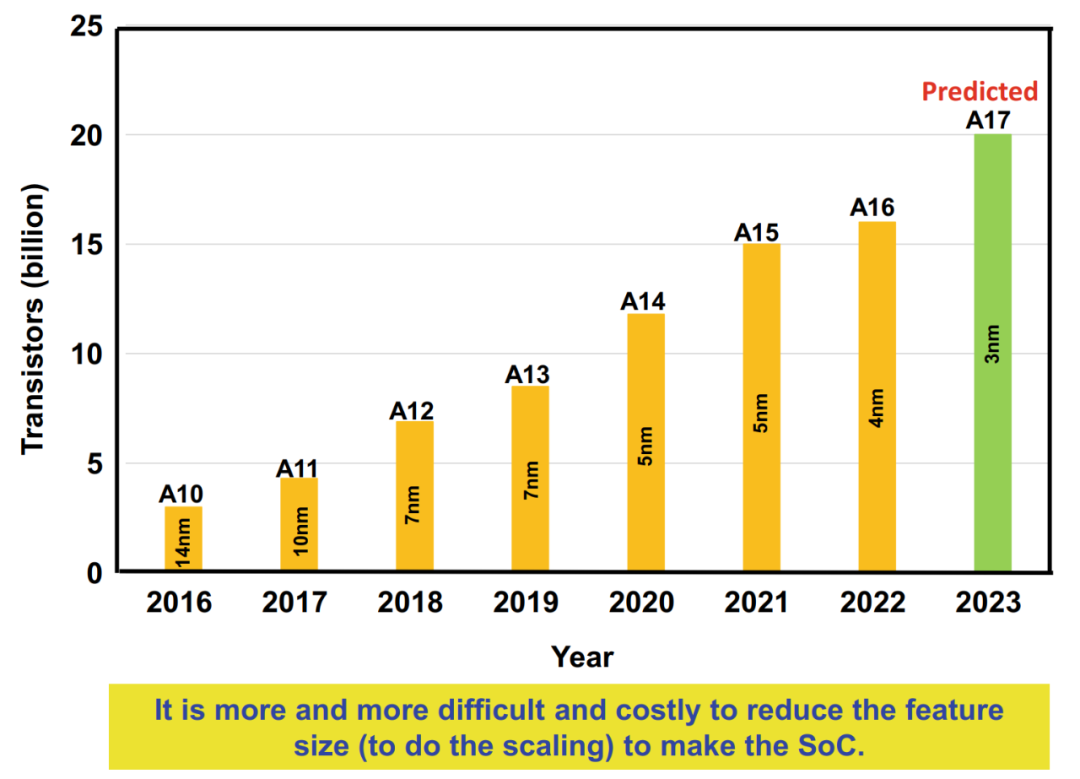

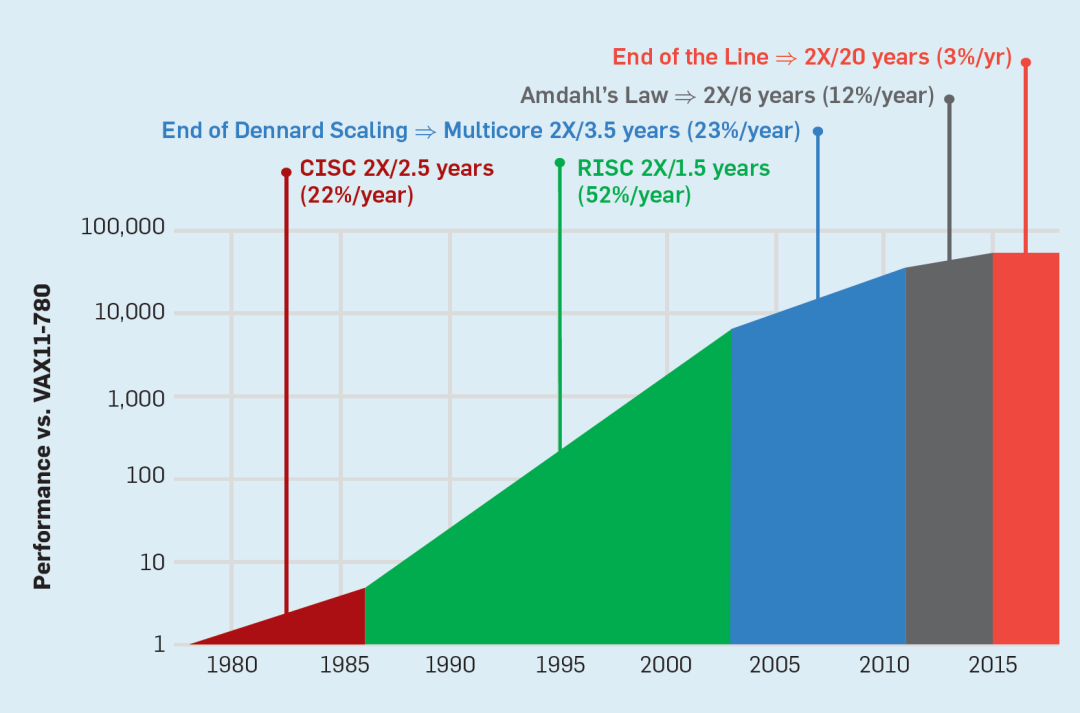

摩爾定律描述了集成電路上晶體管數量大約每兩年翻一番的經驗規律,它對計算技術進步來說至關重要,比如處理速度或計算機價格。早在1965年,戈登·摩爾(Gordon Moore)就曾指出:“用單獨封裝和互連的較小功能構建大型系統可能會更經濟。”

幾十年來,晶圓廠成功實現了數字能力和晶體管密度的指數級增長。今天,芯粒(又稱Chiplet)等新的工藝技術與先進封裝方案不僅沒有違反摩爾定律,反而還在為延續摩爾定律,繼續實現數字縮放進步而賦能。

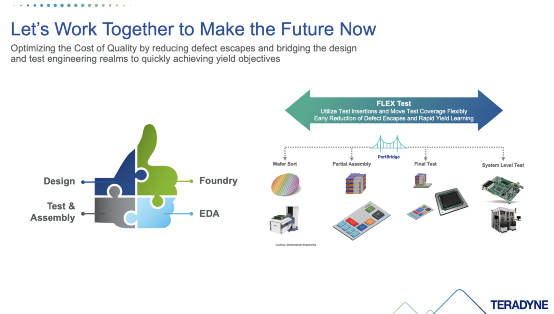

雖然Chiplet近年來越來越流行,將推動晶體管規模和封裝密度的持續增長,但從設計、制造、封裝到測試,Chiplet和異構集成也面臨著多重挑戰。因此,進一步通過減少缺陷逃逸率,降低報廢成本,優化測試成本通過設計-制造-測試閉環實現良率目標已成為當務之急。

總體質量成本優化策略至關重要

當我們處理更復雜的測試流程時,比如KGD(Known Good Die)測試、最終測試和系統級測試,優化總體質量成本的策略仍然至關重要。策略背后的關鍵點包括以下幾個方面:

在設計過程的初期,新產品導入或大批量生產之前,設計人員和測試工程師需要進行充分協作,利用通用工具進行芯片驗證和故障調試;

將某些測試流程轉移到整個流程的早期,以減少KGD集成之前的早期缺陷;

將一些測試推遲到制造過程的后期,以降低測試成本,進一步優化成本;

隨著制造過程的成熟和穩定,對這些過程進行大數據分析,以便調整制造過程中的測試流程,從而優化總體質量成本。

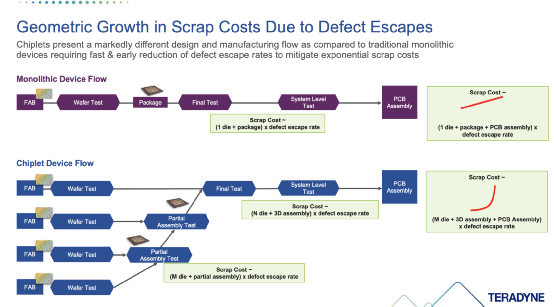

缺陷逃逸導致報廢成本呈幾何級數增長

與傳統單片器件相比,Chiplet的設計和制造流程明顯不同,與制造傳統單片半導體器件相關聯的報廢成本實際上是線性的,包括單芯片成本、封裝和組裝成本。Chiplet或3D先進封裝的制造流程在廢料成本的積累方面有很大不同。具體講,從制造到組裝,報廢成本呈幾何級數增加,因為其中包括了多個管芯、多芯片部分組件或全3D封裝的報廢成本。

雖然3D封裝是摩爾定律繼續向前的的推動者,不過這種方法的經濟可行性在于,需要能夠在制造流程的早期減少缺陷逃逸率,從而降低報廢成本。

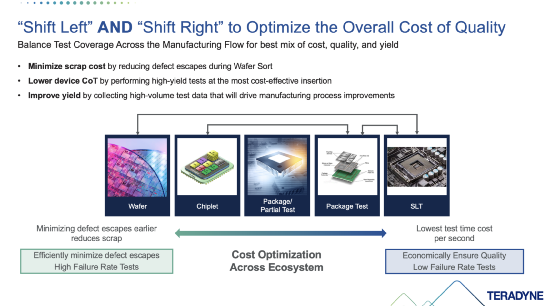

“左移”還是“右移”?

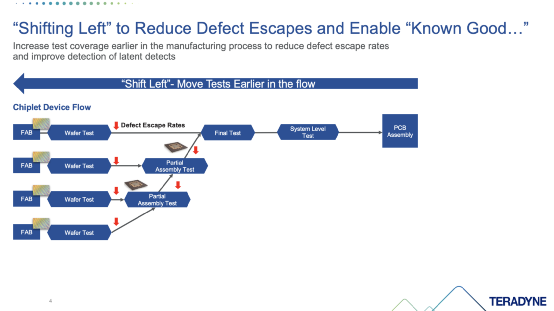

“左移”是一種在制造流程早期降低缺陷逃逸率降低報廢成本,從而3D組件的總體制造成本降至最低的策略。“左移”是在制造過程的早期增加測試覆蓋率,以降低缺陷逃逸率并改進潛在檢測的能力。

減少缺陷逃逸的方法之一是啟用“Known Good”。為減少缺陷逃逸生產“Known Good”的器件,需要在包括晶圓檢測和部分封裝的階段,即制造流程的早期,提高測試覆蓋范圍,同樣,還可以在流程中增加額外的測試,以識別新的故障類型或故障模式,例如通過邊界掃描的測試覆蓋發現與部分組件相關的互連問題。

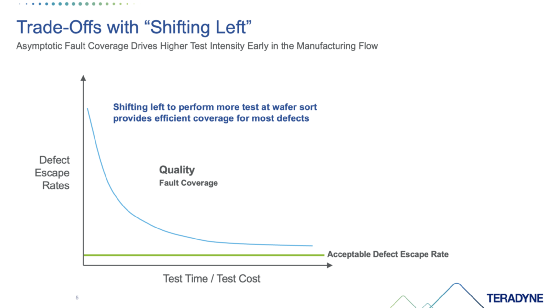

當然,作為實現“Known Good”的手段,“左移”也需要進行權衡。例如,在制造流程的早期增加測試強度,可以大大降低缺陷逃逸率。然而,“左移”在逐漸接近可接受的缺陷逃逸率時,會導致測試成本持續增加,而缺陷逃逸率降低的帶來的報廢成本的減少則會遞減。

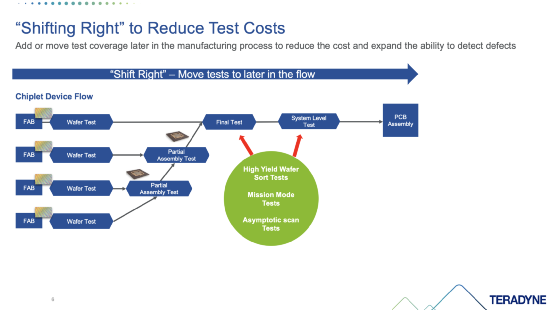

“右移”是增加制造流程后期的測試覆蓋率,擴大檢測缺陷的能力,在降低成本同時確保質量水平的可行手段。

通常,晶圓測試良率較高的測試項、任務模式測試或需要較長測試時間掃描測試的高良率測試是“右移”的理想候選者。這些測試可以轉移到最終測試或系統級測試階段,或者在兩者之間靈活管理,在實現質量目標的前提下進一步降低成本。

不管是“左移”還是“右移”,都是為了在整個制造流程中、質量和良率的最佳組合,最終優化整體質量成本。具體的策略包括:通過降低晶圓檢測過程中的缺陷逃逸率,最大限度地降低報廢成本;以最高效的方式實現量產測試,從而降低芯片的測試成本;通過大數據推動整個制造工藝的閉環和改進,從而提高良率。

那么在生產中,要選擇將測試“左移”還是“右移”呢?

兩者兼而有之是問題的答案。為了管理整體質量成本,有必要“左移”和“右移”。左移提供了一種在制造流程早期降低缺陷逃逸率的方法,而右移則可以實現在可控測試成本的同時達到需要的產品質量水平。

“左移”增加了晶圓檢測的覆蓋率,通過高故障率的結構、參數、掃描及壓力測試,為工藝改進和優化提供有價值的信息;“右移”為檢測“難以找到”或需要長時間掃描的測試或壓力測試提供了一種經濟的手段。

在面對“左移”還是“右移”的選擇中,優化測試策略是一個動態和持續的過程。大數據為測試策略的決策提供了依據。泰瑞達靈活測試方案和工具組合,可以在整個芯片制造流程中靈活調整測試策略,持續優化制造成本和保障質量。

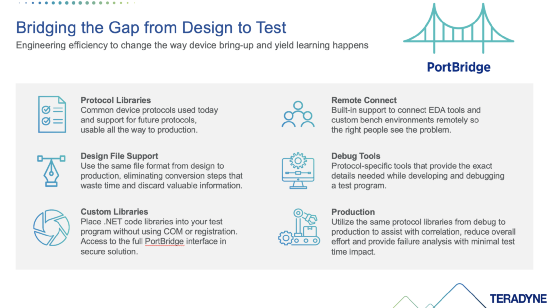

彌合從設計到測試的差距

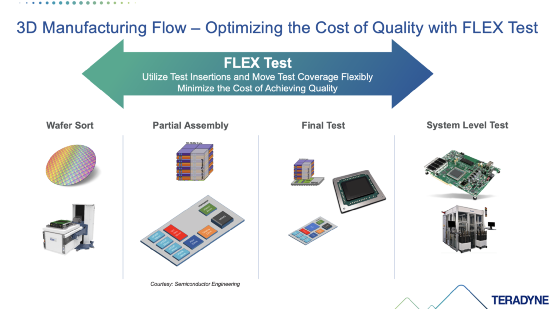

Chiplet是先進封裝中的組成單元,而3D是先進封裝的工藝手段。利用靈活測試可以優化3D制造流程的質量成本。靈活測試可以移動測試覆蓋范圍,包括晶圓檢測、部件裝配、最終測試、系統級測試,最大限度地降低實現質量的成本。

事實上,在制造流程的早期,最大限度地降低缺陷逃逸并不是一個靜態問題。學習、工藝改進和新技術都為實現整個制造流程中測試覆蓋率的平衡提供了機會。因此,在制造流程中靈活地“左移”或“右移”測試覆蓋范圍的能力很重要。這種靈活性將有助于應對制造過程不斷發展的成熟度,并對質量成本的持續優化做出響應。

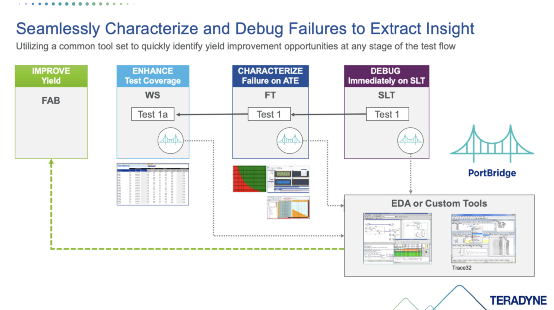

事實上,減少缺陷逃逸并非事情的全部,還需要考慮良率如何。

為了實現這一點,就要彌合從設計到測試的差距,提升工程效率,以改變器件的調試(debug)和良率學習(yield learning)方式。新的工作流程需要設計,制造和測試工程團隊無縫合作的方式,以加快器件的開發并產生學習效果。不僅需要在SLT和ATE測試系統上啟用EDA和JTAG工具,還需要通過一組通用的庫和調試工具,讓設計和DFT工程師可以無縫合作,同時共享關鍵見解,從而加速芯片開發并縮短學習時間。

值得一提的是,通用的工具集可以彌合設計和測試之間的差距,它可以在制造流程的任何階段部署,以識別、實施和驗證提高良率的機會。例如,該工具集可以在系統級測試中調試故障,在最終測試插入中對故障進行更深入的驗證,在晶圓檢測中增強的測試覆蓋率,以減少缺陷逃逸,并揭示生產流程中的“秘密”,以改進器件或工藝,完全消除缺陷并提高良率。

設計和測試攜手創造未來

快速識別是在制造過程早期經濟地降低缺陷逃逸率的關鍵。靈活的測試流程,加上設計和測試工程領域能力的整合,將有助于快速識別、調試和消除故障,同時實現最佳的質量成本。

與3D Fabric Alliance中的EDA、設計、代工、測試和組裝合作伙伴合作,對于充分實現靈活的測試流程,并收集滿足3D封裝設計的質量目標成本所必需的關鍵學習工具至關重要。

來自EDA公司、DFT、運營、晶圓代工廠、OSAT、ATE-SLT供應商團隊之間的合作將是成功的關鍵。讓我們一起努力創造未來,快速實現良率目標。

-

芯片

+關注

關注

454文章

50460瀏覽量

421973 -

封裝

+關注

關注

126文章

7794瀏覽量

142741 -

chiplet

+關注

關注

6文章

419瀏覽量

12561

原文標題:Chiplet和異構集成時代芯片測試的挑戰與機遇

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

創新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

剖析 Chiplet 時代的布局規劃演進

西門子EDA創新解決方案確保Chiplet設計的成功應用

Chiplet是否也走上了集成競賽的道路?

Chiplet和異構集成時代芯片測試的挑戰與機遇

Chiplet和異構集成時代芯片測試的挑戰與機遇

評論