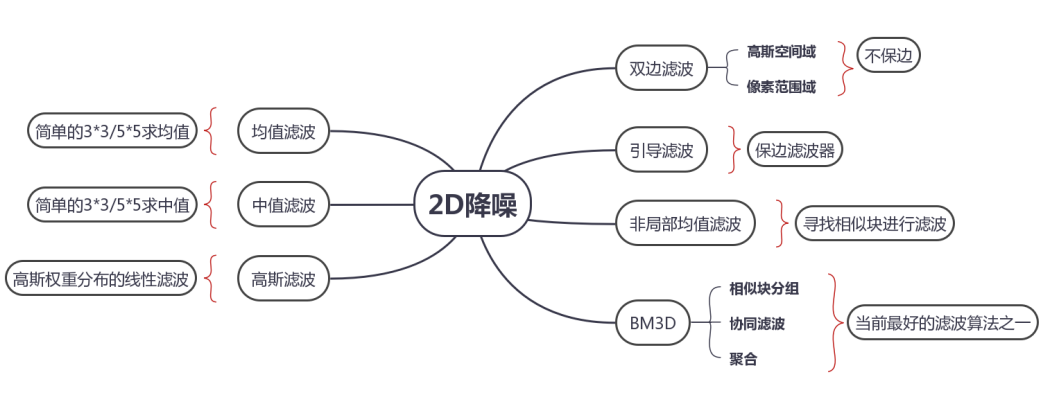

使用高級綜合HLS,開發 2D 中值濾波器算法 (HLS) 。

概述

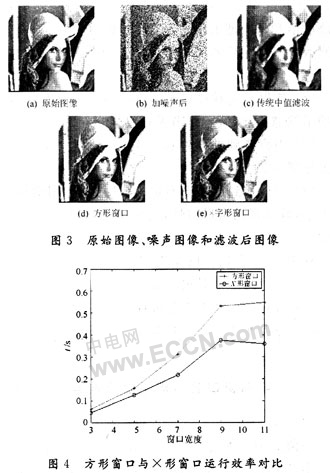

該項目包含使用高級綜合 (HLS) 的 2D 中值濾波器算法的實現。該項目的目標是在不到 3 ms的時間內對測試圖像進行去噪,同時消耗不到 25% 的可用 PL 資源。特征如下:

- 包含具有任意精度數據類型的高效數據類型管理。

- 采用 HLS 編譯指示來確保最佳系統性能。

- 通過多個測試用例進行驗證。

內容

該項目包含以下內容:

- 2D中值濾波器算法的源代碼文件

- C 仿真文件

- 協同仿真文件

- 綜合文件

- 包含干凈和有噪聲的圖像數據的 CSV 文件

- 仿真和綜合過程的屏幕截圖

設置和安裝

該項目已在 Vivado HLS 中設計和測試。要設置并運行項目:

- 克隆此倉庫:git clone

- 打開 Vivado HLS 軟件并導入項目。

- 加載包含圖像數據的 CSV 文件。

- 運行 C 仿真以確保算法正常運行。

- 進行綜合和協同仿真。

用法

將項目導入 Vivado HLS 后:

- 運行 C 仿真以驗證中值濾波器的功能。

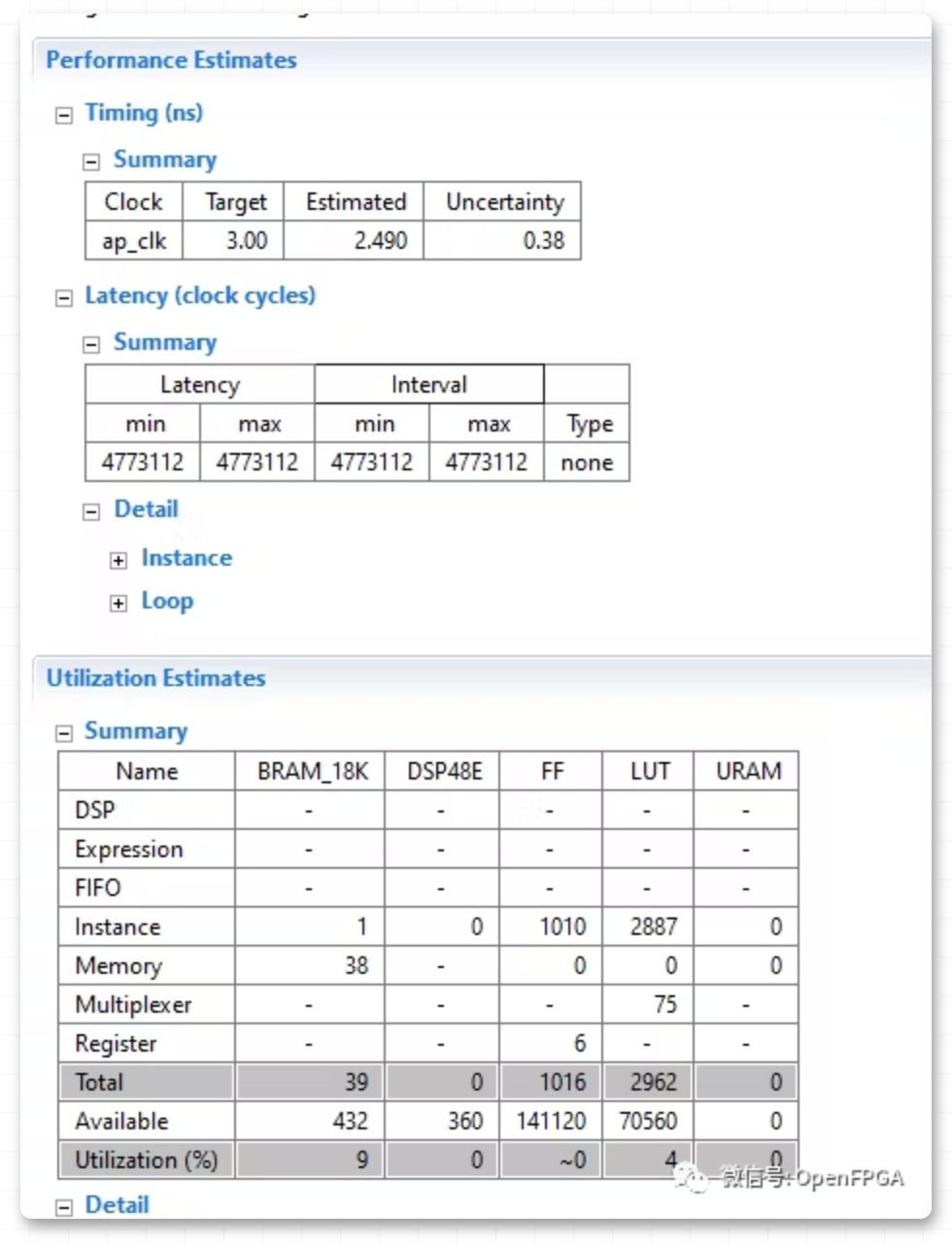

- 執行綜合過程以查看資源利用率報告并進行必要的調整。

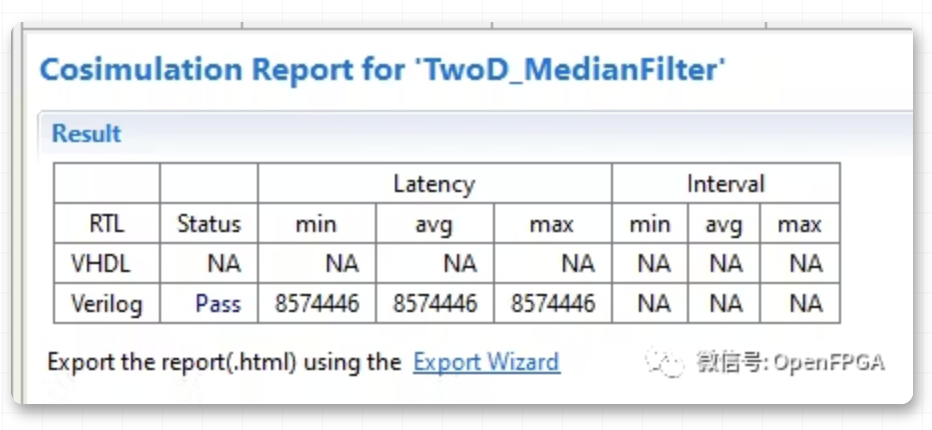

- 執行協同仿真以確保綜合設計的行為符合預期。

請注意:可能需要根據所使用的 FPGA 板調整代碼中的 HLS 編譯指示以獲得最佳性能。

最終設計應用于測試數據時,在不到 12 ms的時間內實現了去噪,總體 PL 資源利用率約為 13%。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

濾波器

+關注

關注

160文章

7727瀏覽量

177672 -

FPGA開發板

+關注

關注

10文章

122瀏覽量

31484 -

HLS

+關注

關注

1文章

128瀏覽量

24032

發布評論請先 登錄

相關推薦

基于FPGA的中值濾波算法實現

` 本帖最后由 ninghechuan 于 2017-9-1 07:04 編輯

在這一篇開篇之前,我需要解決一個問題,上一篇我們實現了基于FPGA的均值濾波算法的實現,最后的顯示效

發表于 09-01 07:04

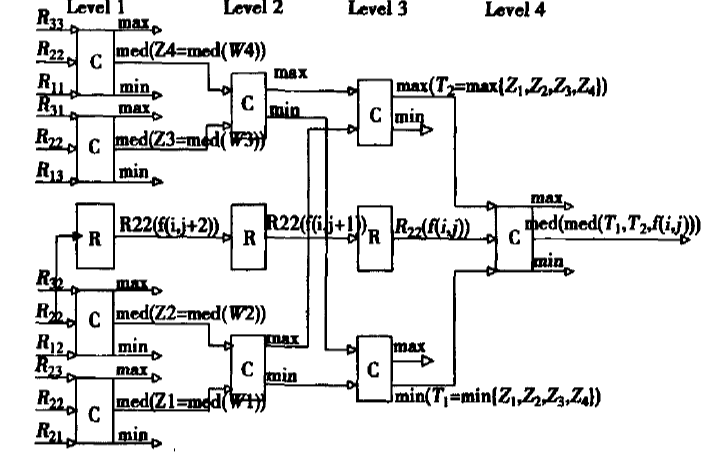

快速中值濾波的FPGA實現

中值濾波: 算法說明: 系統獲取的圖像在形成、傳輸、接收和處理的過程中,不可避免地存在著外部干擾和內部干擾。各種噪聲隨之而來,如圖像傳感器、信道傳輸、A/D轉換等所產生

發表于 03-25 15:10

?234次下載

測井圖像的多級中值濾波算法及其FPGA實現

微電阻率成像測井儀傳輸上來的地層信息數據需要濾波處理后才能真實地反映出地層中油層的信息,而中值濾波是圖像預處理中常用的技術。本文介紹了標準中值濾波

發表于 12-31 09:20

?8次下載

2D中值濾波算法的設計實現

2D中值濾波算法的設計實現

評論