什么是同步有限狀態(tài)機(jī)?

同步:所有的狀態(tài)跳轉(zhuǎn)都是在時(shí)鐘的作用下進(jìn)行

有限:狀態(tài)的個(gè)數(shù)是有限的

為什么要用狀態(tài)機(jī)?

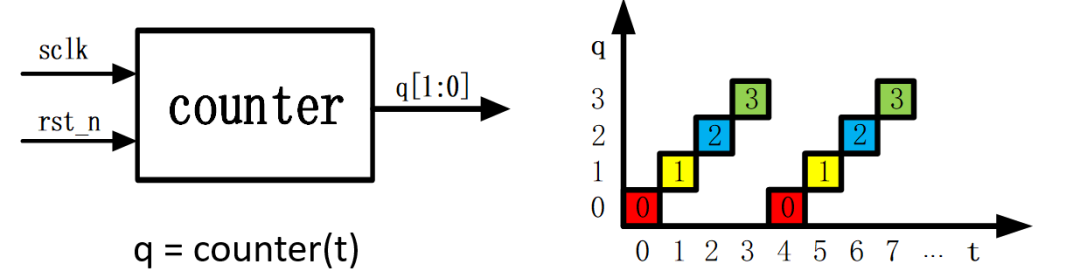

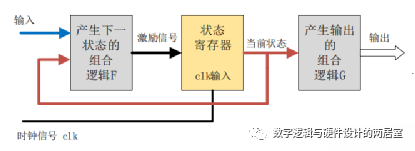

FPGA是并行處理的,如果我們想要處理具有前后順序的事件時(shí),就需要引入狀態(tài)機(jī)。狀態(tài)機(jī)的每一個(gè)狀態(tài)代表一個(gè)事件,從執(zhí)行當(dāng)前事件到執(zhí)行另一事件我們稱之為狀態(tài)的跳轉(zhuǎn)或狀態(tài)的轉(zhuǎn)移。

狀態(tài)機(jī)特別適合描述那些發(fā)生有先后順序或時(shí)序規(guī)律的事情。小到計(jì)數(shù)器大到微處理器都適合用狀態(tài)機(jī)描述。

怎么表示狀態(tài)機(jī)?

狀態(tài)機(jī)需要具備什么?

- 輸入:根據(jù)輸入確定是否需要進(jìn)行狀態(tài)跳轉(zhuǎn)

- 輸出:當(dāng)前時(shí)刻狀態(tài)要做的事情是什么

- 狀態(tài):要處理的事情

狀態(tài)機(jī)的設(shè)計(jì)步驟是怎么樣的?

- 首先分析輸入、輸出有哪些,需要多少個(gè)狀態(tài)

- 其次根據(jù)分析繪制狀態(tài)轉(zhuǎn)移圖

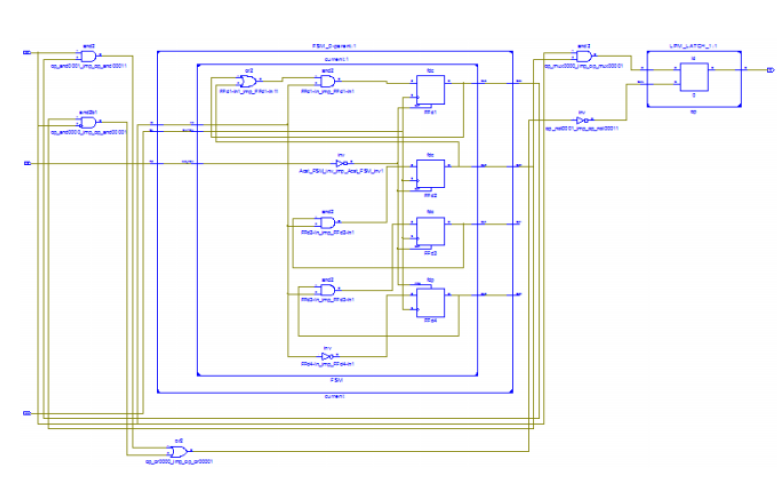

- 設(shè)計(jì)實(shí)現(xiàn)的模塊

- 狀態(tài)機(jī)代碼的編寫(xiě)

FIFO的使用

什么是FIFO?

FIFO(First In First Out)即先入先出,是一種數(shù)據(jù)緩沖器,用來(lái)實(shí)現(xiàn)數(shù)據(jù)先入先出的讀/寫(xiě)方式。FIFO有一個(gè)寫(xiě)端口和一個(gè)讀端口外部無(wú)需使用者控制地址,使用方便。

根據(jù)FIFO工作的時(shí)鐘域可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。異步FIFO是指讀/寫(xiě)時(shí)鐘不一致,是相互獨(dú)立的。

FIFO的作用是什么?

- 用于緩存數(shù)據(jù)

- 用于做多bit數(shù)據(jù)的跨時(shí)鐘域處理

- 用于做時(shí)鐘、位寬不匹配問(wèn)題的接口

如何使用FIFO?

- 在一定時(shí)間內(nèi),寫(xiě)數(shù)據(jù)的總帶寬一定要小于等于讀數(shù)據(jù)的總帶寬

- 控制好FIFO的關(guān)鍵信號(hào),讀寫(xiě)時(shí)鐘、讀寫(xiě)使能、空滿標(biāo)志信號(hào)

- FIFO一定不能寫(xiě)滿、也不能讀空,要考慮FIFO的背靠背問(wèn)題,設(shè)置好存儲(chǔ)深度

FPGA設(shè)計(jì)中的技巧

一、使能信號(hào)(en)、標(biāo)志信號(hào)(flag)、計(jì)數(shù)器(cnt)

二、模塊框圖設(shè)計(jì)——方案的確定

三、波形設(shè)計(jì)——代碼的實(shí)現(xiàn)

四、代碼規(guī)范——可復(fù)用性和效率

五、仿真調(diào)試——修改查錯(cuò)

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489 -

有限狀態(tài)機(jī)

+關(guān)注

關(guān)注

0文章

52瀏覽量

10316 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

492瀏覽量

27485 -

FIFO存儲(chǔ)

+關(guān)注

關(guān)注

0文章

103瀏覽量

5965 -

數(shù)據(jù)緩沖器

+關(guān)注

關(guān)注

1文章

5瀏覽量

1843

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SaberRD狀態(tài)機(jī)建模工具介紹(一)什么是狀態(tài)機(jī)建模

Verilog狀態(tài)機(jī)+設(shè)計(jì)實(shí)例

有限狀態(tài)機(jī)有什么類型?

什么是有限狀態(tài)機(jī)呢

有限狀態(tài)機(jī)_FSM_的實(shí)現(xiàn)

有限狀態(tài)機(jī)的建模與優(yōu)化設(shè)計(jì)

VHDL有限狀態(tài)機(jī)設(shè)計(jì)-ST

初學(xué)者對(duì)有限狀態(tài)機(jī)(FSM)的設(shè)計(jì)的認(rèn)識(shí)

如何使用FPGA實(shí)現(xiàn)序列檢測(cè)有限狀態(tài)機(jī)

基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī)介紹

如何以面向?qū)ο蟮乃枷朐O(shè)計(jì)有限狀態(tài)機(jī)

基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī)介紹

Verilog狀態(tài)機(jī)的類型

什么是同步有限狀態(tài)機(jī)?為什么要用狀態(tài)機(jī)?怎么表示狀態(tài)機(jī)?

什么是同步有限狀態(tài)機(jī)?為什么要用狀態(tài)機(jī)?怎么表示狀態(tài)機(jī)?

評(píng)論