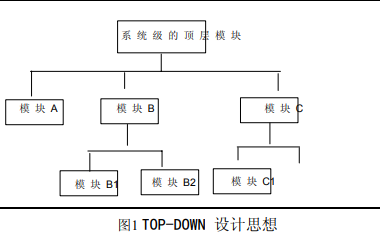

高質量6要素

高質量的verilog代碼至少需要包含以下幾個要素:可讀性、功能、性能、標準化、穩定性、可定位。

標準化:iterlaken MAC PCIE 這些模塊的設計必須要符合協議標準,能夠與其他廠商的產品進行正常對接。

可讀性:代碼是容易閱讀,是否容易理解原理

功能:功能是否正確,功能點是否全面,是否靈活可配置。

性能:讀寫、傳輸速率是否達標

穩定性:跨時鐘等是否處理細致,異常情況代碼是否能夠保持穩定,是否能夠自恢復,狀態機是否會卡住。

可定位:定位手段是否添加全面、遇到故障,是否能夠快速定位。

1、可讀性

代碼是否容易閱讀理解,需要注意代碼格式、關鍵信號命令、盡量多添加注釋。

代碼格式:代碼編寫需要采用普遍的格式、如空格的插入、if else的位置放置、特別是復雜的邏輯判斷,該斷行的需要斷行,該添加括號的地方添加括號。

信號命名:信號命名需要注意:如請求信號以req命令,響應信號ack,流控信號fc,信號命令需要通俗易懂,采用常見的縮寫。

注釋清晰:一定要多寫注釋,很多代碼時間長了,自己都看不明白了,就算能看明白,也需要花費不少時間

2、功能達標

代碼功能點是否全面。

各個功能是否能夠正常實現。

各功能是否靈活可配置,如是否具有使能開關

3、性能達標

模塊性能是否達標。設計是否已考慮各項性能指標,如數據通路常見的指標為BPS和PPS。

極限(最佳速率和最差速率)和正常場景下性能是否達標。

特殊包長場景是否已考慮。是否能夠及時處理突發數據。

4、標準化

模塊設計是否符合標準協議,如IEEE802.3 MAC 模塊設計是否符合標準,PCIE 是否能夠與其他廠商的PCIE進行對接傳輸數據,且與主機相關的各項能力結構能夠與主機正常交互。如interlaken接口是否能夠與FPGA的interlaken進行正常對接。

5、穩定性

代碼的穩定性需要關注常見的spyglass lint cdc、跨時鐘信號、代碼是否能夠自恢復。

常見spyglass lint檢查:信號位寬是否匹配,技術是否會溢出、是否產生了latch等等

跨時鐘:跨時鐘的信號是否都進行了同步處理、單bit、多bit信號是否正確同步。電平單bit、多bit數據、單bit脈沖、復位信號的同步方式各不相同,是否都正確同步了。信號同步的max_delay 延時是否符合要求。

自恢復:異常情況下,模塊是否能夠自行恢復,當異常情況消失后,模塊是否夠能夠正常工作。異常情況有:

1)不符合規定的信號輸入:輸入信號eop_in/sop_in/vld_in/error_in的有效狀態有一定的規律,不符合規律的輸入信號是否會導致模塊無法正常處理后面正確的輸入數據。

2)狀態機沒有響應:狀態機跳轉信號沒有響應,是否會導致狀態機卡死,無法跳轉到IDLE狀態。

3)關鍵信號異常跳變:偶發性強電磁反應導致的信號跳變是否會導致模塊一直無法正常工作。

6、可定位

常見的定位手段是否添加全面,比如:各類統計計數、關鍵信號狀態是否可讀、中斷信號添加是否全面。

統計計數:模塊進入數據包多少,輸出數據包多少。完成了多少次xx操作。

關鍵信號可讀:狀態機當前狀態要求可讀,關鍵信號要求可讀

中斷:fifo和ram的寫溢出、空讀、ECC、parity要求接入中斷。

教你如何書寫高質量的Verilog代碼?

-

Verilog

+關注

關注

28文章

1343瀏覽量

109980 -

時鐘

+關注

關注

10文章

1720瀏覽量

131362 -

編程

+關注

關注

88文章

3591瀏覽量

93592 -

中斷

+關注

關注

5文章

895瀏覽量

41391 -

代碼

+關注

關注

30文章

4744瀏覽量

68345

原文標題:高質量的verilog代碼是什么樣的

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog HDL入門教程

Verilog HDL入門教程

華為Verilog HDL入門教程的PDF電子書免費下載

分享一些優秀的verilog代碼 高質量verilog代碼的六要素

分享一些優秀的verilog代碼 高質量verilog代碼的六要素

評論