本文翻譯自Wikichip. https://en.wikichip.org/wiki/technology_node

技術節點[Technology Node](也稱工藝節點[Process Node]、工藝技術[Process Technology]或簡稱節點[Node])是指特定的半導體制造工藝及其設計規則。不同的節點通常對應著不同的電路世代和架構。一般來說,技術節點越小,意味著特征尺寸越小,生產出的晶體管更小,速度更快,功耗更低。

從歷史上看,工藝節點名稱指的是晶體管的一些不同特征,包括柵極長度和第一層金屬線的半節距。最近,由于各種營銷和代工廠之間的差異,這個數字本身已經失去了曾經的確切含義。最近的技術節點,如22 nm、16 nm、14 nm和10 nm,純粹是指采用特定技術制造的特定一代芯片。它與任何柵極長度或半節距無關。盡管如此,這一名稱慣例一直沿用至今,這也是領先代工廠對其節點的稱呼。

大約2017年以后,節點名稱已完全被市場營銷所取代,一些領先的代工廠含糊地使用節點名稱來代表略有改動的工藝。此外,代工廠之間晶體管的尺寸、密度和性能也不再匹配。例如,英特爾的10納米與代工廠的7納米相當,而英特爾的7納米與代工廠的5納米相當。

術語

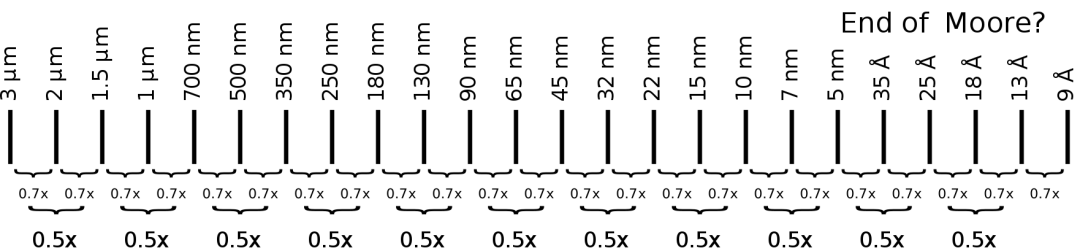

工藝節點擴展背后的驅動力是摩爾定律。要實現密度翻番,每個節點的接觸柵極間距(CPP)和最小金屬間距(MMP)大約需要縮小0.7倍。換句話說,0.7× CPP ? 0.7× MMP ≈ ? 面積。節點名稱實際上是摩爾定律驅動下的自我實現預言( self-fulfilling prophecy )。

歷史

從1960年代MOSFET首次量產到1990年代末,在半導體歷史的前35年中,工藝節點大體上是指的是晶體管的柵極長度(Lg),它也被認為是 "最小特征尺寸"。例如,英特爾0.5微米工藝的Lg=0.5μm。這種情況一直持續到1997年的0.25微米工藝,英特爾在這一時期開始使用更激進的柵極長度縮小。例如,其0.25微米工藝的柵極長度為0.20微米,同樣,其0.18微米工藝的柵極長度為0.13微米(領先一個節點)。在這些節點上,"工藝節點 "實際上大于柵極長度。

工藝節點這個術語本身可以追溯到1990年代,當時微處理器的發展主要由更高的頻率驅動,而DRAM的發展則主要由對大容量的需求驅動。由于更大的容量是通過更高的密度實現的,因此DRAM成為技術發展的驅動力。這種情況一直持續到2000年代。國際半導體技術路線圖(ITRS)為半導體行業提供了各種技術節點的指導和幫助。到2006年,隨著微處理器開始主導技術的擴展,ITRS用閃存、DRAM和MPU/ASIC的一系列獨立指標取代了這一術語。

ITRS傳統上將工藝節點定義為制造工藝中允許的第一層金屬線的最小半節距。它是用于描述和區分集成電路制造技術的通用指標。

意義的變化

在45納米工藝中,英特爾傳統平面晶體管的柵極長度達到25納米。在這一節點上,柵極長度的擴展實際上停滯了;柵極長度的任何進一步擴展都會產生不理想的結果。在32納米工藝節點之后,雖然晶體管的其他方面有所縮小,但柵極長度實際上有所增加。

隨著英特爾在其22納米工藝中引入FinFET,晶體管密度繼續增加,而柵極長度基本保持不變。這是由于FinFET的特性造成的;例如,有效溝道長度是新鰭片的函數(Weff = 2* Hfin + Wfin)。由于晶體管與過去相比發生了巨大變化,目前的命名方案失去了意義。

半節點

半節點也可追溯到1990年代,當時很容易實現超量收縮。全技術節點的線性收縮率預計為0.7倍(例如,全收縮后的130納米變為90納米)。同樣,相關的半節點也有望實現0.9倍的線性收縮。這種想法的前提是,當新的技術節點被考慮當作全節點時,代工廠的設計規則(如標準單元)需要經過提前布局,以兼容18個月后會出現半節點收縮。這樣,應對半節點收縮,只需進行各種調整,就可以實現向新工藝的無縫過渡,而不會遇到違反設計規則、時序或其他可靠性問題。請注意,封裝等某些步驟確實需要重新設計。

技術發展趨勢

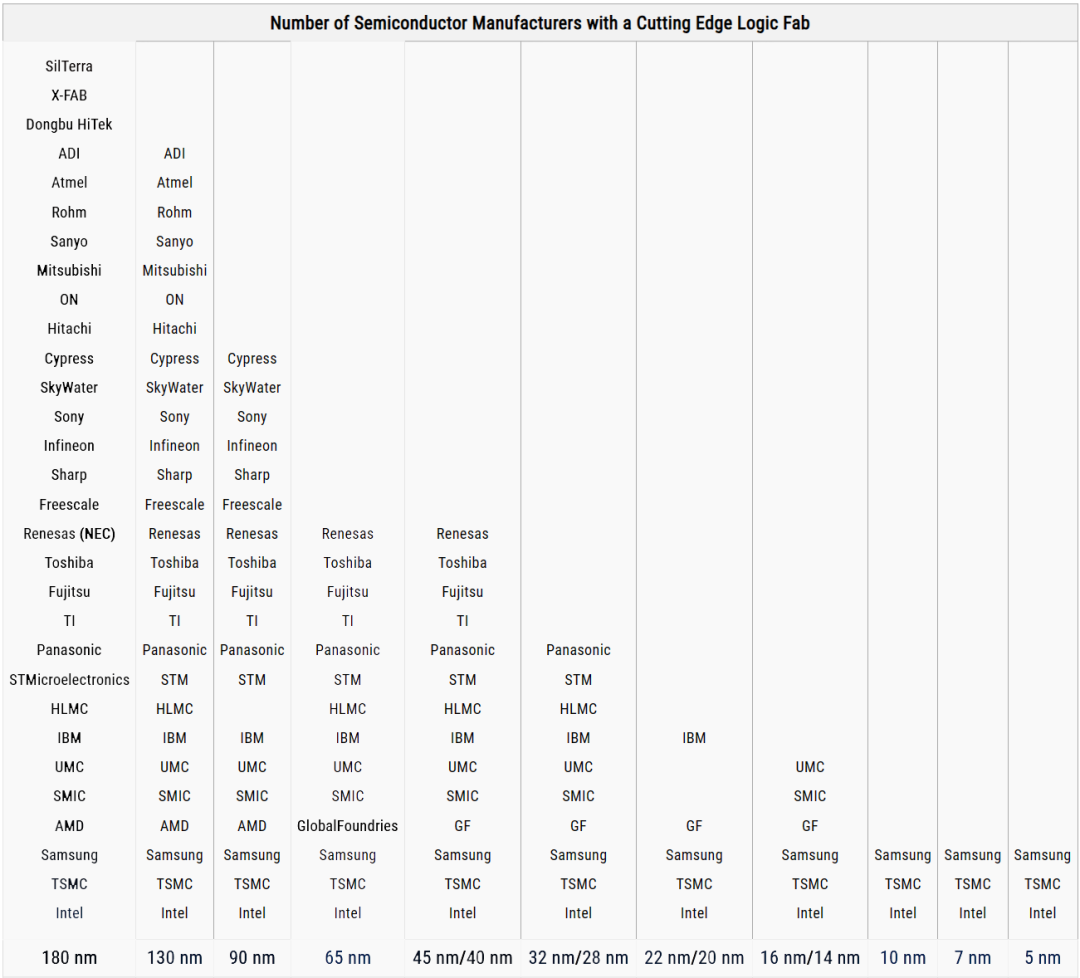

隨著收縮變得越來越復雜,需要更多的資金、專業知識和資源,能夠提供尖端制造工藝的公司數量一直在下降。截至2020年,只有三家公司有能力在最尖端的工藝上制造集成電路:英特爾、三星和臺積電。

審核編輯:劉清

-

集成電路

+關注

關注

5381文章

11385瀏覽量

360875 -

英特爾

+關注

關注

60文章

9886瀏覽量

171525 -

晶體管

+關注

關注

77文章

9634瀏覽量

137849 -

MMP

+關注

關注

0文章

2瀏覽量

6592 -

cpp

+關注

關注

0文章

10瀏覽量

2107

原文標題:EDA探索丨第24期:集成電路的幾納米代表了什么?

文章出處:【微信號:hzwtech,微信公眾號:鴻之微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路的幾納米代表了什么?

集成電路的幾納米代表了什么?

評論