文本轉自公眾號系列文章,歡迎關注

《基于“礦板”低成本學習Zynq系列》之四-第一個工程HelloWorld一下 (qq.com)

一.前言

礦板,可能一些器件都不穩定了,比如DDR,所以我們來測試下,做個壓力測試。

這一篇先測試DDR,后面再測試其他的。

參考https://mp.weixin.qq.com/s/eecigPSyHQGUIx8hwSoAtQ

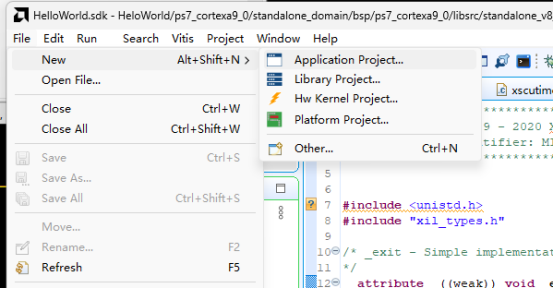

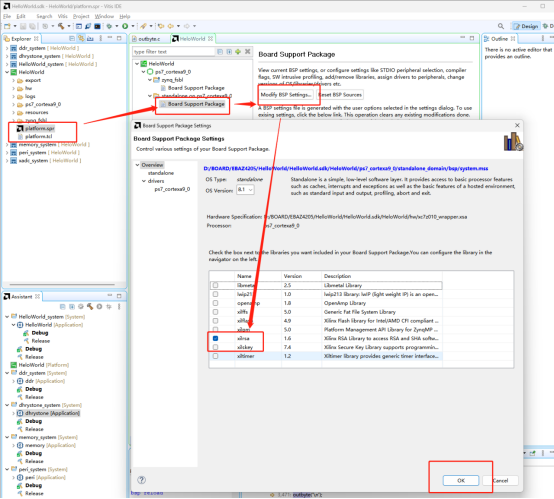

二.創建工程

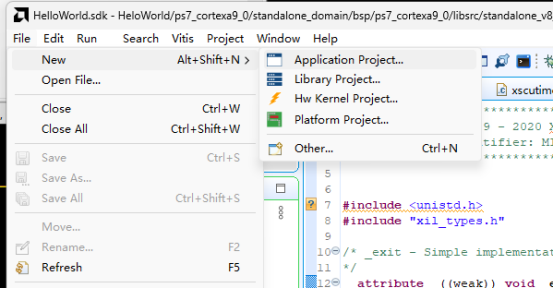

File->New->Application Project...

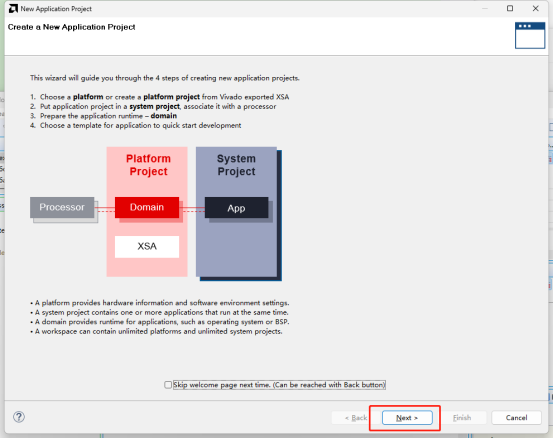

Next

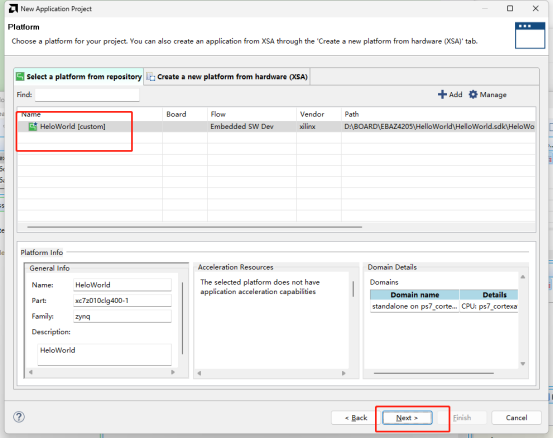

選擇之前創建的平臺,Next

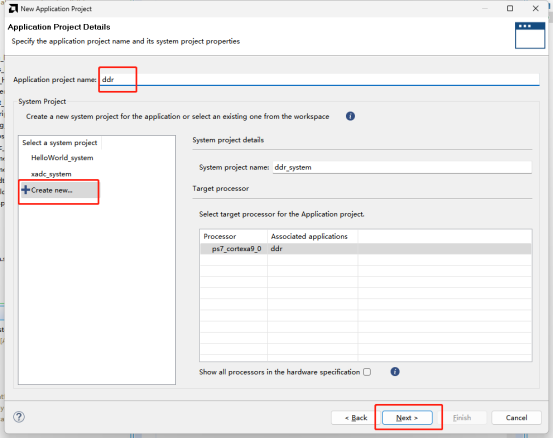

輸入工程名ddr,next

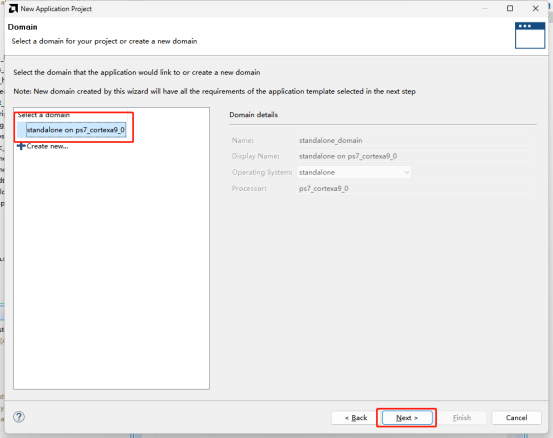

Next

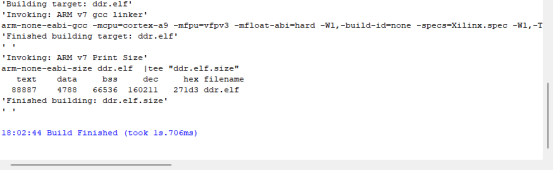

三.編譯

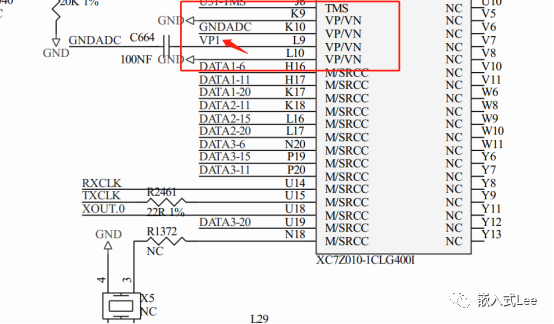

從原理圖可以看出

DDR 256M 16位

EM6GD16EWKG-12H

所以

int bus_width = 32;

改為

int bus_width = 16;

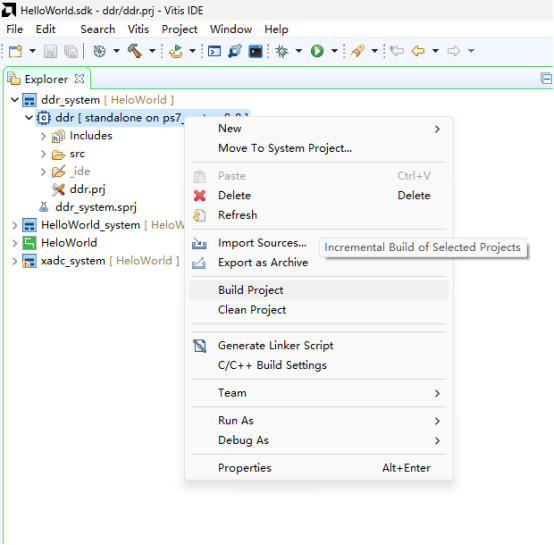

右鍵點擊DDR工程,build project

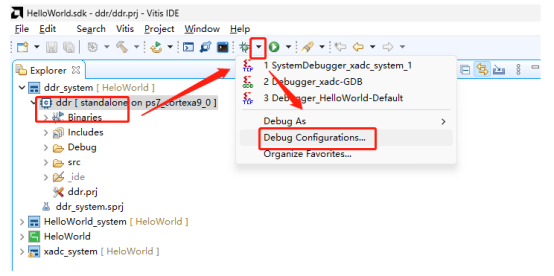

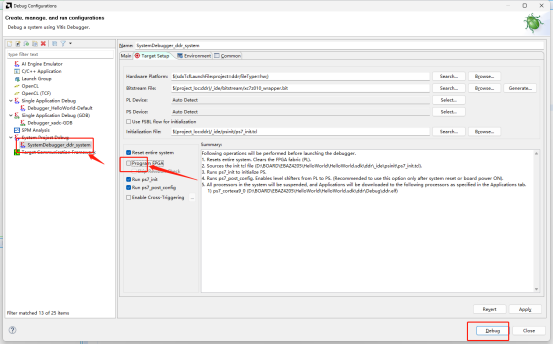

四.仿真運行

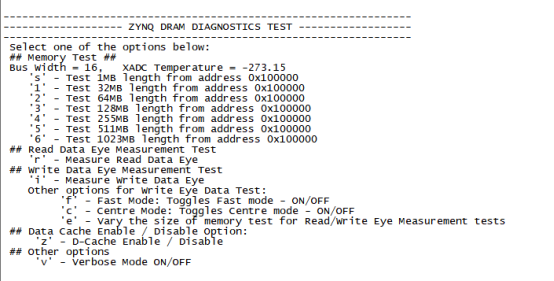

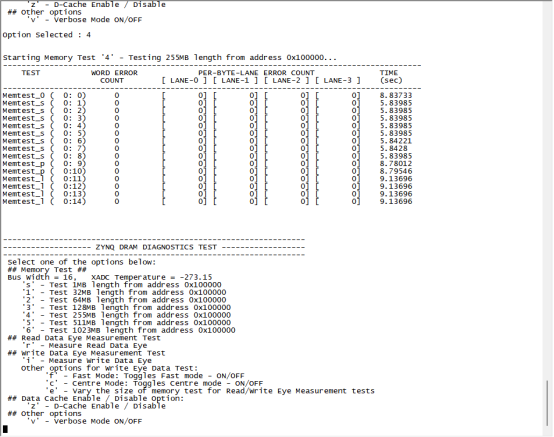

五.測試

運行后打印如下

輸入4測試255M的大小

r測試讀眼圖

i測試寫眼圖

六.總結

以上測試,確認DDR目前看還比較可靠,沒有問題。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

測試

+關注

關注

8文章

5174瀏覽量

126488 -

DDR

+關注

關注

11文章

711瀏覽量

65237 -

眼圖

+關注

關注

1文章

67瀏覽量

21114 -

編譯

+關注

關注

0文章

654瀏覽量

32813 -

Zynq

+關注

關注

10文章

608瀏覽量

47129

發布評論請先 登錄

相關推薦

請問4層板能實現zynq+ddr3嗎?

想diy一個小玩意,考慮到成本問題,只使用4層板用的主要芯片就兩個1.Xilinx ZYNQ XC7Z010-1CLG225 (15 * 15 0.8mm BGA)2.16bit DDR

發表于 01-08 22:50

使用Vitis 在EBAZ4205(ZYNQ)礦機上實現"Hello World!"

立即學習—60天FPGA工程師入門就業項目實戰特訓營(3月16日開班)Vitis是 Xilinx 最新推出的開發平臺,雖然Vitis 早就在電腦上安裝好了,但一直沒怎么使用。現在用低成本的ZYNQ

發表于 03-06 22:59

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx DDR 控制器。 DDR PHY 與電路板調試: Zynq UltraScale+ MPSoC VCU DDR 控制器采

發表于 01-07 16:02

低成本 MiniZed Zynq SoC 開發板

MiniZed Zynq SoC 開發板基于全新 Xilinx Zynq Z-7007S 器件,現可通過安富利訂購,僅需 89 美元。該開發板為單核 ARM Cortex-A9 開發人

DDR PHY 與電路板調試

UltraScale+ MPSoC VCU(H.264/H.265 視頻編解碼器)連用。

因此,調試將不同于 MIG 等傳統 Xilinx DDR 控制器。

DDR PHY 與電路板調試:

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

UltraScale+ MPSoC VCU(H.264/H.265 視頻編解碼器)連用。

因此,調試將不同于 MIG 等傳統 Xilinx DDR 控制器。

DDR PHY 與電路板調試:

發表于 02-23 06:00

?15次下載

Xilinx Zynq小試FPGA開發流程

Xilinx Zynq系列是帶有ARM Cortex-A系列CPU核的FPGA,前幾年流落到二手市場上的“礦板”就以

《基于“礦板”低成本學習Zynq系列》之六-DDR測試

《基于“礦板”低成本學習Zynq系列》之六-DDR測試

評論