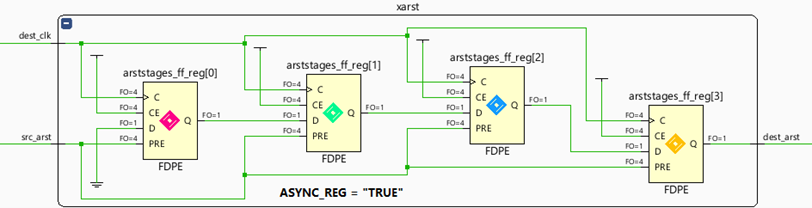

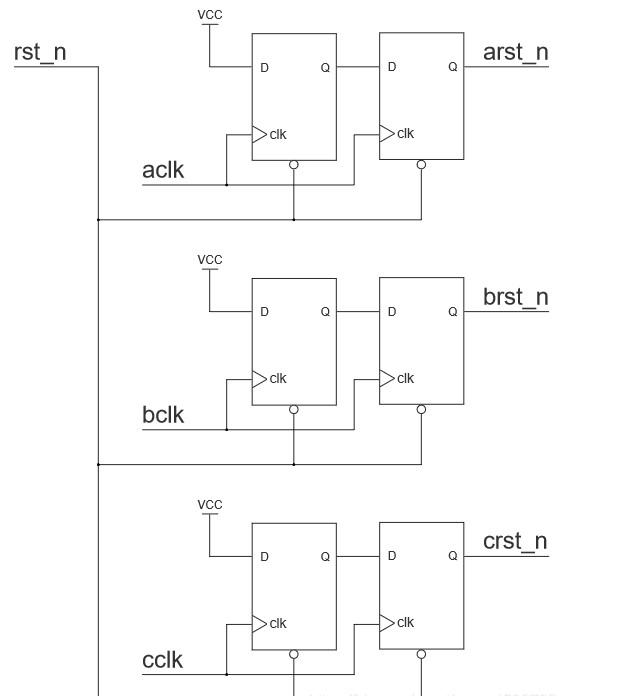

對于從FPGA外部進來的信號,我們通常采用“異步復位同步釋放的策略”,具體電路如下圖所示。圖中src_arst是輸入異步復位信號,dest_arst是同步釋放的異步復位信號,其后負載為需要異步復位的觸發器。

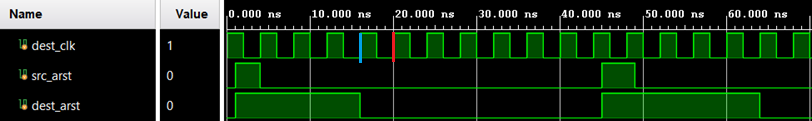

從時序關系的角度來看,結合如下仿真波形,異步復位信號在藍色標記的時鐘上升沿被釋放,所有觸發器將在紅色邊沿開始輸出D端口數據。

問題是如果后續觸發器公眾在不同的時鐘頻率下,這種方式是否仍能確保所有觸發器的異步復位信號在同一個時鐘上升沿被釋放?為便于說明,我們假定設計中有兩個時鐘,分別為100MHz和200MHz,均有同一個MMCM/PLL生成,即二者是同步時鐘(同相不同頻)。

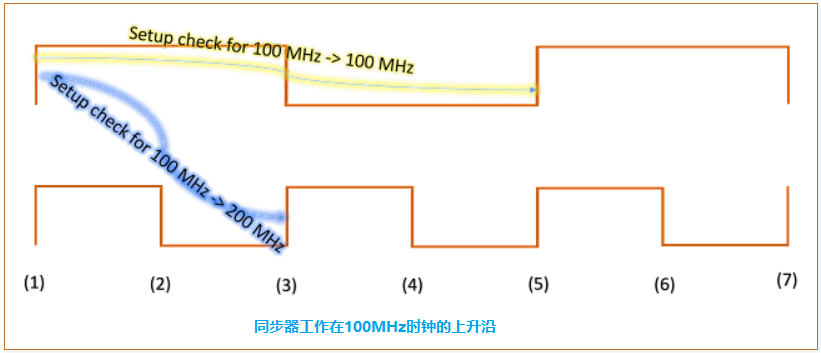

第一種情況:同步器工作在100MHz時鐘的上升沿

在這種情況下,假定異步復位在標記(1)被釋放,那么200M時鐘域下的觸發器將在標記(3)開始輸出D端數據,而100M時鐘域下的觸發器則要在標記(5)開始輸出D端數據,顯然,兩者并沒有在同一個時鐘沿下開始工作。

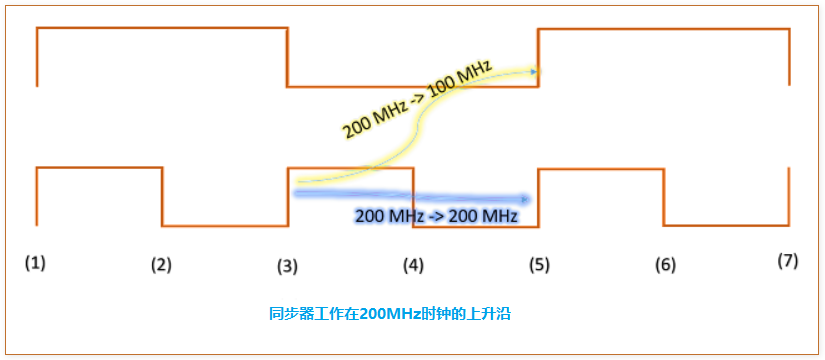

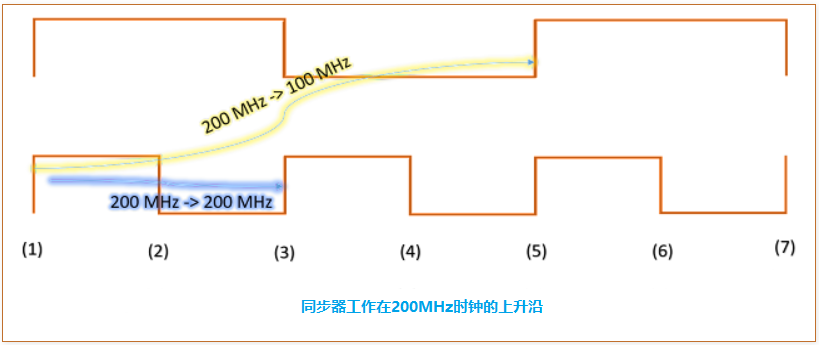

第二種情況:同步器工作在200MHz時鐘的上升沿

在這種情況下,如果異步復位是在標記(3)釋放,那么100M時鐘域下的觸發器和200M時鐘域下的觸發器都將在標記(5)結束復位,開始輸出D端口數據。

但是,如果復位是在標記(1)釋放,如下圖所示,100M時鐘域下的觸發器將在標記(5)輸出D端口數據,而200M時鐘域下的觸發器將在標記(3)輸出D端口數據。

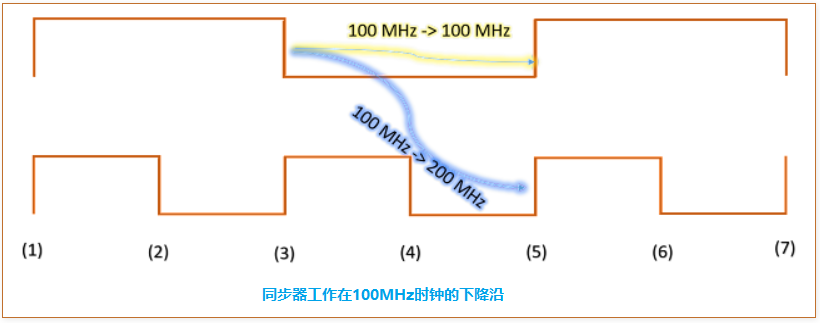

第三種情況:同步器工作在100MHz時鐘的下降沿

在這種情況下,同步器工作在100MHz時鐘的下降沿,但后續觸發器仍工作在時鐘的上升沿。如下圖所示。異步復位在標記(3)釋放,那么100M時鐘域下的觸發器將在標記(5)開始輸出D端口數據,200M時鐘域下的觸發器也在此刻輸出D端口數據,故兩者可以在同一個時刻開始釋放復位正常工作。

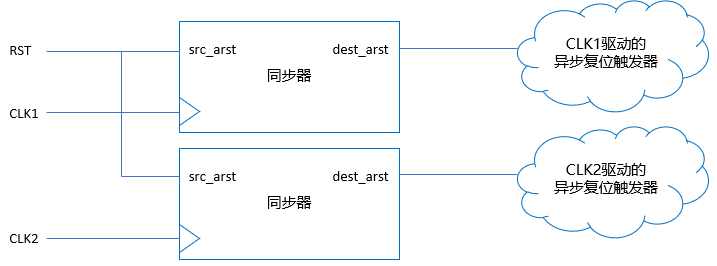

如果兩個時鐘是異步時鐘,都要使用外部提供的同一個復位信號,這時無法做到這兩個時鐘域下的觸發器實現復位信號同步釋放。這是因為這兩個時鐘之間沒有明確的相位關系,這就造成同步器引發的延遲差是不確定的。這種情況下,我們需要對每個時鐘域添加同步器,生成各自時鐘域下的復位信號,如下圖所示。

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602043 -

pll

+關注

關注

6文章

775瀏覽量

135054 -

時鐘

+關注

關注

10文章

1721瀏覽量

131378 -

觸發器

+關注

關注

14文章

1996瀏覽量

61057 -

同步器

+關注

關注

1文章

95瀏覽量

14617 -

異步復位

+關注

關注

0文章

47瀏覽量

13300 -

PLL電路

+關注

關注

0文章

92瀏覽量

6397

原文標題:異步復位同步釋放有多個時鐘域時如何處理

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

異步復位同步釋放有多個時鐘域時如何處理 異步復位同步釋放的策略

異步復位同步釋放有多個時鐘域時如何處理 異步復位同步釋放的策略

評論