來源:《半導體芯科技》雜志

美國麻省理工學院的研究人員對一種低溫生長技術進行革新,將二維材料集成到硅電路上,為制造出更密集、更強大的芯片鋪平了道路。新方法涉及直接在硅芯片頂部生長二維過渡金屬二硫化物材料層,而在傳統方法上這通常需要可能會損壞硅的高溫。

據國外媒體報道,麻省理工學院(MIT)工程師使用一種新的低溫生長和制造技術將二維(2D)材料直接集成到硅電路上,通過這種技術有望實現更密集和更強大的芯片。

新興的人工智能應用,比如生成自然人類語言的聊天機器人,需要更密集、更強大的計算機芯片。但半導體芯片傳統上是用塊狀材料制成的,這些材料是方形的三維(3D)結構,因此通過堆疊多層晶體管來實現更密集的集成非常困難。

MIT的研究人員開發了一種低溫生長工藝,可將二維材料直接集成到硅芯片上,從而實現密度更高、功能更強大的半導體。該技術繞過了之前與高溫和材料轉移缺陷相關的挑戰。它還縮短了生長時間,并允許在更大的8英寸晶圓上形成均勻的層,使其成為商業應用的理想選擇。

由超薄二維材料制成的半導體晶體管,每個只有大約三個原子的厚度,可以堆疊起來制造更強大的芯片。MIT研究人員開發的新技術,可以直接在完全制造的硅芯片上有效且高效地“生長”二維過渡金屬二硫化物(transition metal dichalcogenide, TMD)材料層,進而實現更密集的集成。

研究生Jiadi Zhu拿著一塊帶有二硫化鉬薄膜的8英寸CMOS晶圓。右邊是研究人員專門開發的外延生長爐,使他們能夠使用不損壞晶圓的低溫工藝在晶圓上“生長”一層二硫化鉬。

將二維材料直接生長到硅CMOS晶圓上是一項重大挑戰,因為該過程通常需要大約600攝氏度的溫度,而硅晶體管和電路在加熱到400攝氏度以上時可能會損壞。現在,MIT研究人員的跨學科團隊已經開發出一種不會損壞芯片的低溫生長工藝。該技術允許將二維半導體晶體管直接集成在標準硅電路之上。

過去,研究人員是先在其他地方生長二維材料,然后將它們轉移到芯片或晶圓上。這通常會導致缺陷,從而影響最終器件和電路的性能。此外,在晶圓級順利轉移材料變得極其困難。相比之下,這種新工藝在整個8英寸晶圓上生長出了平滑、高度均勻的薄層。

新技術還能夠顯著減少生長這些材料所需的時間。以前的方法生長單層二維材料需要超過一天的時間,而新方法可以在不到一個小時的時間內在整個8英寸晶圓上生長出均勻的TMD材料層。

由于其速度快和均勻性高,這項新技術使研究人員能夠成功地將二維材料層集成到比之前展示的更大的表面上。這使得他們的方法更適合用于商業應用,其中8英寸或更大的晶圓是關鍵。

“使用二維材料是提高集成電路密度的有效方法。我們正在做的就像建造一座多層建筑。如果你只有一層,這是傳統的情況,它不會容納很多人。但是隨著樓層的增加,大樓將容納更多的人,從而可以實現令人驚嘆的新事物。由于我們正在研究異質集成,我們將硅作為第一層,然后我們可以將多層二維材料直接集成在上面,”電氣工程和計算機科學研究生,關于這項新技術的論文的共同主要作者Jiadi Zhu說。該論文于2023年4月27日發表在《Nature

Nanotechnology》雜志上。Zhu與共同主要作者、麻省理工學院博士后Ji-Hoon Park共同撰寫了這篇論文;論文通訊作者Jing Kong,電氣工程與計算機科學(EECS)教授,電子研究實驗室成員;論文作者還有EECS教授兼微系統技術實驗室(MTL)主任Tomás Palacios;以及麻省理工學院、麻省理工學院林肯實驗室、橡樹嶺國家實驗室和愛立信研究中心的其他人。

1具有巨大潛力的超薄材料

研究人員關注的二維材料二硫化鉬具有柔韌性、透明性,并具有強大的電子和光子特性,使其成為半導體晶體管的理想選擇。它由夾在兩個硫(化物)原子(層)之間的單原子鉬層組成。

在表面上以良好的均勻性生長二硫化鉬薄膜通常是通過稱為金屬有機化學氣相沉積(MOCVD)的工藝完成的。六羰基鉬和二亞乙基硫是含有鉬原子和硫原子的兩種有機化合物,它們在反應室內蒸發并被加熱,在那里它們“分解”成更小的分子。然后它們通過化學反應連接起來,在表面形成二硫化鉬鏈。

但是分解這些被稱為前體的鉬化合物和硫化合物需要550攝氏度以上的溫度,而當溫度超過400攝氏度時,硅電路就會開始受到損害。

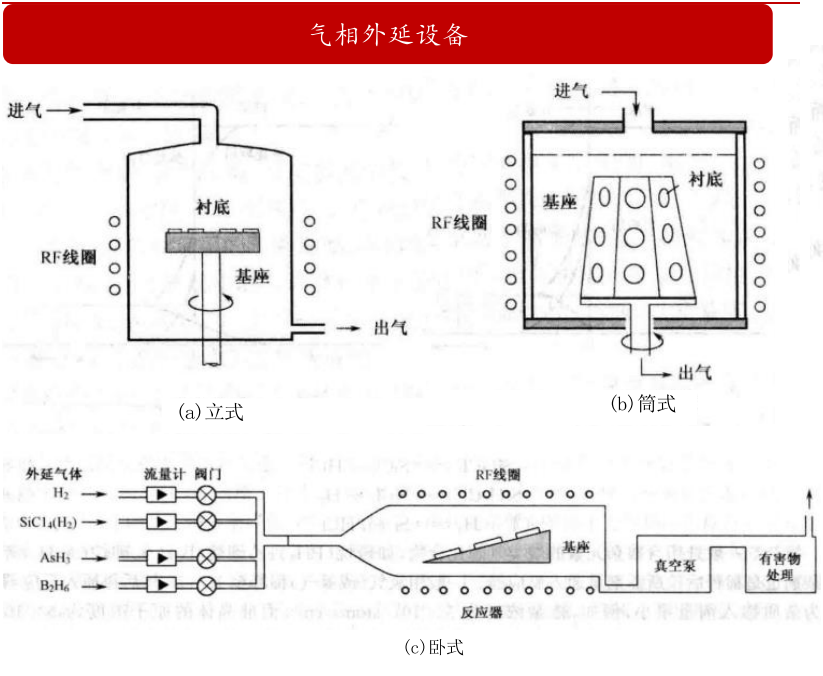

因此,研究人員開始跳出框框思考——他們為金屬有機化學氣相沉積(MOCVD)工藝設計并建造了一個全新的外延生長爐。

爐子的烘箱由兩個腔室組成,前部是低溫區,放置硅片,后部是高溫區。汽化的鉬和硫前體被泵入生長爐。鉬停留在低溫區域,溫度保持在400攝氏度以下——熱到足以分解鉬前體,但又不會熱到損壞硅芯片。

硫前體流入高溫區域,并在那里分解。然后它流回低溫區,在那里發生在晶圓表面生長二硫化鉬的化學反應。“你可以把分解想象成制作黑胡椒——你有一整粒胡椒,然后把它磨成粉末。所以,我們在高溫區粉碎和研磨辣椒,然后粉末流回低溫區,”Zhu解釋道。

2更快的生長和更好的均勻性

該工藝有一個問題:硅電路通常將鋁或銅作為頂層,因此芯片可以在安裝到印刷電路板上之前連接到封裝或載體。但是硫會導致這些金屬硫化,就像一些金屬暴露在氧氣中會生銹一樣,這會破壞它們的導電性。研究人員通過首先在芯片頂部沉積一層非常薄的鈍化材料來防止硫化。然后他們可以打開鈍化層再進行連接。

他們還將硅片垂直放置到爐子的低溫區域,而不是水平放置。通過垂直放置,兩端都不會太靠近高溫區域,因此晶圓的任何部分都不會被熱量損壞。此外,鉬和硫氣體分子在撞擊垂直芯片時會旋轉,而不是流過水平表面。這種旋轉循環效應促進了二硫化鉬的生長,并提高了材料的均勻性。

除了產生更均勻的沉積層外,他們的方法也比其他MOCVD工藝快得多。他們可以在不到一個小時的時間內生長一層,而通常MOCVD生長過程至少需要一整天。MIT使用最先進的MIT.Nano設施,他們能夠在8英寸硅晶圓上生長高度均勻的優質材料,這對于需要更大晶圓的工業應用尤為重要。

“通過縮短生長時間,該工藝效率更高,并且可以更容易地集成到工業制造中。此外,這是一種與硅兼容的低溫工藝,有助于將二維材料進一步推進到半導體行業中。”Zhu說。

未來,研究人員希望微調他們的技術,并用它來生長多層堆疊的二維晶體管。此外,他們還想探索這種低溫生長工藝在柔性表面(如聚合物、紡織品甚至紙張)的應用。這可能會實現將半導體集成到衣服或筆記本等日常用品上。

這項工作在單層二硫化鉬材料的合成技術方面取得了重要進展,在8英寸規模的低溫生長能力使這種材料與硅CMOS技術的后端集成成為可能,為其未來的更多電子應用鋪平了道路。

這項工作部分由MIT士兵納米技術研究所、國家科學基金會綜合量子材料中心、愛立信、MITRE、美國陸軍研究辦公室和美國能源部資助。該項目也得到TSMC University Shuttle的支持。

-

芯片

+關注

關注

453文章

50403瀏覽量

421806 -

半導體

+關注

關注

334文章

27014瀏覽量

216292

發布評論請先 登錄

相關推薦

美國 inTEST 高低溫沖擊熱流儀助力半導體芯片研發

周星工程研發ALD新技術,引領半導體工藝革新

半導體發展的四個時代

半導體發展的四個時代

芯片制造工藝:晶體生長基本流程

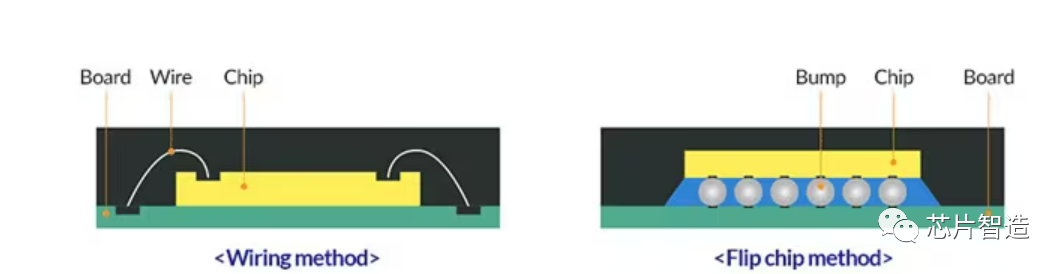

半導體封裝工藝面臨的挑戰

氮化鎵半導體芯片和芯片區別

半導體封裝的作用、工藝和演變

新型低溫生長工藝改變半導體芯片技術

新型低溫生長工藝改變半導體芯片技術

![[<b class='flag-5'>半導體</b>前端<b class='flag-5'>工藝</b>:第二篇] <b class='flag-5'>半導體</b>制程<b class='flag-5'>工藝</b>概覽與氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

評論