本文介紹基于 dsPIC33CK256MP508 實現的三相交錯 LLC PWM發波邏輯,該發波邏輯充分利用了 dsPIC33C 系列MCU強大的“支持精細邊沿定位的高分辨率PWM”外設,諸如PWM發生器(PG)的ADC觸發信號2分頻,PCI同步功能和PWM事件輸出機制。同時也開啟了PG5的同步中斷(此中斷建議具有最高優先級)。

1. PWM發波邏輯說明

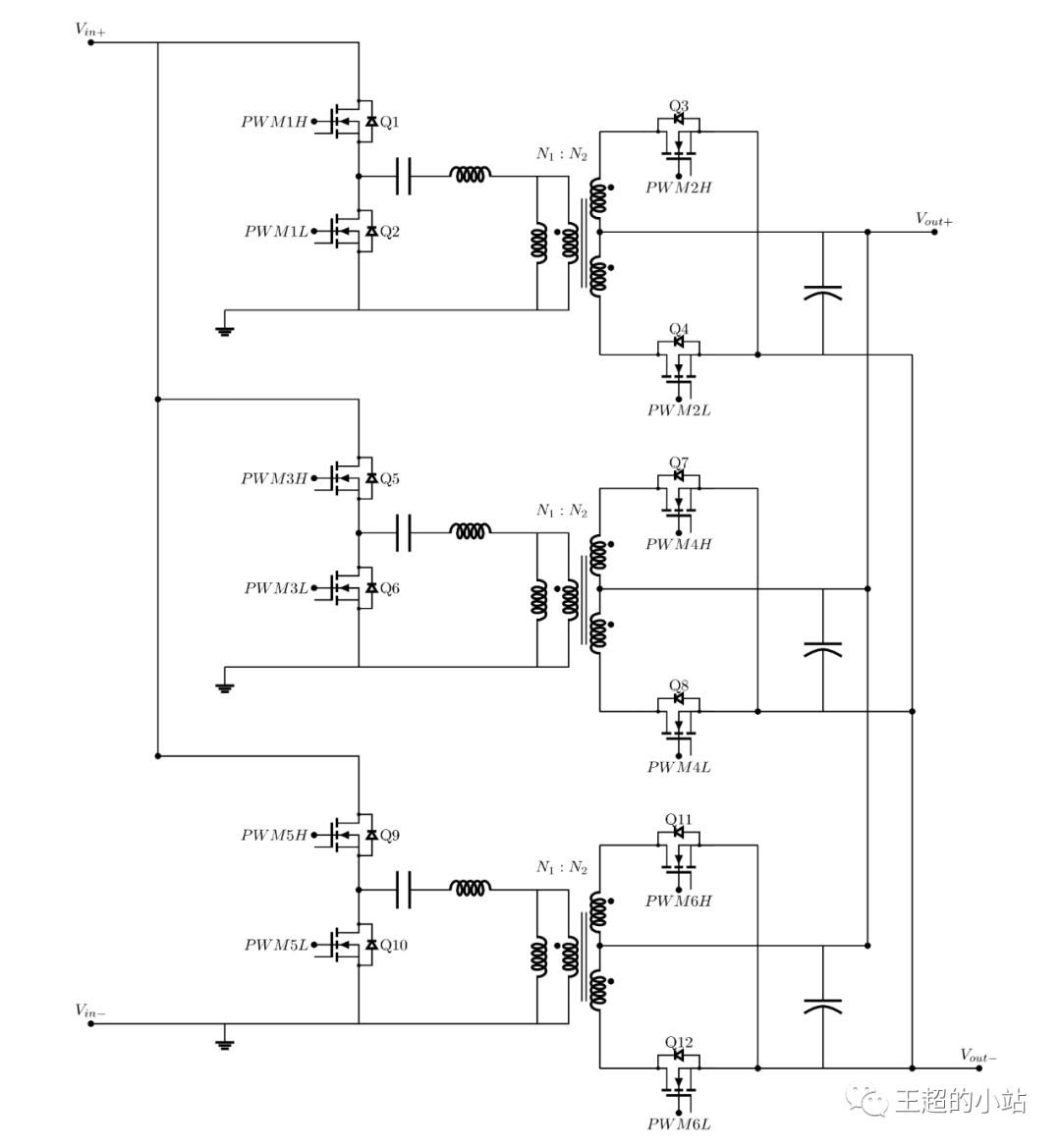

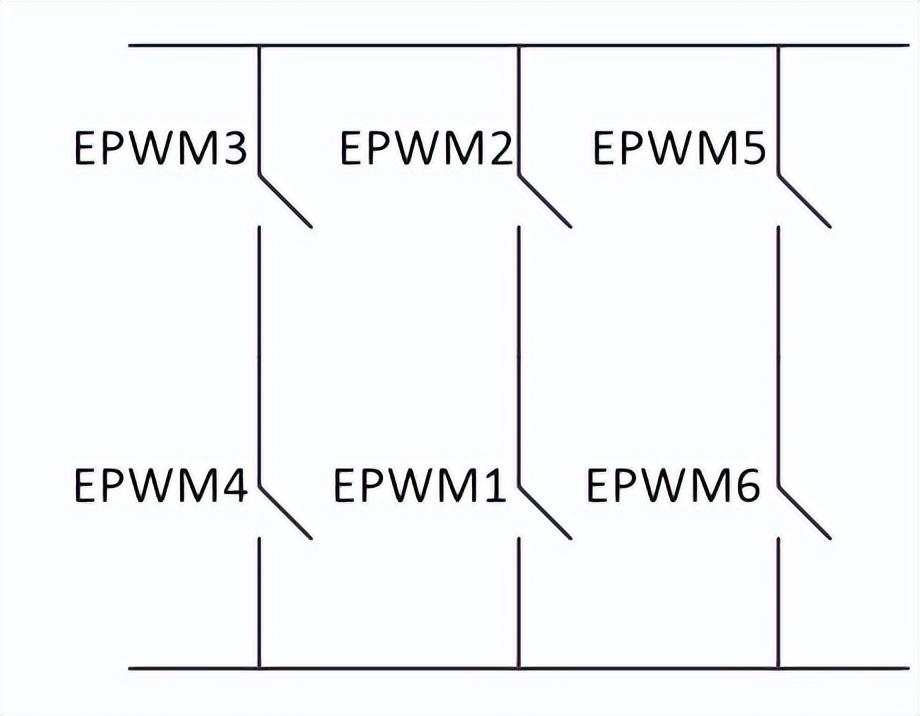

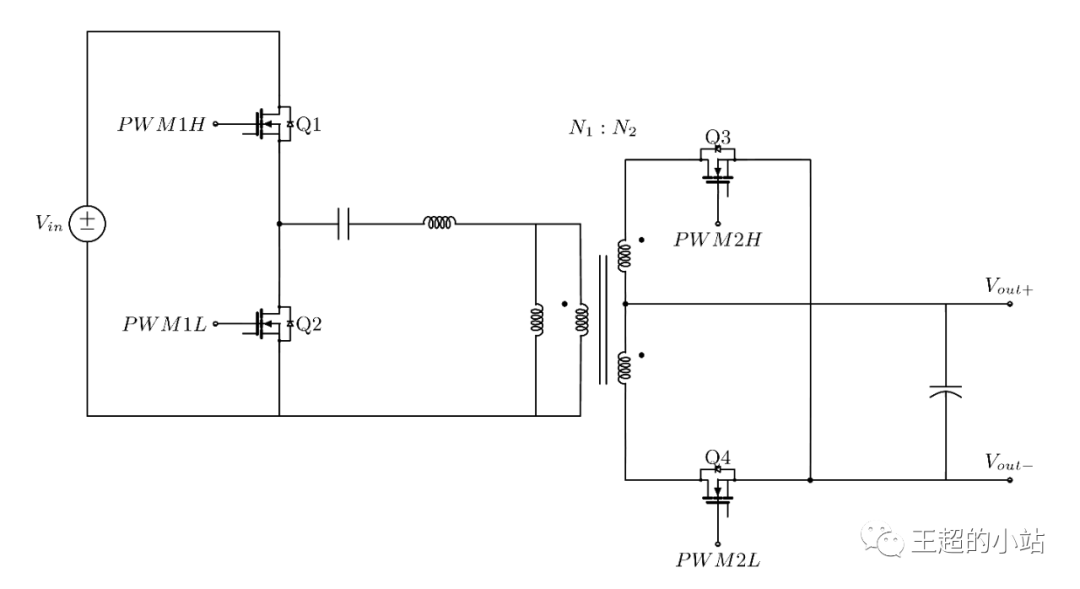

三相交錯帶同步整流的半橋LLC拓撲結構示意如下,需要6對PWM波。對于dsPIC33CK256MP508 可以用PG1、PG3和PG5作為主管PWM驅動,PG2、PG4和PG6作為同步管PWM驅動。

圖 1 - 三相交錯LLC拓撲示意

1.1 PWM外設基礎知識回顧

在具體研究PWM發波邏輯之前,需要了解下本文用到的dsPIC33C 系列MCU“支持精細邊沿定位的高分辨率PWM ^[2]^ ”外設的一些基礎知識。

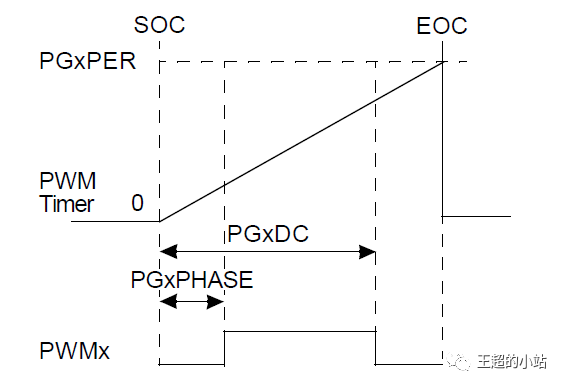

- PWM模式 - 獨立邊沿PWM模式

- PGxPHASE:確定定時器計數器周期開始后的PWM信號上升沿位置,一般主管PGxPHASE賦值為0,而對應于主管的同步整流管靠PGxPHASE值實現相應的相位偏移。

- PGxDC:確定定時器計數周期開始后的PWM信號下降沿位置。

- PGxPER:確定PWM定時器計數周期的結束位置。

圖 2 - 獨立邊沿PWM模式

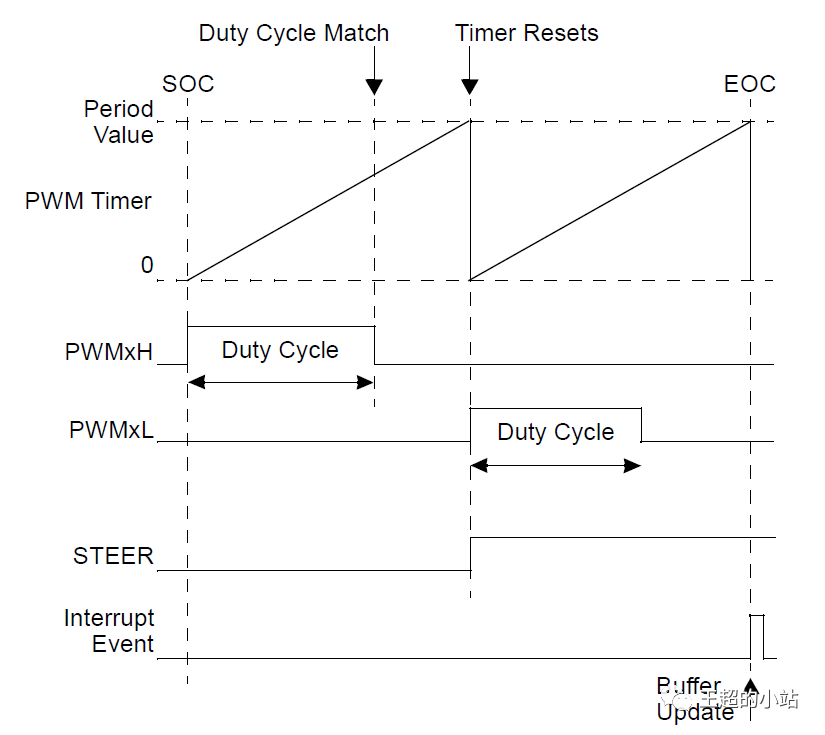

- 輸出模式 - 推挽輸出模式

推挽輸出模式在接收到SOC觸發信號時,都會將PWM周期重復兩次。由于推挽模式下不能使用死區,所以在獨立邊沿PWM模式下可以給PGxDC一個小于PGxPER值,以實現死區功能。

圖 3 - 推挽輸出模式

- ADC觸發信號

每個PWM發生器可生成兩個ADC觸發信號:ADC觸發信號1和ADC觸發信號2,同時ADC觸發信號1輸出可以使用ADTRPS<4:0>控制位(PGxEVTL<15:11>)進行后分頻,以降低ADC轉換的頻率。

- PWM事件輸出

PWM事件輸出功能提供了一種用于將各種PWM信號和事件與其他外設和外部器件接口的機制。本文LLC PWM發波邏輯的錯相就會用到將ADC觸發信號1的2分頻送給PWM事件輸出,然后相關PWM發生器與該事件進行同步。

- 同步PCI

同步模塊是唯一可啟動周期開始的PCI模塊,可用作SOCS<3:0>(PGxCONH<3:0>)多路開關的輸入,這里用于相關PWM發生器與PWM事件的同步操作,完成錯相功能。

- 觸發模式

PWM發生器提供了兩種觸發模式,用于確定如何使用SOC觸發信號,分別為單觸發模式和可重觸發模式,使用TRGMOD<1:0>(PGxCONH<7:6>)選擇觸發模式,因用了PCI同步功能,這里需要選擇重觸發模式,以防止SOC觸發信號丟失。

- 數據緩沖

PGxPER、PGxPHASE、PGxDC和PGxTRIGA等寄存器都是有緩沖的,本文這里選擇在下一個PWM周期開始時真正更新寄存器。只要在PG1新周期開始前完成對PG1~PG6的相關寄存器更新,就可以保證半橋LLC所有PG的正確同步。

1.2 PWM發波邏輯實現

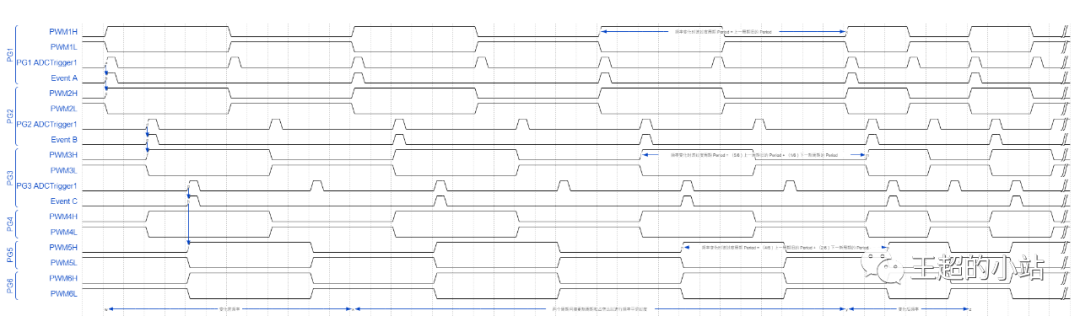

在回顧了PWM外設的基礎知識后,開始看一下半橋LLC 三相交錯PWM發波的具體實現,示意波形見圖4 。這里忽略了死區和同步整流管相對于主管的相位偏移,其他詳細說明如下。

圖 4 - PWM發波邏輯波形示意

- PG1~PG6配置為獨立邊沿推挽輸出模式。

- PG1采用SOC自觸發模式,PG2采用PCI同步功能。PG1的ADC觸發信號1經2分頻送給PWM事件A(PG1的ADC觸發信號1在定時器值等于PG1TRIGA時產生),PG2經PCI同步功能與PWM事件A同步,這就保證了PG1和PG2的相位同步一致。

- PG3和PG4采用SOC PCI同步功能,PG2的ADC觸發信號1經2分頻送給PWM事件B(PG2的ADC觸發信號1在定時器值等于PG2TRIGA時產生),PG3和PG4經PCI同步功能與PWM事件B同步,這就保證了PG3和PG4與PG2的相位相差60°。

- PG5和PG6采用SOC PCI同步功能,PG3的ADC觸發信號1經2分頻送給PWM事件C(PG3的ADC觸發信號1在定時器值等于PG3TRIGA時產生),PG5和PG6經PCI同步功能與PWM事件C同步,這就保證了PG5和PG6與PG3的相位相差60°。

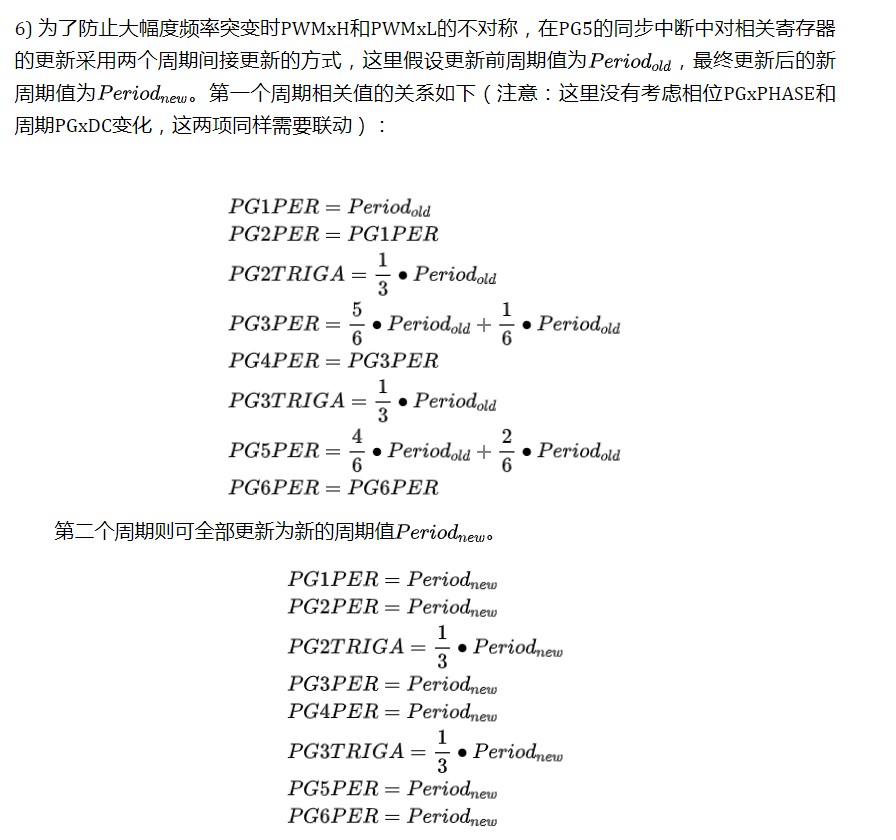

- PG5開啟PCI同步中斷,此中斷優先級需高于控制中斷,在該中斷中給PG1~PG6的相關寄存器賦值,保證在PG1的下一周期開始時刻所有寄存器統一更新。

2. 開發與驗證

2.1 開發環境說明

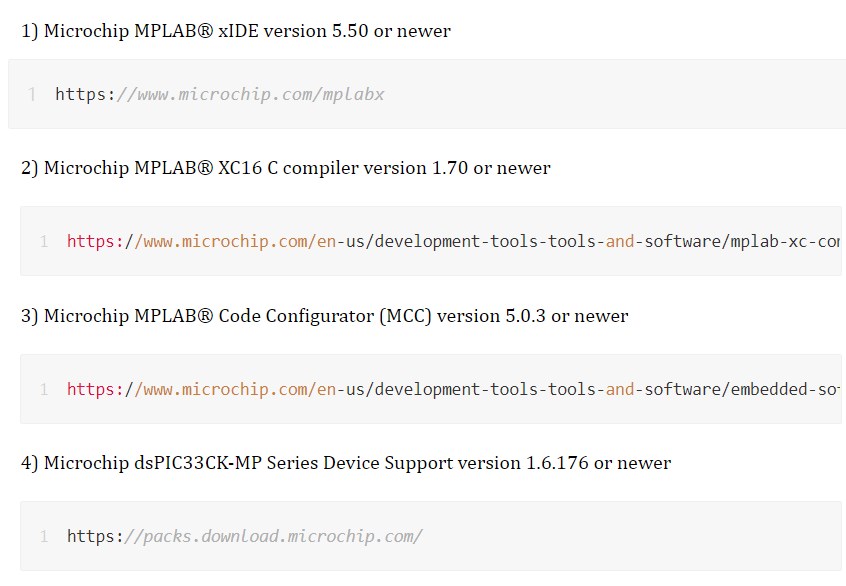

2.1.1 軟件開發環境

相關軟件開發版本情況說明如下。

2.2 軟件工程創建

您可以直接從如下Gitee鏈接下載完整的測試工程,參見doc目錄下的README.pdf可以一步一步從零開始完成該搭建工程。

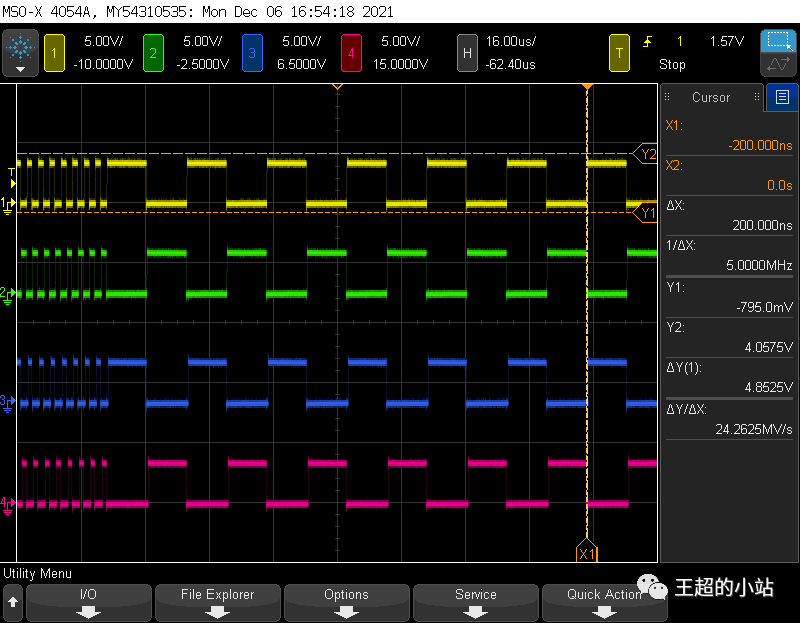

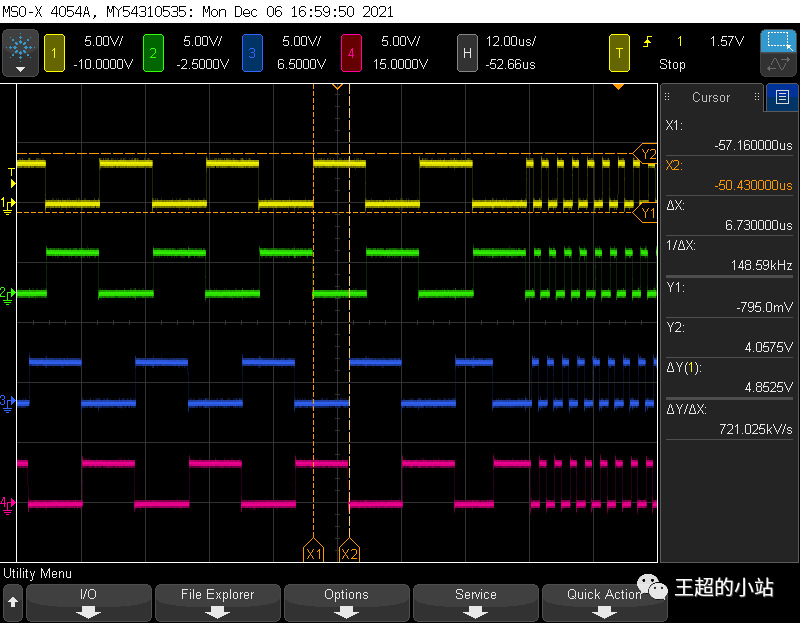

2.3 發波邏輯驗證

軟件經編譯并燒錄到dsPIC33CK256MP508后可以詳細觀察相關的PWM波形。PWM1H、PWM1L、PWM2H、PWM2L的波形關系如圖6,在頻率突變時也能很好的保證推挽輸出正負半波的對稱性。對應的PWM2H、PWM2L、PWM3H、PWM3L 和 PWM5H、PWM5L、PWM6H、PWM6L的波形關系也與圖6一致。

圖 6 - CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

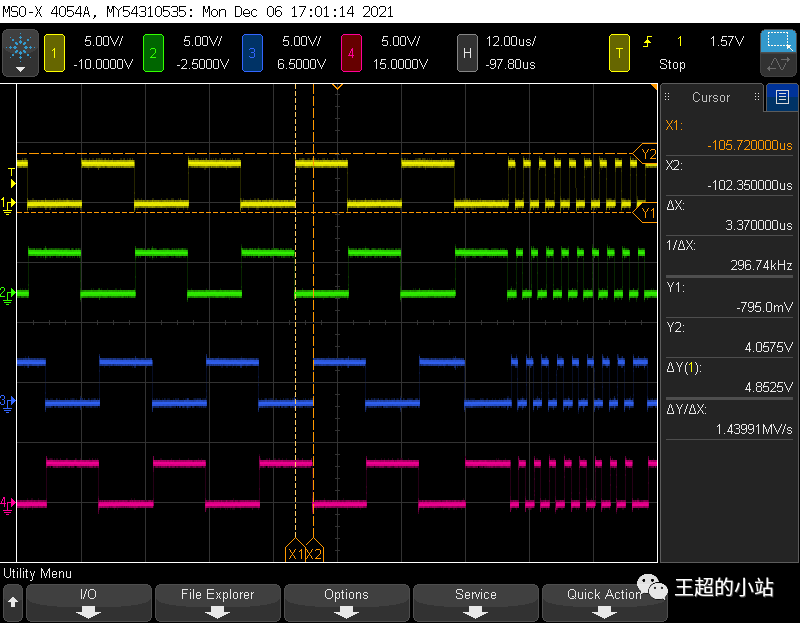

PWM1H、PWM1L、PWM3H、PWM3L的波形關系如圖7,PG3滯后PG1 60°。

圖 7 - CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

PWM1H、PWM1L、PWM5H、PWM5L的波形關系如下,PG5滯后PG1 120°。

圖 8 - CH1: PWM1H, CH2: PWM1L, CH3: PWM3H, CH4: PWM3L

-

寄存器

+關注

關注

31文章

5322瀏覽量

120019 -

緩沖器

+關注

關注

6文章

1919瀏覽量

45450 -

PWM發生器

+關注

關注

0文章

14瀏覽量

8854 -

LLC電源

+關注

關注

0文章

23瀏覽量

5177 -

PWM驅動

+關注

關注

0文章

28瀏覽量

1195

發布評論請先 登錄

相關推薦

Microchip dsPIC33CK256MP508-IPT 汽車 ISELED氛圍燈方案介紹

使用C2000 MCU的數控式兩相交錯LLC諧振轉換器設計

基于FPGA實現三相SVPWM

Microchip全新dsPIC33CH512MP508雙核DSC可為程序存儲器

dsPIC33CH512MP508系列閃存編程規范

dsPIC33CH512MP508通用接插模塊(PIM)信息手冊

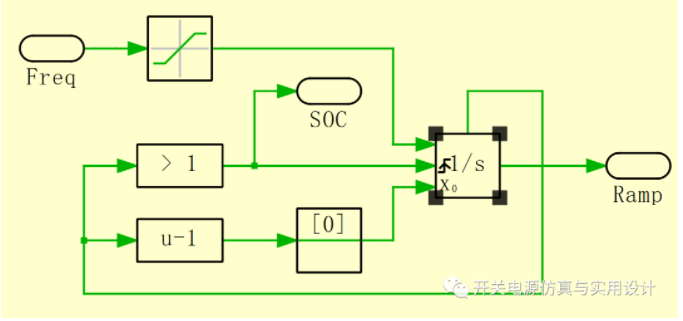

三相LLC的閉環仿真模型的實現方法

dsPIC33CH128MP508接插模塊(PIM)信息手冊

dsPIC33EPXXXGS70X/80X到dsPIC33CK256MP508的移植與性能增強指南

基于dsPIC33CK256MP508實現的三相交錯LLC PWM發波邏輯

基于dsPIC33CK256MP508實現的三相交錯LLC PWM發波邏輯

評論