今天介紹的是使用FPGA做OFDM的調制。

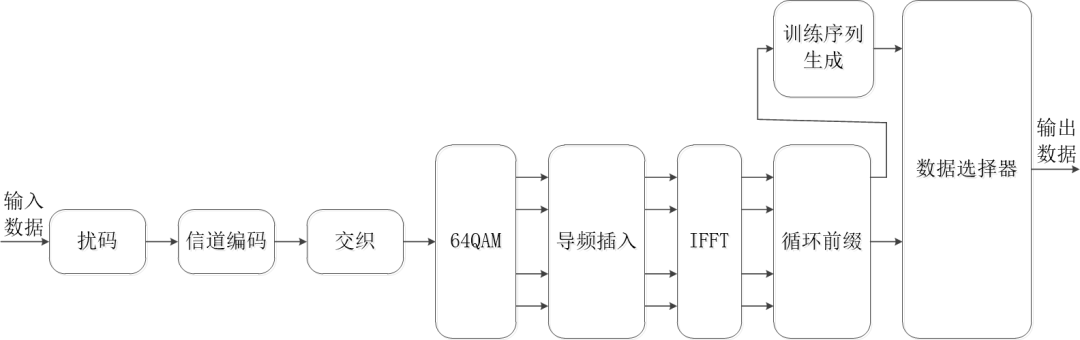

首先是OFDM調制的原理圖,輸入數據在輸入系統后首先會經過擾碼環節,在數字通信中數據中長連的“0”或“1”序列會對接收機的位同步產生重要影響,通過對要發送的數據進行擾碼操作,可以解決其對接收機同步的影響。擾碼器的實質是一個反饋的移位寄存器,輸出結果是一個m序列,將輸出的m序列域輸入的數據進行異或運算,從而將輸入的數據攪亂。

擾碼模塊根據使用的生成多項式完成對輸入數據的擾碼操作。這里使用的擾碼器是通過一個7位的反饋移位寄存器來實現的,使用的擾碼器生成多項式為:

上圖為擾碼器的硬件實現結構圖,該擾碼器輸出序列的周期為127,首先將擾碼器的初始值設置為1011101,每來一個時鐘周期將擾碼器的值右移一位,同時將第七位和第四位進行異或運算,將異或的結果作為最低位的值。同時也將得到的結果和輸入的數據分別進行異或運算,從而實現對輸入數據的擾碼操作。

擾碼器程序如下所示:

s_start為啟動信號,s_coder為7位移位寄存器,s_yz為第七位和第四位異或后的結果,當時在程序中因為順序問題我寫的是s_coder[0]和s_coder[3]。s_out為移位寄存器s_coder[0]的輸出,data_in為輸入數據,data_out為輸入數據data_in與移位寄存器輸出s_out異或運算的結果,即為擾碼后的輸出。

這里因為我沒做解調所以省去了信道編碼部分,在需要添加冗余的部分我才用補零來進行補充。

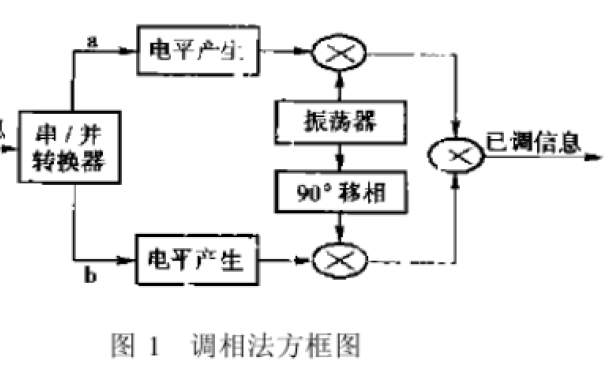

對于64QAM調制,如下圖所示為64QAM調制原理圖

這里的2到8電平轉換即為星座映射(8電平為-1,-3,-5,-7,1,3,5,7)。

對于64QAM的星座圖,星座圖中每一個點都由6bit數據表示,所以在程序中每6bit數據映射一次,下圖為verilog仿真圖。

s_start為起始信號,data_in為擾碼之后的輸入64QAM調制的信號data_index為存儲輸入的6bit數據,cnt為計數器,data_index每輸入一個數據cnt自加一次;index為計算6bit數據后對應的映射狀態,data_i和data_q為根據(index)的映射結果I/Q信號。這里我是根據狀態機來寫的,index為6bit信號的計算結果,然后根據index的大小來描寫狀態機進行映射。最后將data_i和data_q的結果存儲到fifo中,即圖中的data_fifo_in。

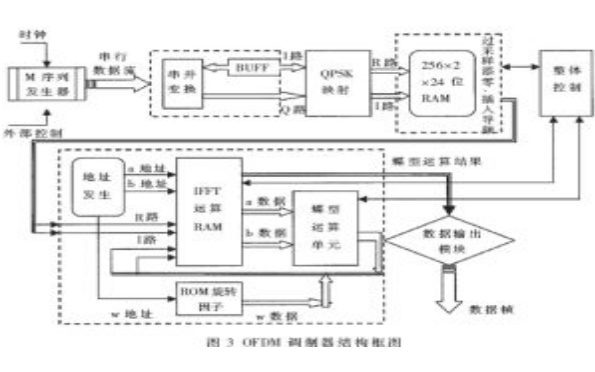

在FPGA上已經完成了星座映射后將I、Q信號送入fifo中存儲,然后通過RAM地址進行加冗余以及添加導頻,從而將一個OFDM符號中星座映射后的48個數據增加至128個數據,數據都寫入RAM,然后通過地址讀取RAM中的數據送入IFFT變換的輸入端口,以及正常輸出,在FPGA上實現頻域至時域的轉換。

下圖中data_i和data_q為星座映射后得到I、Q數據,data_fifo_in為寫入fifo的數據,由圖二可以看出,data_fifo_in的前八位為data_i,data_fifo_in的后八位為data_q。

下圖便是將數據寫入RAM,并通過地址讀寫增加冗余以及插入導頻。rd_en為讀取fifo數據使能,data_fifo_out為讀取的fifo數據。ram_en為RAM使能,ram_wea為高電平時向RAM中寫入數據,ram_wea為低電平時向RAM中讀取數據,ram_addr為寫入/讀取數據的地址。data_ram_in為寫入ram中的數據,增加的冗余為前38個寫入的數據為0以及后37個寫入數據為0。中間插入四個導頻。

在前38個寫入數據0后便開始寫入fifo中的數據,在地址為37時(0~37)打開fifo的讀使能(rd_en),此時將fifo輸出端(data_fifo_out)數據賦值給RAM寫入端(data_ram_in)。圖中的ram_addr為43時寫入的數據為導頻符號,在這里導頻符號我是通過類似于m序列的擾碼器來進行產生的。

導頻的產生:

需要插入的4個導頻符號分別為1,1,1,-1。OFDM數據中插入的導頻符號并不都是一樣的,需要根據公式對插入的導頻符號的極性進行改變,這里我用的改變導頻符號極性的公式為s(x)=x7+x4+1。

公式的實質是一個擾碼器,首先將擾碼器的初始狀態設置為1111111,根據擾碼器的輸出結果對導頻符號的極性進行修改,若擾碼器的輸出結果為0,則導頻符號的極性不變,若擾碼器的輸出結果為1,則對導頻符號的極性進行修改,修改規則為1 -> -1,-1 -> 1。

圖七為導頻產生數據波形圖,其中data_m為擾碼器序列,初始狀態為1111111,每當需要插入導頻時m_start便會使能置1,根據m_start可以看出圖中一個OFDM符號中共插入四個導頻。p寄存器中便是存放的四個原始導頻數據,01表示導頻1,11表示導頻-1。data_m_out便是最終插入OFDM符號的導頻數據,即寫入ram中的導頻數據。

ifft變換:

在數據都在RAM中存好之后便是將ram中的數據送入IFFT變換的輸入端口,此時將ram的ena使能端置為高電平ram的wea置為低電平,開始讀取ram中的數據。如下圖所示,ram的ena為高,ram的wea為低,ram數據輸出端為douta開始輸出數據。

這里OFDM一次傳輸128個數據,在星座映射后為48個數據,插入四個導頻后為52個數據,這里選擇通過補零來添加冗余,如下圖所示。

在上圖中,ifft_s_data_tdata為ifft變換的輸入端口,ifft_s_data_tvalid為輸入使能,ifft_s_data_tvalid為高時輸入ifft_s_data_tdata的數據才有效。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602043 -

ofdm

+關注

關注

6文章

349瀏覽量

56989 -

接收機

+關注

關注

8文章

1180瀏覽量

53413 -

調制器

+關注

關注

3文章

834瀏覽量

45111

發布評論請先 登錄

相關推薦

一種基于相位調制器的40 GHz OFDM-ROF系統實驗研究

請問FM調制器的FPGA實現

QPSK高性能數字調制器的FPGA實現

QPSK調制器的FPGA實現

電光調制器,電光調制器工作原理是什么?

基于FPGA的QDPSK調制器的設計

FPGA實現OFDM調制器設計

基于FPGA的OFDM系統設計與實現

基于ofdm的調制解調原理,ofdm調制解調fpga代碼

如何使用FPGA設計和實現OFDM系統和OFDM中的FFT模塊設計及其FPGA實現

如何使用FPGA實現QPSK調制器的設計與實現

基于FPGA的OFDM調制器設計

基于FPGA的OFDM調制器設計

評論