隨著游戲產(chǎn)業(yè)和數(shù)據(jù)中心的蓬勃發(fā)展,全球 NAND 市場正呈擴張之勢。而由于新冠疫情的爆發(fā),人們更多選擇遠程辦公和在線課程,對數(shù)據(jù)中心和云服務器的需求隨之增長,市場對 NAND 存儲器的需求也大幅增加。從移動或便攜式固態(tài)硬盤到數(shù)據(jù)中心,從企業(yè)固態(tài)硬盤再到汽車配件, NAND 閃存的應用領(lǐng)域和使用場景愈發(fā)多樣化,各種要求也隨之出現(xiàn),常見的譬如更高的讀寫速度、最大化的存儲容量、更低的功耗和更低的成本等等。為了滿足這些要求,數(shù)據(jù)的存儲方式和堆疊方法也在不停發(fā)展演變。

NAND閃存的數(shù)據(jù)存儲辦法

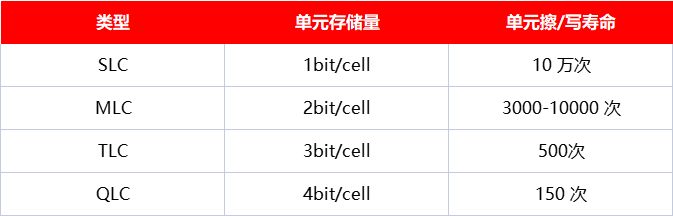

NAND 閃存是一種通過在氮化硅的內(nèi)部補集點捕獲電子或空穴來存儲信息的設(shè)備。在這種設(shè)備中,工作區(qū)和柵極間會留有通道供電流通過硅晶片表面,而根據(jù)浮置柵極中存儲的電荷類型,便可進行存儲編程 (“1”) 和擦除 (“0”) 信息的操作。同時,在一個單元內(nèi)存儲 1 個比特的操作被稱為單層單元 (SLC)。氮化硅內(nèi)部捕獲的電子數(shù)量與單元晶體管的閾值電壓成正比,因此,當俘獲大量電子時,即實現(xiàn)了高閾值電壓;捕獲少量電子會造成低閾值電壓。

通過將捕獲的電子數(shù)量分成三份,并將每份的中間電壓施加到單元柵極上,可以檢查電流的流通狀態(tài),從而確定所捕獲的電子數(shù)量。在這種情況下,存在四種狀態(tài),其中包括擦除狀態(tài):這就是 2 比特多層單元 (2 bit-MLC)。2 比特多層單元的這四種狀態(tài)可以描述為“11”、“10”、“01”和“00”,每個單元可以存儲 2 個比特的信息。從定義而言,多層單元指的是一種狀態(tài),在這種狀態(tài)下,一個單元具有多層的 2 個比特或更多比特;然而在本文中,多層單元是相對于單層單元(SLC,Single Level Cell)而言的。方便起見,本文將存儲 2 個比特信息的多層單元(MLC,Multi Level Cell)稱為 2 比特多層單元。

在相同的方法下,若產(chǎn)生八單元狀態(tài)并存儲 3 個比特的信息時,此類狀態(tài)則被稱為三層單元 (TLC,Triple Level Cell);同樣,當產(chǎn)生十六單元狀態(tài)并存儲 4 個比特的信息時,則稱為四層單元 (QLC, Quadruple Level Cell)。單元狀態(tài)越密集,一個單元內(nèi)便可儲存更多信息。舉例來說,與單層單元(SLC) NAND 閃存相比,四層單元(QLC) NAND 閃存能夠以 67.5% 的芯片尺寸存儲相同數(shù)量的信息;但若想進行更多運行和讀取的操作,就要增大單元狀態(tài)的密度。相應地,由于單元狀態(tài)之間的空間狹窄,更大的密度會使性能降級并出現(xiàn)讀取錯誤的可能性,從而導致設(shè)備壽命縮短。因此,重要的是,首先要根據(jù)NAND閃存的應用領(lǐng)域決定是否優(yōu)先考慮信息量,性能和壽命,然后選擇適當?shù)木幊谭椒ā?/span>

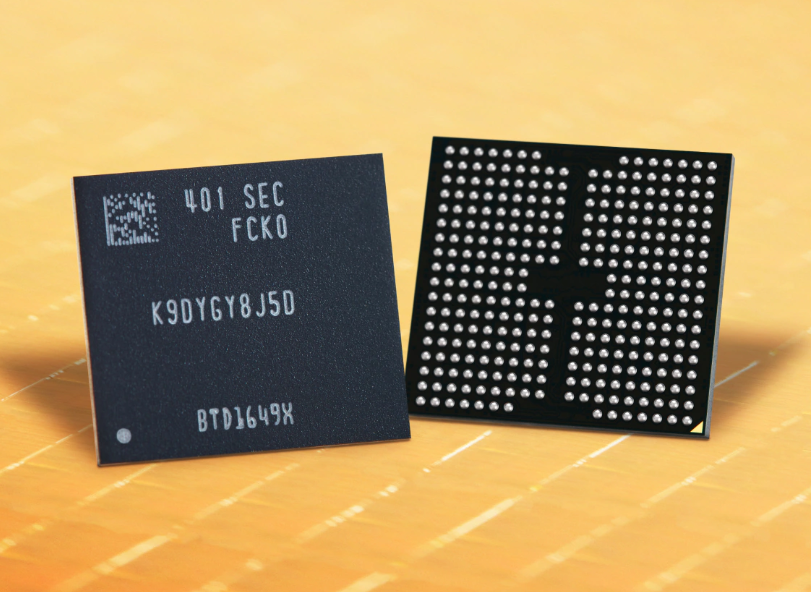

當前,NAND 閃存正在從 2D 發(fā)展到 3D 和 4D。對于 2D-NAND,如果在同一區(qū)域?qū)崿F(xiàn)更多的單元數(shù)量,形成更小的工作區(qū)和柵級,便能增大存儲容量。直至 2010 年初,2D-NAND 中的擴展一直是這項技術(shù)的主要焦點所在;然而,由于精細圖案結(jié)構(gòu)的限制,且儲存數(shù)據(jù)會隨時間推移而丟失導致使用壽命縮短,該技術(shù)已無法再實現(xiàn)擴展。因此,3D-NAND逐漸取而代之,成為業(yè)界關(guān)注焦點,現(xiàn)在所有 NAND 制造商都在開發(fā)和制造 3D-NAND 產(chǎn)品。

在 3D-NAND 的結(jié)構(gòu)中,存儲容量會隨著三維疊層中堆疊層數(shù)的增加而變大。3D-NAND 使用了堆疊多層氮氧化物的方法,形成一個被稱為“塞子”的垂直深孔,在其中形成一個由氧化物-氮化物-氧化物制成的存儲設(shè)備。通過這種方法,僅需少量工藝即可同時形成大量單元。在 3D-NAND 中,電流通過位于圓柱單元中心的多晶硅通道,便能根據(jù)存儲在氮化硅中的電荷類型實現(xiàn)存儲編程和擦除信息。雖然2D-NAND 技術(shù)發(fā)展的目標是實現(xiàn)形成較小的單元, 3D-NAND 的核心技術(shù)卻是實現(xiàn)更多層數(shù)的三維堆疊。

為在 3D-NAND 的基礎(chǔ)上進一步增大存儲容量,4D-NAND技術(shù)也隨之而來。經(jīng)過幾代技術(shù)的發(fā)展,當前的半導體行業(yè)已實現(xiàn)了用更多層數(shù)存儲更多信息,目前最高層為238層,存儲企業(yè)也正在研發(fā)更多層的產(chǎn)品。

往期存儲知識回顧:

芯科普 | 一文讀懂存儲主流配置LPDDR

芯科普 | 一文讀懂存儲主流配置DDR

芯科普 | 一文了解存儲主流配置eMCP

存儲主流配置之DRAM篇

存儲主流配置之eMMC篇

原文標題:芯科普 | 一文了解 NAND 閃存技術(shù)的發(fā)展演變

文章出處:【微信公眾號:KOWIN康盈半導體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

存儲

+關(guān)注

關(guān)注

13文章

4262瀏覽量

85669

發(fā)布評論請先 登錄

相關(guān)推薦

一文帶你了解什么是SD NAND存儲芯片

一文帶你了解什么是SD NAND存儲芯片

NAND閃存的發(fā)展歷程

NAND閃存和NOR閃存有什么區(qū)別

SK海力士加速NAND研發(fā),400+層閃存量產(chǎn)在即

科普 | 一文了解FPGA

鎧俠NAND閃存生產(chǎn)恢復

3D NAND閃存來到290層,400層+不遠了

SK海力士推出新一代移動端NAND閃存解決方案ZUFS 4.0

一文解析NAND的閃存接口ONFI

昂科燒錄器支持XinCun芯存科技的串行外設(shè)接口NAND閃存 XCSP4AAPK-IT

芯科普 | 一文了解 NAND 閃存技術(shù)的發(fā)展演變

芯科普 | 一文了解 NAND 閃存技術(shù)的發(fā)展演變

評論