點擊上方藍字關注我們

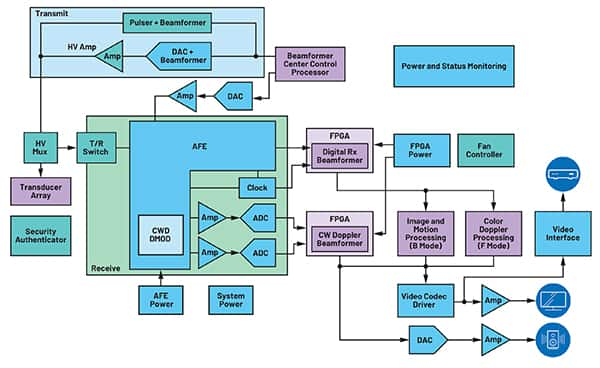

醫學超聲診斷成像技術大多數采用超聲脈沖回波法,即利用探頭產生超聲波進入人體,由人體組織反射產生的回波經換能器接收后轉換為電信號,經過提取、放大、處理,再由數字掃描變換器轉換為標準視頻信號, 由顯示器進行顯示。在基于FPGA+ARM 9硬件平臺的全數字化B超診斷儀中,前端探頭返回的回波電信號需由實時采集系統進行波束合成、相關處理、采集并傳輸至ARM嵌入式處理系統,視頻信號數據量大,實時性要求高,因此選用FPGA+SRAM構成實時采集系統,在速度和容量上都能滿足上述要求。主要介紹B超成像系統中應用FPGA進行邏輯控制進行超聲視頻圖像采集的原理和實現。

2 系統構成工作原理

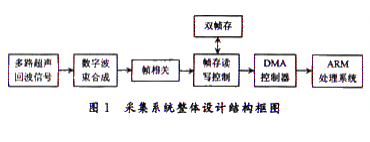

如圖1所示,采集系統首先由數字波束合成器對多通道超聲回波信號進行波束合成,數字波束合成器對不同通道信號進行延時,使同一點的信號同相相加,同時對多個通道的回波信號進行空間域上的加窗,類似匹配濾波,可以提高信號的信噪比。然后對合成后的超聲視頻信號做一個幀相關的預處理,即圖像幀與幀之間對應象素灰度上的平滑處理。因為疊加在圖像上的噪聲是非相關且具有零均值的隨機噪聲,如果在相同條件下取若干幀的平均值來代替原圖,則可減弱噪聲強度。在幀相關過程中,FPGA要控制數據的讀取、處理以及存儲。在為了滿足視頻顯示的實時性,該采集系統采用雙幀存結構的乒乓機制,由FPGA實現讀寫互鎖控制。經幀相關處理完后的視頻數據交替寫入幀存A和幀存B,幀存讀控制器根據后端處理速度讀取幀存中的數據,送往DMA控制器,DMA控制器開啟DMA通道進行數據傳輸。FPGA實現讀寫控制時,為了避免同時對一個幀存進行讀寫操作,需要設置讀寫互斥鎖進行存儲器狀態切換。

3 系統設計與實現

3.1 數字波束合成

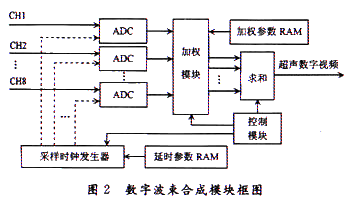

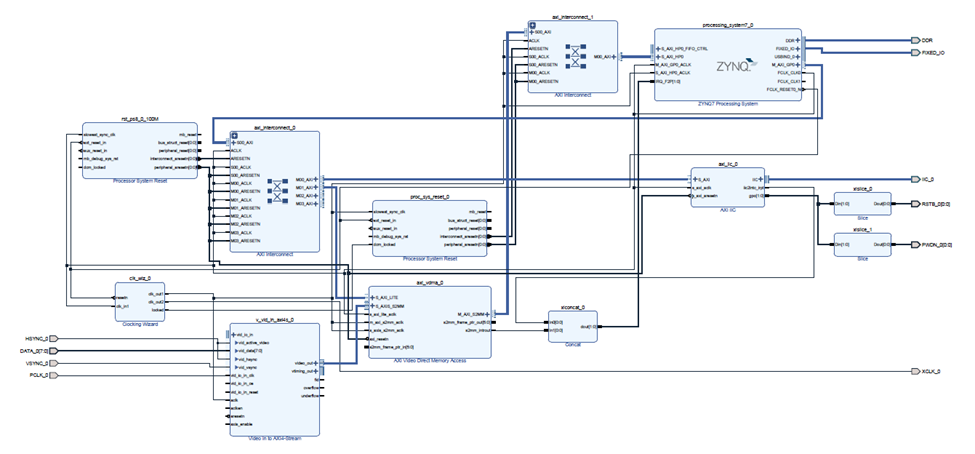

對于具有128陣元和32收發通道的超聲探頭,在進行32路AD轉換后,將其分為4組,每組8路接收通道,每組用一片FPGA實現,在該FPGA內首先進行接收延時和動態聚焦再進行加權求和,其后再進行組間的求和產生超聲數字視頻信號。每一組的系統框圖如圖2所示:

對不同通道的回波信號進行不同的延時是達到波束聚焦的關鍵,延時按 可分為粗延時和細延時:粗延時用于控制A/D采樣的開始時間, 為32 ns,延時參數由FPGA的片內RAM中讀出,更換探頭時系統控制器將相應數據寫入這些RAM;細延時由采樣時鐘發生器根據不同的通道產生不同的A/D采樣時鐘,這些時鐘的相位互相錯開,其錯開的值剛好等于各陣元傳播延遲之差。考慮到系統的實時性以及探測過程中深度的變化,需要采用動態聚焦。動態聚焦是在A/D采樣開始后,通過讀取動態聚焦參數,在采樣的過程中控制采樣時鐘發生器實現。

8個通道的回波信號經過A/D采樣后,送入FPGA,緩沖之后同步讀出進入加權模塊,加權模塊由8個無符號為數字乘法器組成。回波信號分別與加權參數相乘后得到具有動態聚焦和加權特性的數據。8組數據再經過3級加法器就得到波束合成之后的超聲數字視頻數據。

3.2 幀相關處理

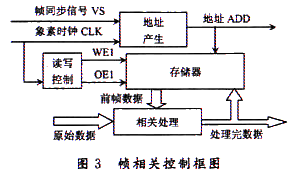

幀相關模塊如圖3所示,由幀相關控制器和一片存儲器組成,進行幀相關的存儲器采用大小為256 kB的靜態存儲器(SRAM)。幀相關控制器由FPGA實現,完成地址產生、存儲器讀寫控制、幀相關計算功能,因為實時性的要求,即保證送往后端雙幀存的數據不能中斷,所以考慮到對逐個象素數據讀寫的同時就進行相關處理,而且需要在同一個象素時鐘周期內完成。讀寫控制器在1個象素時鐘周期的前半段需要讀出存儲器中的數據和當前幀數據進行相關處理;時鐘周期的后半段再將相關處理完的數據寫入存儲器以備后用,這樣送往后端雙幀存的數據依然是和象素時鐘對應的連續象素數據。

幀相關的工作流程如下:

(1)地址產生。地址的產生由一個象索計數器實現,輸入信號為幀同步信號VS和象素時鐘CLK。前端提供的幀同步信號VS為該計數器的復位信號,在每一幀的開始,計數器清零,然后根據象素時鐘CLK計數生成地址,每個象素時鐘周期內地址不變,依據此地址進行存儲器的讀寫。

(2)讀取已有數據及相關處理。在一個象素時鐘周期的前半段,也就是CLK跳變為高電平時,讀寫控制器輸出的讀信號OEl為有效,讀出前幀中一個象素的數據,送到FPGA內部實現的加法器的A口,與同時到達B口的當前幀的對應象素數據相加平均。

(3)數據保存及傳輸。在同一個象素時鐘周期的后半段,也就是CLK跳變為低電平時,讀寫控制器輸出的寫信號WEl為有效,相關處理完的數據寫回原來的地址,同時該數據也送往幀存寫控制模塊。

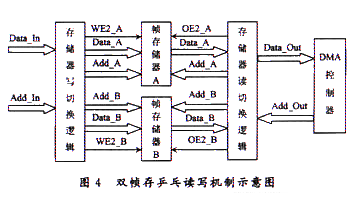

3.3 幀存乒乓讀寫控制機制

超聲視頻圖像需要實時地采集并在處理后在顯示器上重建,圖像存儲器就必須不斷地寫入數據,同時又要不斷地從存儲器讀出數據送往后端處理和顯示。另外,為了滿足這種要求,可以在采集系統中設置2片容量一樣的幀存,通過乒乓讀寫機制來管理,結構如圖3所示。為了確保任何時刻,只能有1片幀存處于寫狀態,設置1個寫互斥鎖;同時,只能有1片幀存處于讀狀態,設置一個讀互斥鎖。在系統初始時,1片幀存為等待寫狀態,另1片為等待讀狀態;開始工作后,2片都處于讀寫狀態輪流轉換的過程,轉換的過程相同,但是2片狀態相錯開,這樣就能夠保證數據能連續地寫入和讀出幀存。該機制如圖4所示,工作流程為:

(1)采集過程未開始,幀存A為等待寫狀態,獲得寫互斥鎖;幀存B為等待讀狀態,獲得讀互斥鎖;

(2)幀存寫控制器收到一幀開始信號,判斷為采集開始,設置幀存A寫信號WE2 A有效,幀存A開始寫入當前幀數據;同時幀存讀控制器設置幀存B讀信號OE2_B有效,幀存B則開始讀出所存數據;

(3)一幀結束,幀存A寫結束,釋放寫互斥鎖;幀存B讀結束,釋放讀讀斥鎖;

(4)等待另一幀開始,幀存A獲得讀互斥鎖;幀存B獲得寫讀斥鎖;

(5)另一幀開始,寫控制器設置幀存B寫信號WE2B有效,幀存B開始寫入數據;讀控制器設置幀存A讀信號OE2 A有效,幀存A則開始讀出數據。

3.4 DMA傳輸

對整個B超診斷儀來說,系統要完成視頻圖像數據的實時采集和指定的處理,高性能ARM處理器的處理能力可達每秒數百萬條指令,因此數據的傳輸設計是提高系統速度的關鍵環節。ARM處理系統與外部的數據傳輸可以通過CPU訪問外部存儲器的方法實現,但是效率低下,不能滿足系統實時性的要求,而DMA數據傳輸以不占用CPU時間和單周期吞吐率進行數據傳輸的優點在實時視頻圖像采集系統中得到廣泛的應用。但是因為DMA的傳輸速率和前端視頻圖像數據的輸入速率不匹配,很難發揮出DMA數據傳輸的優勢。由可編程的FPGA控制SRAM組成的雙幀存可以很好地解決這個問題;此外,FPGA內部嵌入了一定數量的RAM,可以經過配置成緩沖存儲器,通過靈活的邏輯結構可以方便地實現對輸入輸出數據流的控制,成為連接ARM處理系統和SRAM的紐帶和橋梁。

4 結 語

在B超數字視頻圖像實時采集系統中采用FPGA作為采集控制部分,首先可以提高系統處理的速度及系統的靈活性和適應性:由于在FPGA和ARM處理系統之間采用SRAM做數據緩沖,并用DMA方式進行傳輸,大大提高系統的性能;由于采用FPGA可編程邏輯器件,對于不同的超聲視頻信號,只要在FPGA內對控制邏輯稍做修改,便可實現信號采集;FPGA的外圍硬件電路簡單,因而在硬件設計中,可以大大減小硬件設計的復雜程度。而FPGA的時序邏輯調試可在軟件上仿真實現,因而降低硬件調試難度。

有你想看的精彩 至芯科技-FPGA就業培訓來襲!你的選擇開啟你的高薪之路!7月12號北京中心開課、歡迎咨詢! 薦讀:Altera OpenCL 入門 基于FPGA的千兆以太網ARP和UDP的實現

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于FPGA+SRAM實現超聲視頻圖像采集系統的設計

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601886

原文標題:基于FPGA+SRAM實現超聲視頻圖像采集系統的設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA在圖像處理領域的優勢有哪些?

基于VDMA的遠程圖像采集系統參考設計

基于RK3588J的6路MIPI CSI視頻采集案例分享,多路視頻系統必看!

基于FPGA的圖像采集與顯示系統設計

基于FPGA的實時邊緣檢測系統設計,Sobel圖像邊緣檢測,FPGA圖像處理

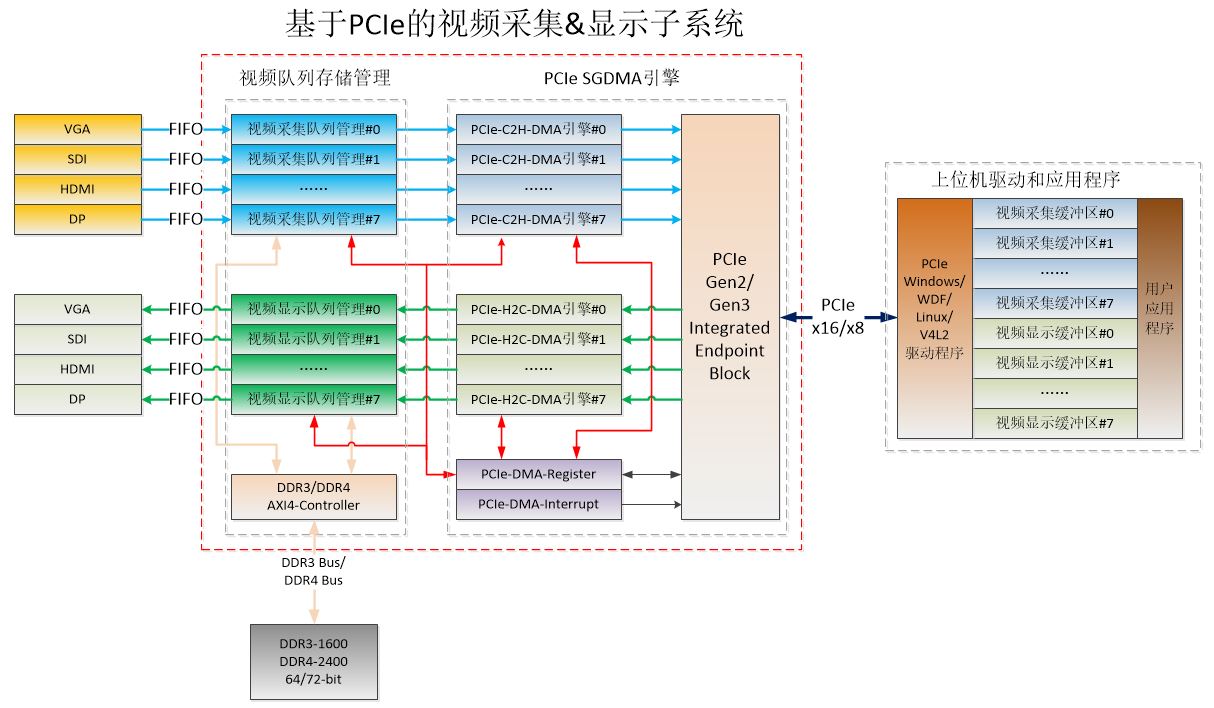

V4L2視頻采集,基于PCIe的多路視頻采集與顯示子系統

如何使用超低噪聲電源提高超聲系統的圖像質量

基于FPGA+SRAM實現超聲視頻圖像采集系統的設計

基于FPGA+SRAM實現超聲視頻圖像采集系統的設計

評論